ZHCA964A September 2019 – July 2020 TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384S , TMS320F28386D , TMS320F28386S , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

4.3.3 ControlCard、LaunchPad 波形

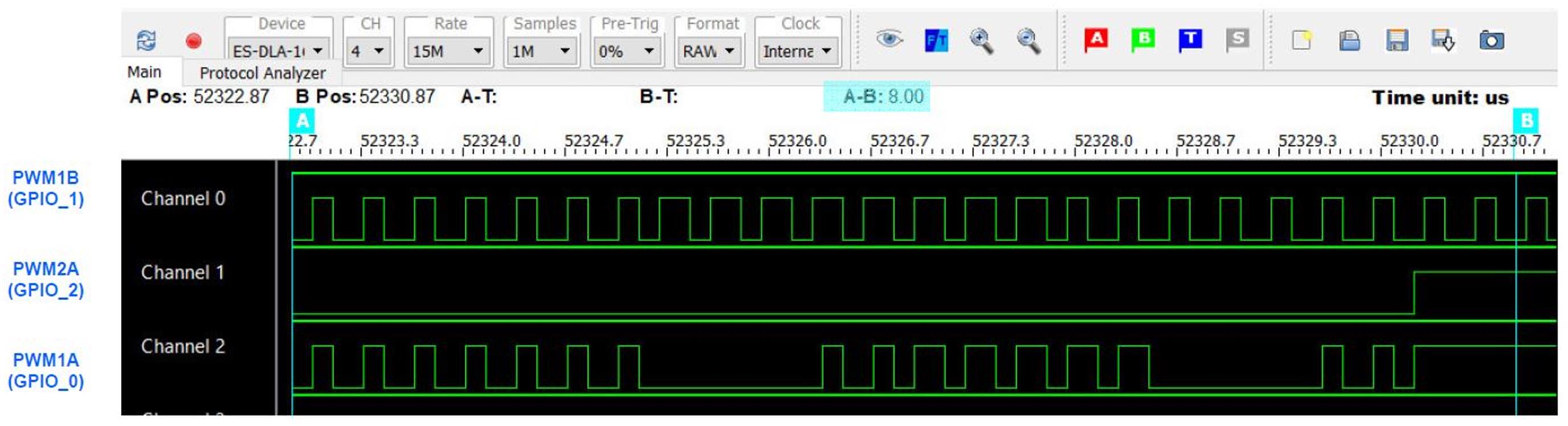

仿真确认在 C2000 CLB 内部实现的自定义逻辑与原始 FPGA 实现的逻辑相匹配之后,就该使用实际的 C2000 硬件来验证结果了。图 4-11 包含连接到 F28004x ControlCard 的 GPIO_0、GPIO_1 和 GPIO_2 的逻辑分析仪的屏幕截图(还使用 F28004x LaunchPad 捕获了相同的波形)。GPIO_0 表示 CLB 输出,该输出已按照配置逻辑块 1 的外设信号多路复用器的功能调用的指示替换了原始 PWM1A 输出。虽然原始的 PWM1A 信号已被 CLB1 输出替换,但相同的功能调用指定 CLB1 的其他 7 个输出不替换其对应的内部控制外设信号,因此可以在 GPIO_1 引脚上看到原始 PWM1B 输出,可以在 GPIO_2 上看到原始 PWM2A 输出。

这样就完成了示例 16 中所述的自定义逻辑从外部 FPGA 到 C2000 的转移。结果证实,可以将复杂的功能(如 PWM 发生器和自定义胶合逻辑)从外部可编程逻辑器件转移到 C2000 微控制器中,并且结果完全相同。该功能通过实现自定义逻辑以外部可编程逻辑器件无法实现的方式来访问 C2000 CPU 和外设的内部信号,从而降低了总系统成本,同时增强了功能。

图 4-11 CLB 示例 16 – C2000 LaunchPad/ControlCard 波形

图 4-11 CLB 示例 16 – C2000 LaunchPad/ControlCard 波形