ZHDA023 January 2026 TPSM33620-Q1

3.2 缓冲器电路

减少降压转换器中高 dv/dt 的 EMI 辐射的一种常见方法是减缓 SW 节点的速度。通过减慢 SW 节点,器件寄生电容产生的电压峰值不那么明显,从而减少了相关的辐射电场。对于许多器件,这是通过与自举电容器串联的电阻器来实现的。但是,TPSM33620-Q1 具有集成式自举电容器,因此无法访问自举电容器。此外,添加与引导电容器串联的电阻会导致器件产生更多热量,因为这会强制高侧 FET 导通更长时间。在只能访问 SW 的情况下,缓冲器电路是 TPSM33620-Q1 上降低 dv/dt 速度的唯一方法。

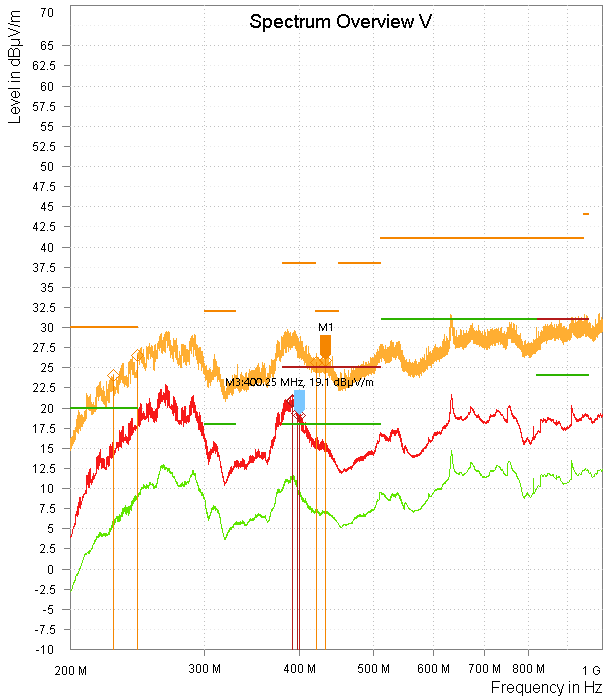

图 3-2 展示了 TPSM33620-Q1 的开关节点。与任何高 dv/dt 环路一样,在高频范围内都存在过冲和下冲。这些电压尖峰会在这些频率范围内产生相关 EMI 峰值。测量 dv/dt 峰值的频率可得到 400MHz 到 500MHz 范围内的频率,这与图 3-3 和图 3-4 中的 EMI 尖峰相匹配。由于存在这种噪声的开关节点,TPSM33620-Q1 在 400MHz 到 500MHz 频率范围内会错过 EMC 的几个 dB。

图 3-2 TPSM33620-Q1 开关节点上升沿纹波

图 3-2 TPSM33620-Q1 开关节点上升沿纹波 图 3-3 TPSM33620-Q1 不带缓冲器、水平极化、12VIN、3.3VOUT、2A 时的辐射 EMI

图 3-3 TPSM33620-Q1 不带缓冲器、水平极化、12VIN、3.3VOUT、2A 时的辐射 EMI 图 3-4 TPSM33620-Q1 不带缓冲器、垂直极化、12VIN、3.3VOUT、2A 时的辐射 EMI

图 3-4 TPSM33620-Q1 不带缓冲器、垂直极化、12VIN、3.3VOUT、2A 时的辐射 EMI为了解决这些发射问题,通过抑制该节点中的寄生电感来“缓冲”高频 dv/dt。缓冲电路从开关节点吸取能量,从而降低对 EMI 的影响。本技术文章可以用于计算有效抑制开关节点所需的 RC 常数。值得注意的是,通过减小电阻并增加缓冲器的电容,可以增加衰减的能量。对于 TPSM33620-Q1,缓冲电阻器降低至 1Ω,缓冲电容器增加至 1000pF 以进行补偿。图 3-5 显示了开关节点中更低的 dv/dt 尖峰。因此,图 3-6 和图 3-7 显示了在开关振铃产生噪声的高频区域的改进。虽然可有效降低 EMI,但缓冲器电路会耗散更多能量,从而降低应用的效率。借助此缓冲器电路,TPSM33620-Q1 在 2A 负载下的功耗可增加 30mW。

图 3-5 TPSM33620-Q1 带缓冲器的开关节点上升沿纹波

图 3-5 TPSM33620-Q1 带缓冲器的开关节点上升沿纹波 图 3-6 TPSM33620-Q1 带缓冲器电路、水平极化、12VIN、3.3VOUT、2A 时的辐射 EMI

图 3-6 TPSM33620-Q1 带缓冲器电路、水平极化、12VIN、3.3VOUT、2A 时的辐射 EMI 图 3-7 TPSM33620-Q1 带缓冲器电路、垂直极化、12VIN、3.3VOUT、2A 时的辐射 EMI

图 3-7 TPSM33620-Q1 带缓冲器电路、垂直极化、12VIN、3.3VOUT、2A 时的辐射 EMI