ZHCU827A July 2019 – March 2021

5 电路板布局

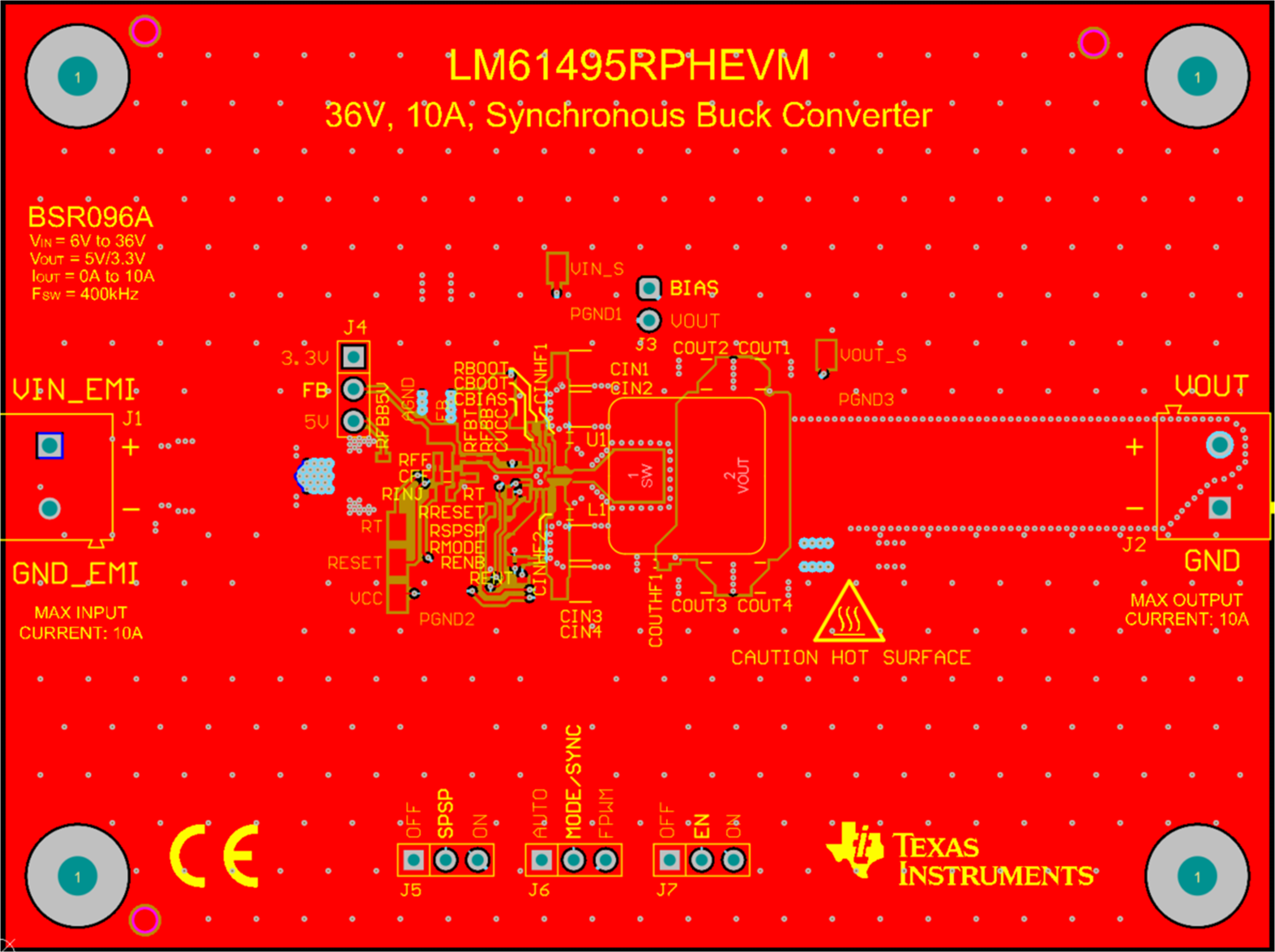

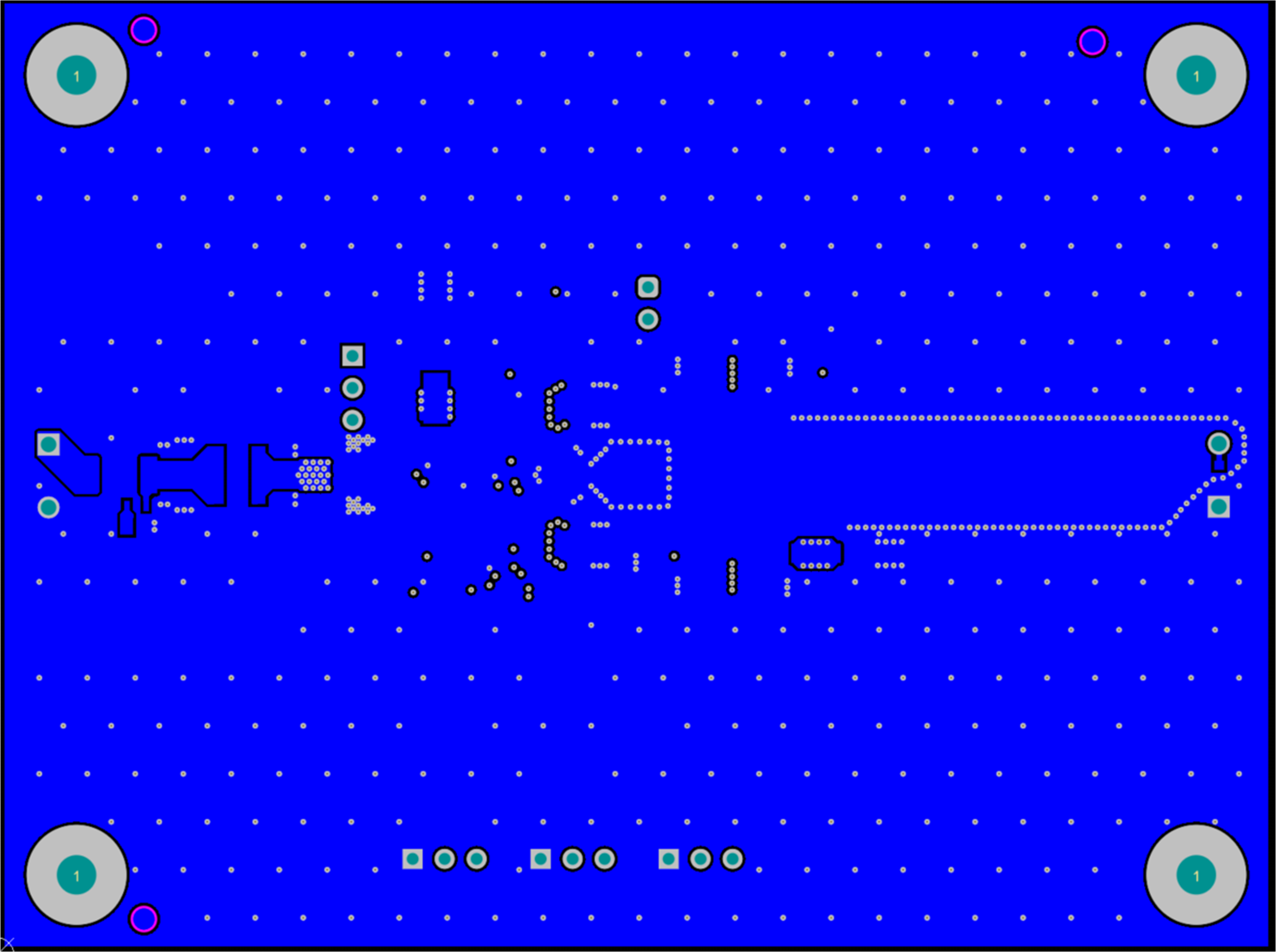

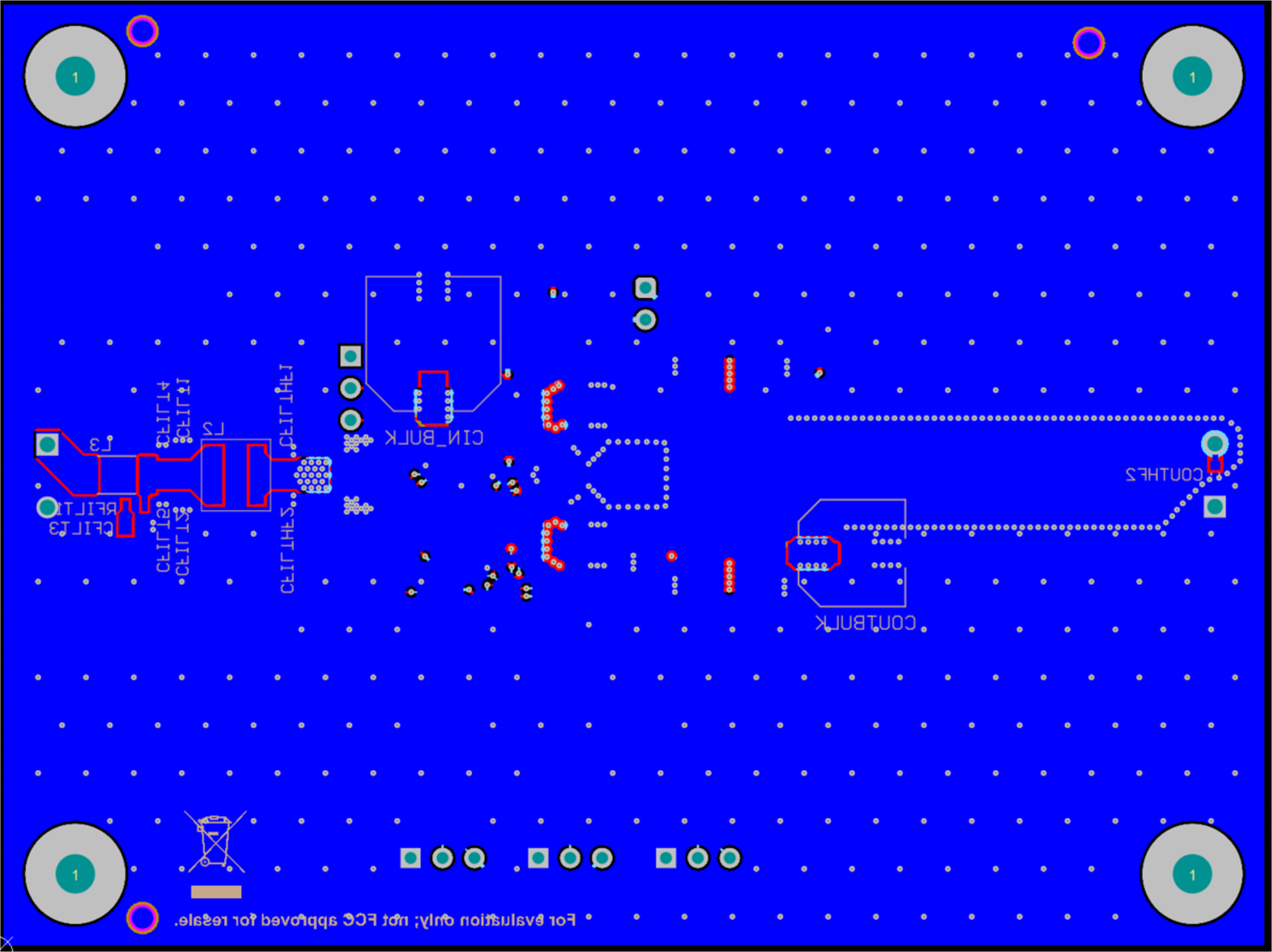

图 5-1 至图 5-6 显示了 LM61495RPHEVM 的电路板布局。EVM 提供电阻、电容器和跳线来配置输出电压和精密使能引脚并设置频率和外部时钟同步等 LM61495-Q1 功能。

PCB 针对热性能进行了优化。电路板包含 4 层。顶层和底层有 2oz 铜,中间两层有 1oz 铜。LM61495-Q1 没有散热焊盘,所以 IC 散热的最好途径是通过引脚接入电路板。PGND 引脚连接到大 GND 平面,后者将热量散播到电路板的剩余部分。GND 平板还有散热过孔,将热量更高效地散播到其他层,以进一步改善热性能。

PCB 还针对 EMI 性能进行了优化。这种布局最大限度地减少了 SW 和 BOOT 之类的高 dv/dt 节点的面积。小型高频陶瓷输入电容器放在非常靠近 IC 的位置,以最大限度地缩短 VIN 引脚通过电容器到 PGND 引脚所形成的环路。电路板背面还有 EMI 滤波器以及电感器、铁氧体磁珠和滤波电容器选项,以调整所需的 EMI 性能。整个滤波器不一定能达到特定的 EMI 要求,但组件和焊盘可灵活调整。

螺纹接线端子 J1 和 J2 允许高电流接入电路板。跳线 J3 将 VOUT 连接到 BIAS 以提高轻负载效率。跳线 J4 允许用户选择输出电压 5V 或 3.3V。J5 允许用户打开或关闭展频。J6 允许用户在 AUTO 模式(轻负载下进行脉冲频率调制)或 FPWM(强制脉宽调制)下运行器件。J6 上的 MODE/SYNC 引脚还可以作为 SYNC 引脚在需要时同步到外部时钟。J7 使用户能够启用或禁用 IC。

图 5-1 顶层和顶部丝网

图 5-1 顶层和顶部丝网 图 5-2 顶层布线

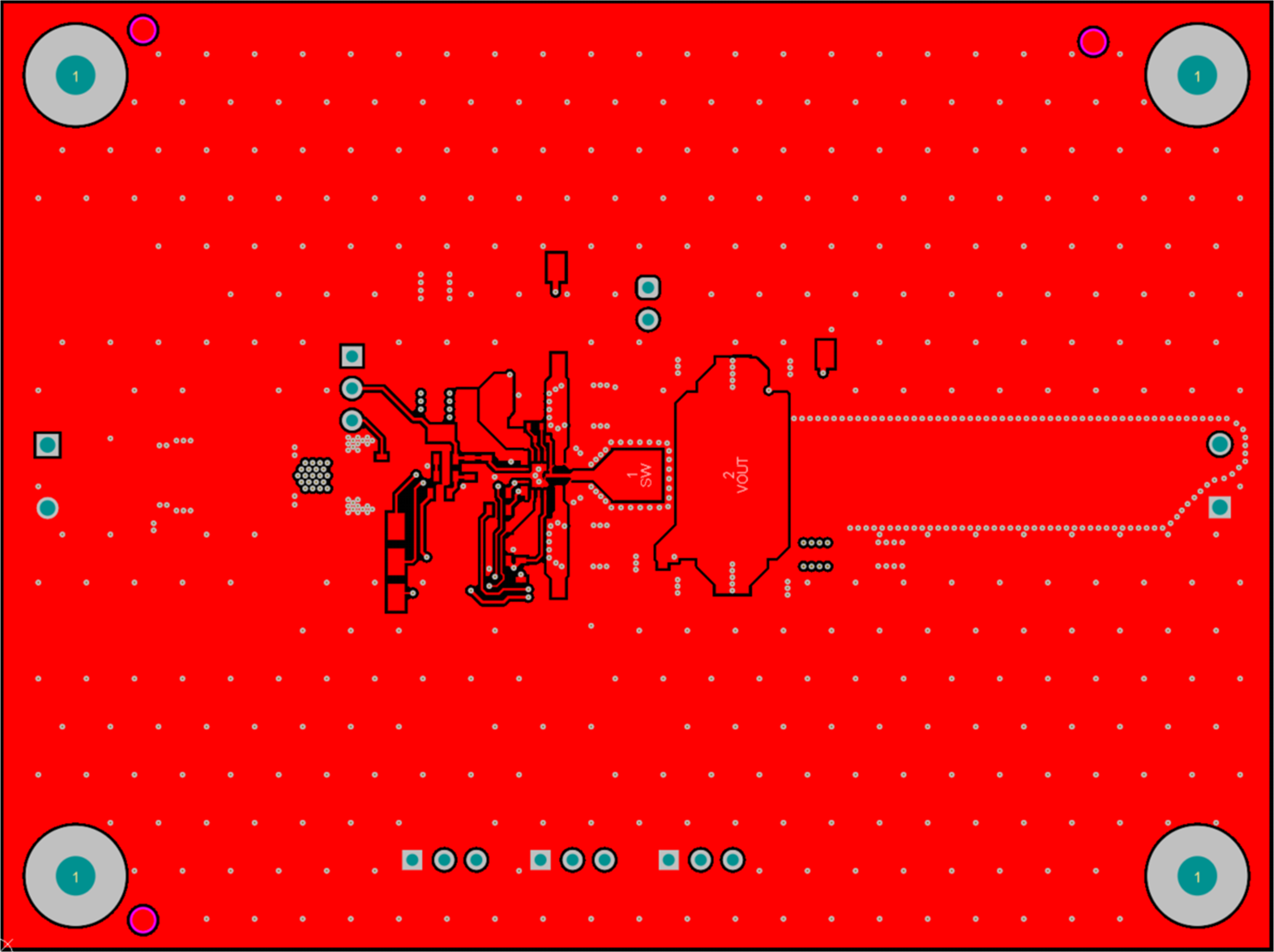

图 5-2 顶层布线 图 5-3 中层 1 接地平面

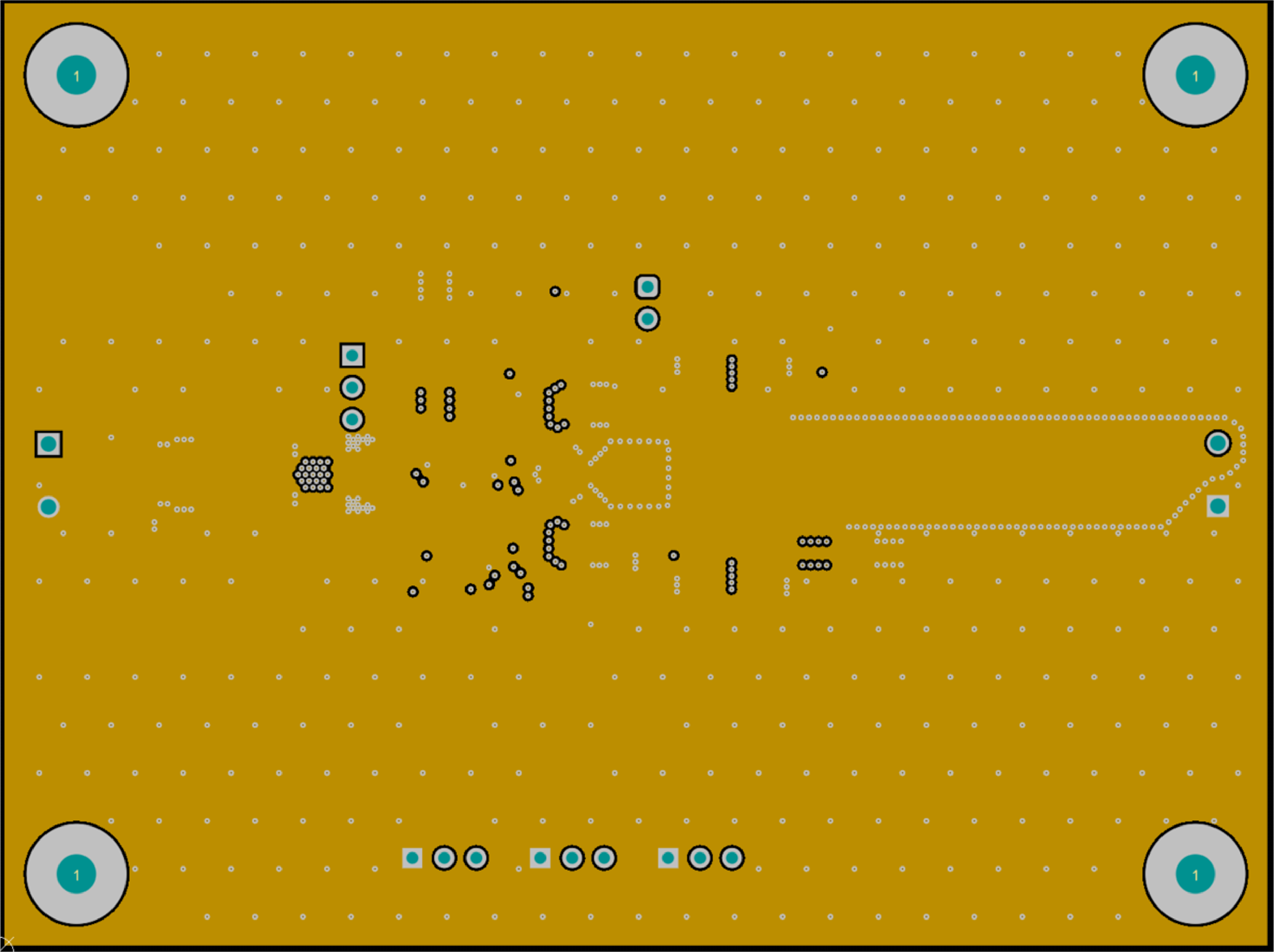

图 5-3 中层 1 接地平面 图 5-4 中层 2 布线

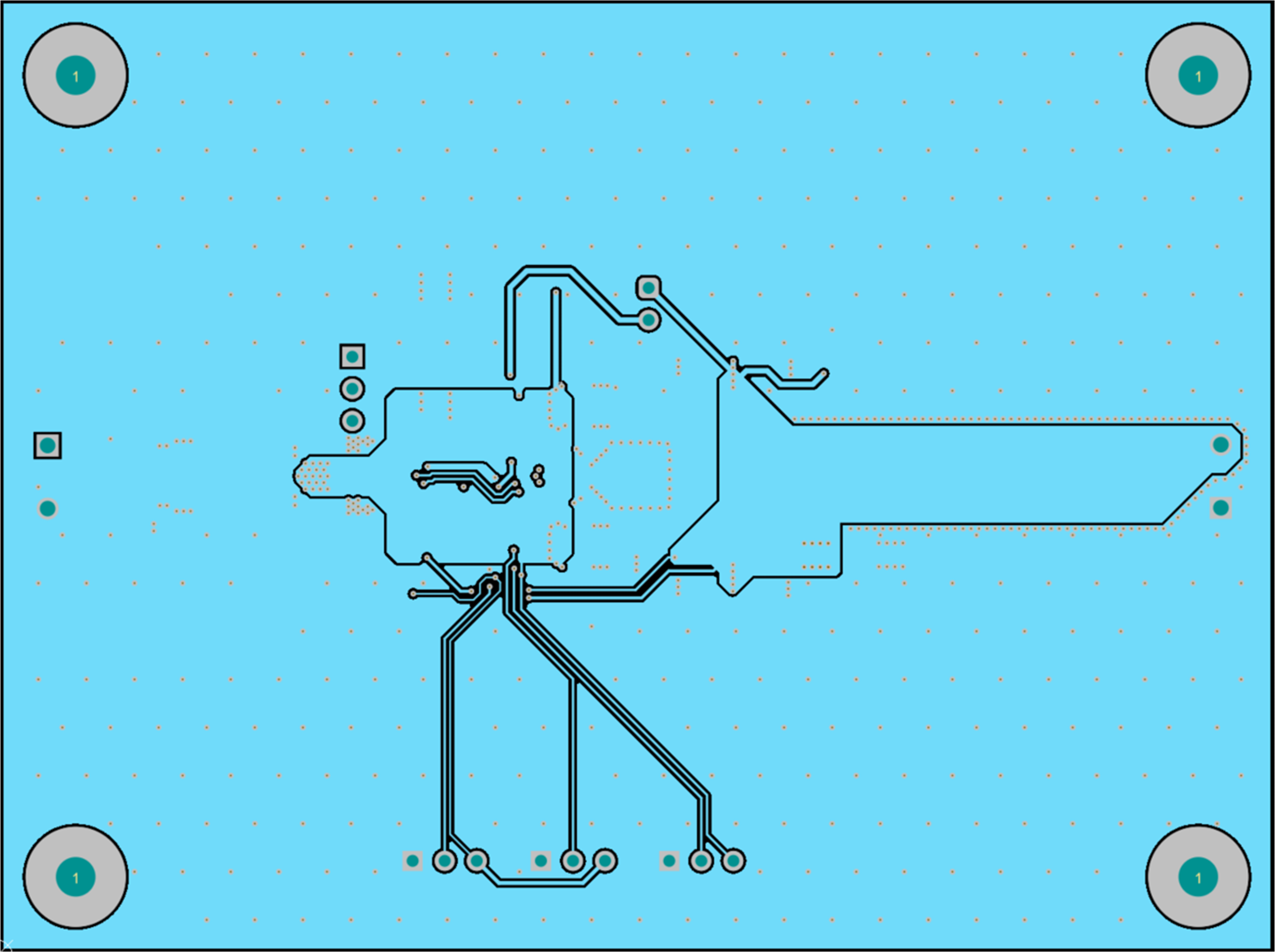

图 5-4 中层 2 布线 图 5-5 底层布线

图 5-5 底层布线 图 5-6 底层和底部丝网

图 5-6 底层和底部丝网