ZHCT360 January 2022 AFE0064 , AFE1256 , AFE2256 , AFE3256 , DDC112 , DDC114 , DDC118 , DDC232 , DDC264 , DDC316

3 X 射线 AFE ROIC

AFE 系列读出集成电路 (ROIC) 包含三个器件:AFE0064、AFE1256 和 AFE2256。

TI 最初设计的 AFE 器件用于测量薄膜晶体管平板探测器中由像素阵列(光电二极管)收集的电荷。鉴于此应用中信号的性质,这些器件针对更宽的输入带宽和远低于 20µs 的更短积分时间(采样周期)进行了优化。相反,器件设计中的积分时间不超过几毫秒。

最大电荷设置(满量程)通常低于 DDC 系列,大约为 10pC。但它们面向的是较低的信号,因此灵敏度/本底噪声也优于 DDC,典型值约为 0.1fCrms(600 个电子)。对于小电荷范围,AFE 的噪声不到 DDC 的一半。

该器件的动态范围更小(本底噪声更低,但满量程更低),不需要使用 DDC 器件所需的 20+ 位转换器,因此,AFE 器件仅支持 16 位转换。

除了提高灵敏度之外,AFE 器件相比 DDC 的一个优点是,它可以处理流入或流出器件输入端的电流,而无需外部组件,甚至可以采集双极性信号。

AFE 的输入电压不是零,而是不同的电压电平(例如,AFE0064 的输入电压为 1.68V,具体取决于所选器件)。偏置传感器时必须考虑电压电平。例如,若要在试图使暗电流接近零的同时读取光电二极管,通常会使用零偏置电压(光电二极管上不施加偏置电压)。因此,如果光电二极管的一个端子连接到 AFE 输入,则另一端子应偏置到相同的非零电压。

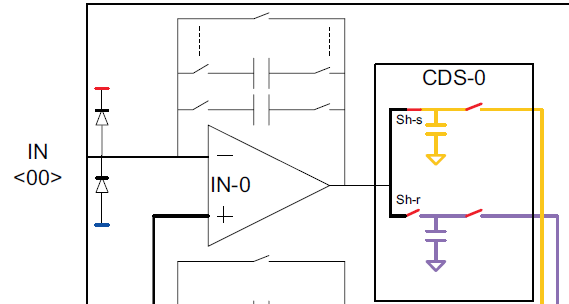

为了进一步解释每个通道的架构(参见图 3-1),每个样本实际上分为两个由外部信号控制的阶段:一个复位/偏移采样阶段和一个信号采样阶段。这些是相关双采样器 (CDS) 的典型阶段。在面板应用中,在复位/偏移阶段,器件的输入端连接到外部(通常采用数据线),但不存在信号。目的是对来自外部或内部源的任何现有偏移或低频噪声(闪烁)进行采样或基线化。一半的 CDS 用于存储生成的积分。在信号采样阶段,外部信号连接到输入,CDS 的另一半用于存储该积分。在此期间,偏移源仍将存在;减去 CDS 中的两个样本将消除偏移,只留下感兴趣的信号。

图 3-1 X 射线 AFE 输入积分器架构

图 3-1 X 射线 AFE 输入积分器架构当将这种方案应用于连续电流的采样时,在复位阶段还将对一部分信号进行积分,电路稍后将从信号采样阶段获得的积分中减去该部分信号。如果信号在这两个阶段中是恒定的,则效果是易于纠正的增益误差。但如果信号发生变化,应该考虑潜在的诱导误差。

如果可以使信号生成与 CDS 采样操作同步,则不会出现增益误差。例如,如果可以在进行 CDS 操作的同时打开和关闭传感器照明,则光电二极管电流将仅在信号采样阶段产生,而不是在复位/偏移阶段产生。结果将不会出现增益误差,并具有额外的优势,即任何环境光或偏移都将在复位/偏移阶段被采样并被 CDS 拒绝。

AFE0064 采用更传统的 Thin Quad Flat Package (TQFP),而较新的版本则采用 Chip-on-Flex (COF) 封装,具体取决于平板探测器应用。与更常见的组装方法相比,这可能会带来一些复杂性。