ZHCSGI8A April 2017 – October 2021 ADC12D1620QML-SP

PRODUCTION DATA

- 1 特性

- 2 应用

- 3 说明

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 Converter Electrical Characteristics: Static Converter Characteristics

- 6.6 Converter Electrical Characteristics: Dynamic Converter Characteristics

- 6.7 Converter Electrical Characteristics: Analog Input/Output and Reference Characteristics

- 6.8 Converter Electrical Characteristic: Channel-to-Channel Characteristics

- 6.9 Converter Electrical Characteristics: LVDS CLK Input Characteristics

- 6.10 Electrical Characteristics: AutoSync Feature

- 6.11 Converter Electrical Characteristics: Digital Control and Output Pin Characteristics

- 6.12 Converter Electrical Characteristics: Power Supply Characteristics

- 6.13 Converter Electrical Characteristics: AC Electrical Characteristics

- 6.14 Electrical Characteristics: Delta Parameters

- 6.15 Timing Requirements: Serial Port Interface

- 6.16 Timing Requirements: Calibration

- 6.17 Quality Conformance Inspection

- 6.18 Timing Diagrams

- 6.19 Typical Characteristics

-

7 Detailed Description

- 7.1 Overview

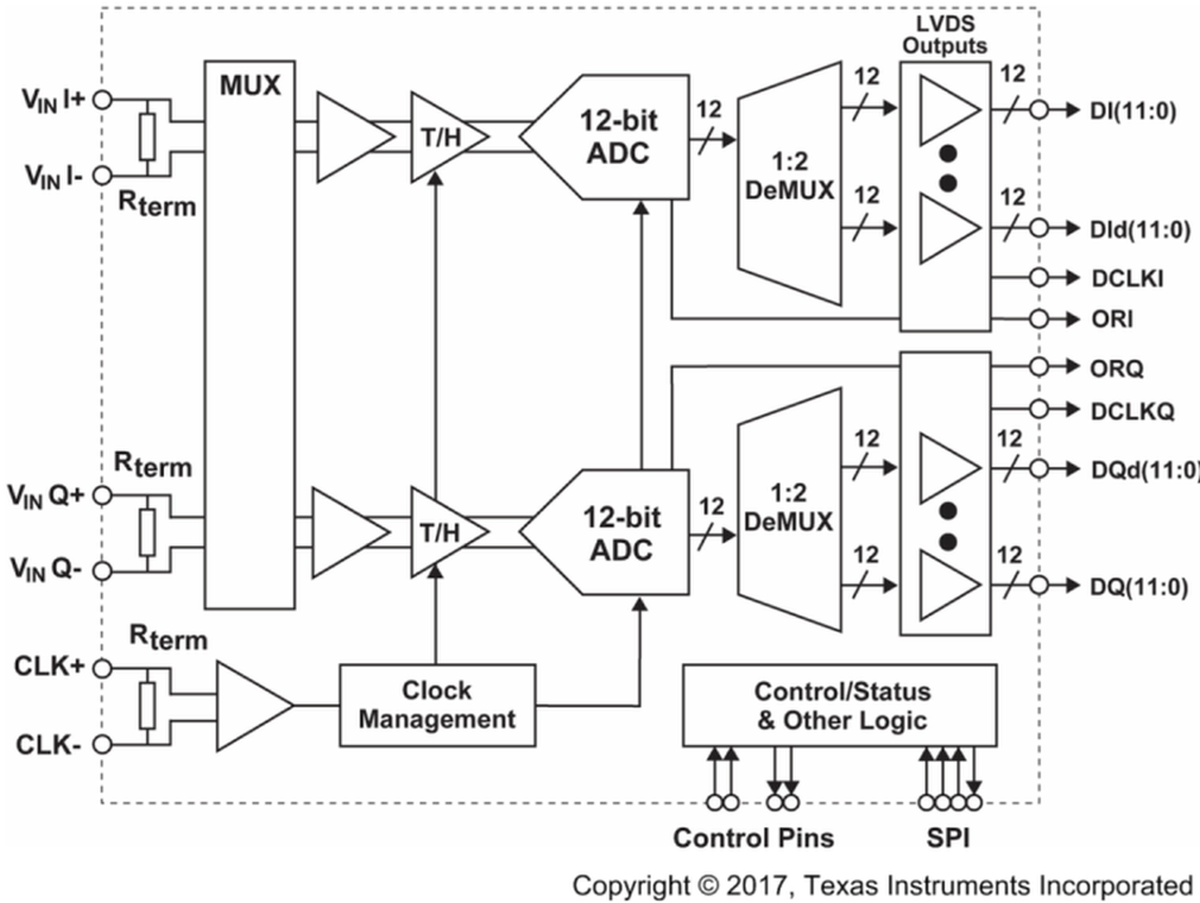

- 7.2 Functional Block Diagram

- 7.3 Feature Description

- 7.4 Device Functional Modes

- 7.5

Programming

- 7.5.1

Control Modes

- 7.5.1.1

Non-ECM

- 7.5.1.1.1 Dual-Edge Sampling Pin (DES)

- 7.5.1.1.2 Non-Demultiplexed Mode Pin (NDM)

- 7.5.1.1.3 Dual Data-Rate Phase Pin (DDRPh)

- 7.5.1.1.4 Calibration Pin (CAL)

- 7.5.1.1.5 Low-Sampling Power-Saving Mode Pin (LSPSM)

- 7.5.1.1.6 Power-Down I-Channel Pin (PDI)

- 7.5.1.1.7 Power-Down Q-Channel Pin (PDQ)

- 7.5.1.1.8 Test-Pattern Mode Pin (TPM)

- 7.5.1.1.9 Full-Scale Input-Range Pin (FSR)

- 7.5.1.1.10 AC- or DC-Coupled Mode Pin (VCMO)

- 7.5.1.1.11 LVDS Output Common-Mode Pin (VBG)

- 7.5.1.2 Extended Control Mode

- 7.5.1.1

Non-ECM

- 7.5.1

Control Modes

- 7.6 Register Maps

- 8 Application Information Disclaimer

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

3 说明

ADC12D1620QML 使用经重新设计的封装,与 ADC12D1600QML 相比,可实现更佳的 ENOB、SNR 和串扰性能。与其前代产品相同,ADC12D1620QML 也是一款低功耗、高性能 CMOS 模数转换器 (ADC),在交错模式下以 12 位的分辨率和高达 3.2GSPS 的采样率对信号进行数字化。对于高达 1.6GSPS 的采样率,它还可以用作双通道 ADC。对于低于 800MHz 的采样率,该器件提供了可以将功耗降低至低于每通道 1.4W(典型值)的低采样节能模式 (LSPSM)。ADC 可以支持低至 200MSPS 的转换速率。

器件信息

| 器件型号(1) | 等级 | 封装 |

|---|---|---|

| 5962F1220502VXF | SMD 飞行 300krad(Si) | CCGA (376) |

| ADC12D1620CCMLS | 飞行 300krad(Si) | CCGA (376) |

| ADC12D1620CCMPR | 飞行前的工程原型 | CCGA (376) |

| ADC10D1000DAISY | 菊链,机械采样,无裸片 | CCGA (376) |

| ADC12D1620LGMLS | 飞行 300krad(Si) | CLGA (256) |

| ADC12D1620LGMPR | 飞行前的工程原型 | CLGA (256) |

| ADC10D1000LDAZ | 菊链,机械采样,无裸片 | CLGA (256) |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购封装附录 (POA)。

功能方框图

功能方框图