ZHCACX6 july 2023 AM62A1-Q1 , AM62A3 , AM62A7

5.3 内核利用率

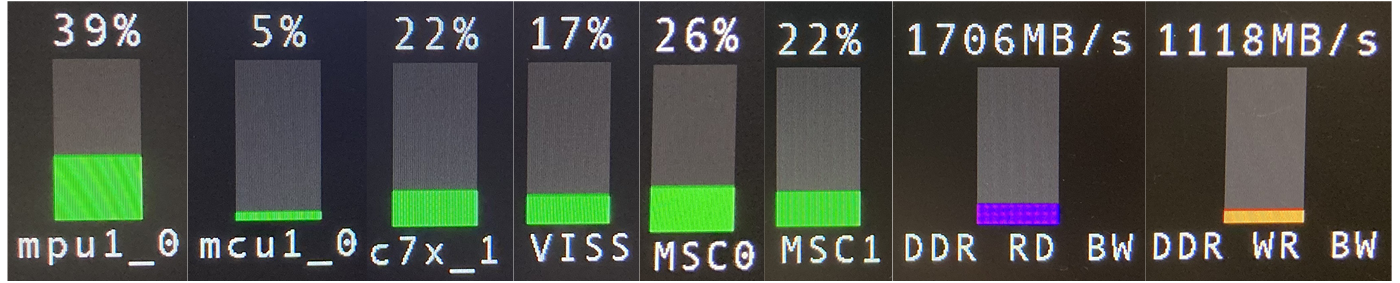

AM62A SoC 包含各种处理内核和硬件加速器。监测这些元件上的负载对于探索整个系统功能和扩展机会非常重要。缺陷检测演示使用 tiperfoverlay gstreamer 插件在屏幕底部以条形图的形式显示内核负载。图 5-2 显示了运行缺陷检测演示时 AM62A 内核负载图的屏幕截图。默认情况下,该图每两秒更新一次,以利用率百分比形式显示负载。除了 tiperfoverlay gstreamer 插件之外,第二个可直接在终端上显示内核性能的选项是 perf_stats 工具(具有文件保存功能)。此选项相比 tiperfoverlay 更精确,tiperfoverlay 会给 Arm 内核和 DDR 带来额外负载,以绘制图形并在屏幕上叠加。

图 5-2 使用 tiperfoverlay gstreamer 插件的缺陷检测演示底部显示的内核负载条形图(该图经过编辑以适合页面)

图 5-2 使用 tiperfoverlay gstreamer 插件的缺陷检测演示底部显示的内核负载条形图(该图经过编辑以适合页面)图 5-2 中的图形显示,除了整个支持 Linux 的进程外,缺陷检测演示仅利用了 Arm 内核容量的约 39%(四个 A53 内核的平均值)。同时,应用中使用的 yolox-nano-lite 利用了 C7xMMA 深度学习加速器的约 22%。值得注意的是,在本实验中,C7xMMA 的时钟频率为 850MHz,而不是 1000MHz。换句话说,如果 C7xMMA 加速器的时钟频率为 1000MHz,其利用率将低于报告的 22%。用于读取操作的 DDR 为 1706MB/s,用于写入操作的 DDR 为 1118MB/s,因此总操作速率为 2824MB/s。在 3200MT/s 速率下使用 32 位 DDR4 时,AM62A 支持速率为 12.8GB/s 的总 DDR 频带。2824MB/s 的总速率利用了总 DDR 带宽的约 22%。

Arm 内核、加速器和 DDR 带宽的这些低利用率值表明,AM62A 有很大的扩展空间,可以运行其他应用或扩展缺陷检测应用本身,例如使用另一个更快的摄像头来提高帧速率。此外,由于内核利用率较低,可以灵活选择合适的 AM6A SoC 型号。图 5-2 中显示的内核负载适用于 SoC AM62A 系列的 AM62A74 型号。该型号配备四个 A53 Arm 内核和一个能够执行 2TOPS 的 C7xMMA 深度学习加速器。低利用率值表明,可在 AM62A 的其他低端型号(例如 AM62A3,其中包括两个 Arm 内核和一个 1TOPS 深度学习加速器)上实现当前形式的缺陷检测演示。