ZHCAB56A January 2021 – February 2022 BQ769142 , BQ76942 , BQ76952

7 控制 LD

在高侧 FET 设计中,LD 引脚通常连接到 PACK+ 并用于 DSG 驱动基准、唤醒信号和电流恢复(如果已选)。数据表指出,当不使用驱动器时,LD 可能通过电阻连接到 PACK+ 或者拉至 VSS。如果拉到高电平,它会阻止器件进入关断模式。如果连接到 VSS,则不能用于控制电流恢复。MCU 可使用主机命令恢复 OCD 事件。该器件提供上拉电阻来测试负载是否移除,因此需要时可设计一个电路来控制 LD。如果不通过命令提供电流恢复,MCU 可以控制电路,或者如果没有可用的 MCU,可通过 PACK- 引脚电平来控制它,如图 7-1 中所示。在发生使 PACK- 接近 PACK+ 的故障后,PACK 端子上存在负载时,LD 保持低电平。如果配置适当,将阻止从电流故障中恢复。电路在 PACK- 上提供下拉电阻,如果移除负载,以使此下拉电阻可以关断信号 FET Q32,LD 将释放,BQ769x2 将 LD 拉到高电平,允许电流恢复。请注意,电路将在 PACK- 上提供下拉电阻,后者通常将 PACK 电压保持在正常电平附近,当 PACK 端子上存在负载时,它会成为电池上的泄漏点。当 CHG 保持导通时,栅极驱动电压将上拉 PACK- 电压,而根据 R66 和 R67 电阻的值,可能阻止关断 Q32。

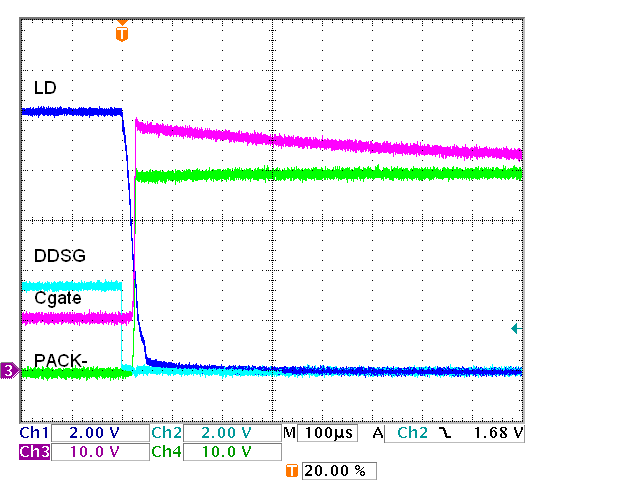

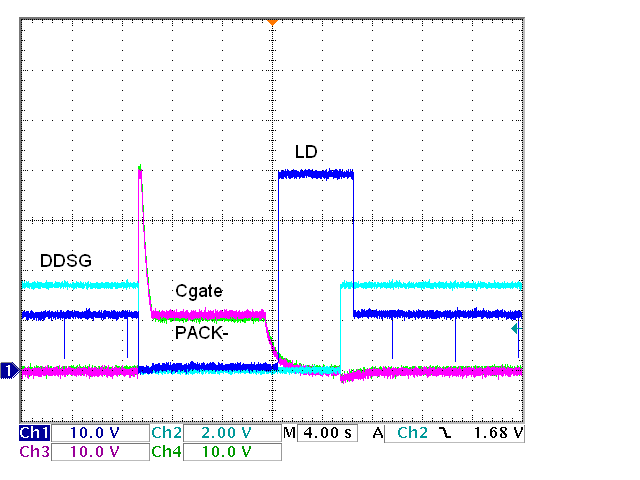

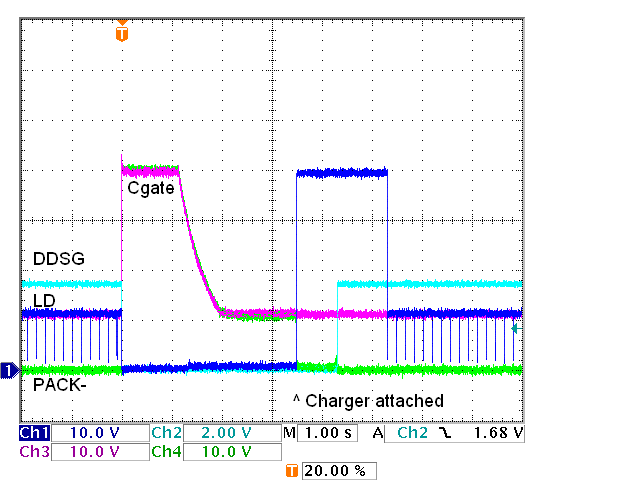

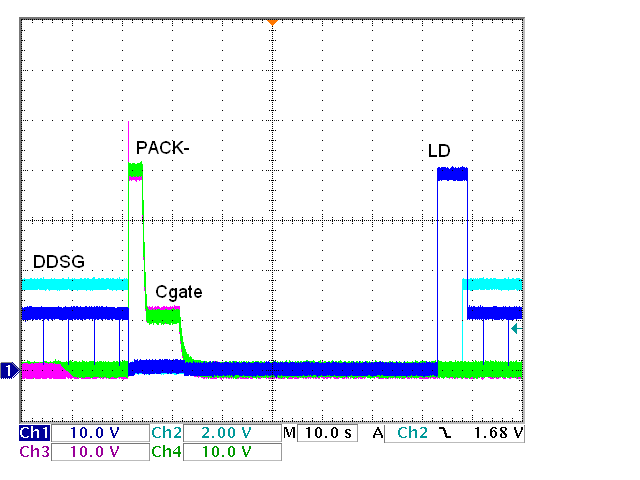

图 7-2 展示了测试电路的 OCD 事件。DDSG 关闭,负载上拉 PACK-,电路下拉 LD。充电 FET 栅极 Cgate 也会由 PACK- 上拉,随着时间的流逝放电至 PACK- 电平。在 DCHG 导通的情况下,当负载释放但器件保持唤醒状态时,驱动器将 PACK- 向上偏置到驱动器电平附近。根据为 R66 和 R67 选择的分压电阻,电路可能使 LD 保持在低电平,恢复将不会发生,直至连接充电器,如图 7-3 中所示。BQ769x2 处于睡眠状态时,如果 CHG 在睡眠期间关断,PACK- 可在负载移除后下降,恢复可能快速发生,如图 7-4 中所示。如果在 Protections:Load Detect:Active Time 之后并在电流停止后移除负载,器件将在 Protections:Load Detect:Retry Delay 之后重试,如图 7-5 中所示。如有必要,器件将一直重试,直至 Protections:Load Detect:Timeout。

图 7-2 OCD 和受控 LD

图 7-2 OCD 和受控 LD 图 7-4 睡眠期间的 OCD 和恢复

图 7-4 睡眠期间的 OCD 和恢复 图 7-3 OCD 和从充电器连接恢复

图 7-3 OCD 和从充电器连接恢复 图 7-5 睡眠期间的 OCD 和重试后恢复

图 7-5 睡眠期间的 OCD 和重试后恢复由于低侧开关和 LD 连接到由上述电路控制的 VSS 或 LD,唤醒信号需要来自 TS2。执行此操作的简单电路如图 7-6 中所示。当朝向 PACK+ 上拉“唤醒”信号时,TS2 下拉导致 BQ769x2 唤醒。如果唤醒信号直接连接到 PACK+,电路将在电池上提供持续漏极。根据需要调整 R80 的值并提供瞬态保护或使用适合该应用的替代电路。