ZHCAB56A January 2021 – February 2022 BQ769142 , BQ76942 , BQ76952

4 逻辑电平 FET

某些设计人员将认识到 REG1 可设置为 5V,而且可能要考虑使用由 DDSG 和 DCHG 输出直接控制的逻辑电平 FET。DDSG 和 DDCHG 提供开关功能,并提供 5V 作为 VFETON 电平。数字输出的测试条件为 IOH 和 IOL 具有 5mA 拉电流或灌电流 ,但负载测试条件为 10pF 而且没有指定上升或下降时间。

REG1 为 5V 时,要更改数据存储器配置。

Settings:Configuration:REG12 Config 0x0F

设计人员可能用更强大的 5V 驱动器来缓冲信号,而本应用报告提供的是使用数字输出直接驱动 FET 的示例。实际使用的是具有 4.5V 下 RDSON 规格的 CSD18535KCS FET。图 4-1 中展示了使用 DDSG 和 DCHG 信号驱动 FET 的示例原理图。使用并联 FET 时,使用 51Ω 电阻使栅极彼此隔离,以避免高频振荡。使用单个 FET 时,此测试电路保留了 51Ω 电阻,因此驱动电阻有所增加。

使用 1kΩ 栅极电阻 R27 驱动单个放电 FET 时,在图 4-2 中发现了驱动器振铃。这是使用的 FET 产生的迹线寄生效应,驱动器无法为 FET 维持合适的驱动电流。使用四个 FET 时,来自额外 Ciss 的驱动器上的额外负载会减缓导通速度并避免振铃。不过,图 4-3 展示了负载会暂时下拉稳压器电压。如果不希望这样,可以增大 REG1 上的电容。此部分的测试波形不包括增大的 REG1 电容。

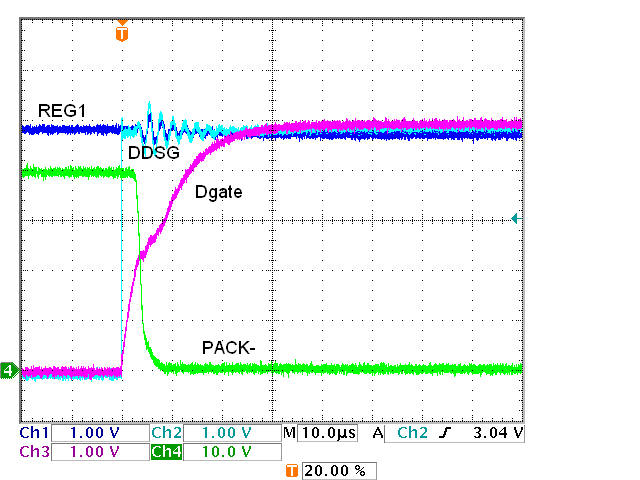

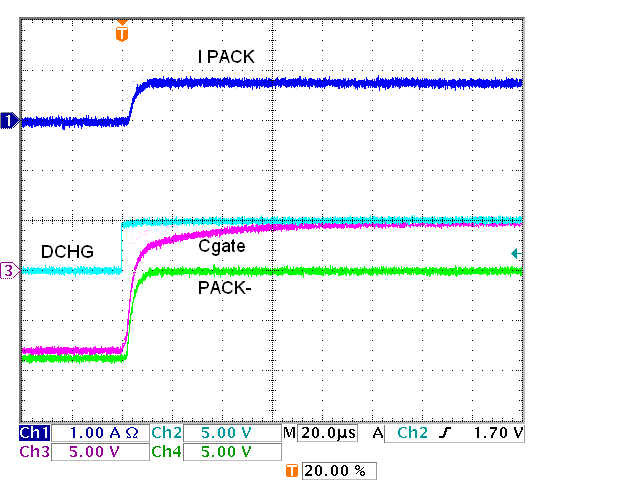

图 4-2 在一个 FET、1kΩ 栅极电阻条件下的放电 FET 导通

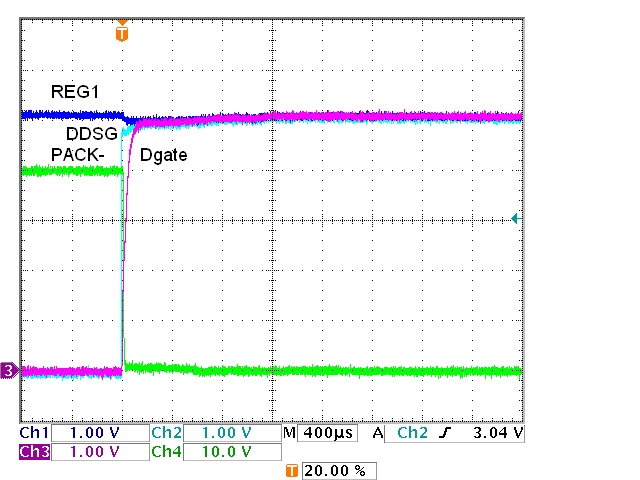

图 4-2 在一个 FET、1kΩ 栅极电阻条件下的放电 FET 导通 图 4-3 在四个 FET、1kΩ、REG1 降压条件下的放电 FET 导通

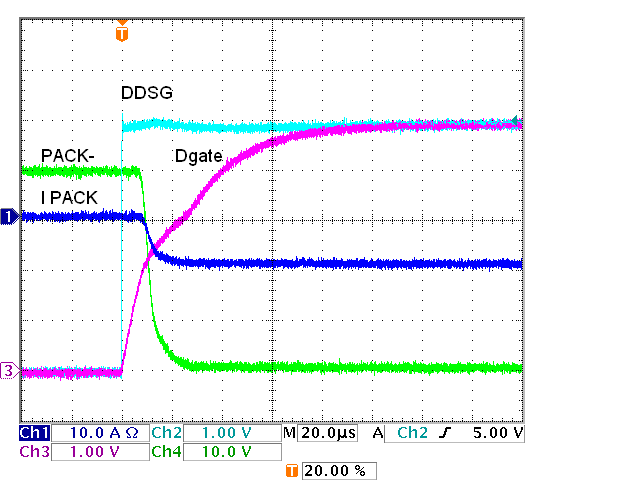

图 4-3 在四个 FET、1kΩ、REG1 降压条件下的放电 FET 导通建立电路板拓扑后,设计人员可使用栅极电阻 R27 进行调节,以避免栅极振铃。增大电阻有助于减缓 FET 导通速度并避免振铃。实际选择了 3kΩ 阻值,单个 FET 的导通和关断如图 4-4 和图 4-5 中所示。

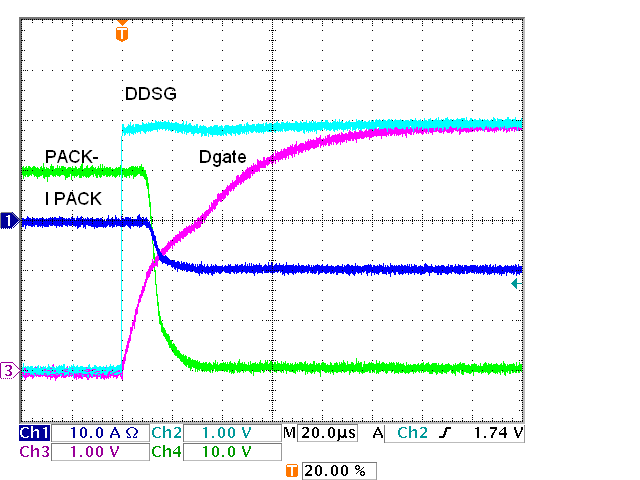

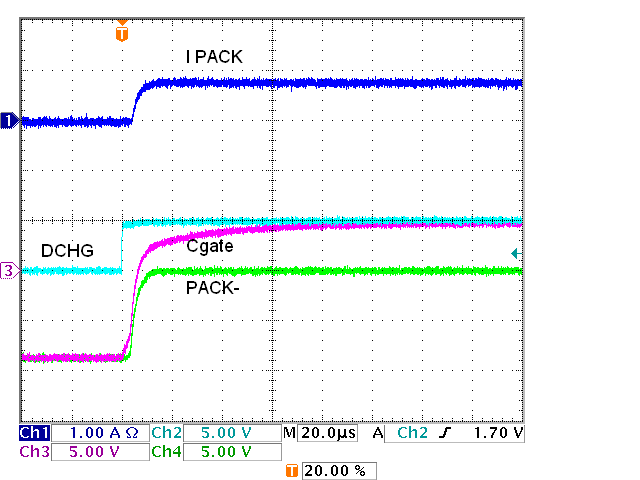

图 4-4 在 3kΩ 栅极电阻下,DDSG 驱动一个 FET 导通

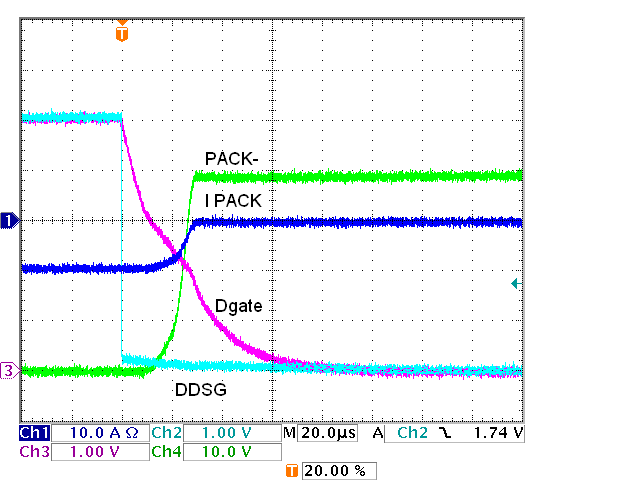

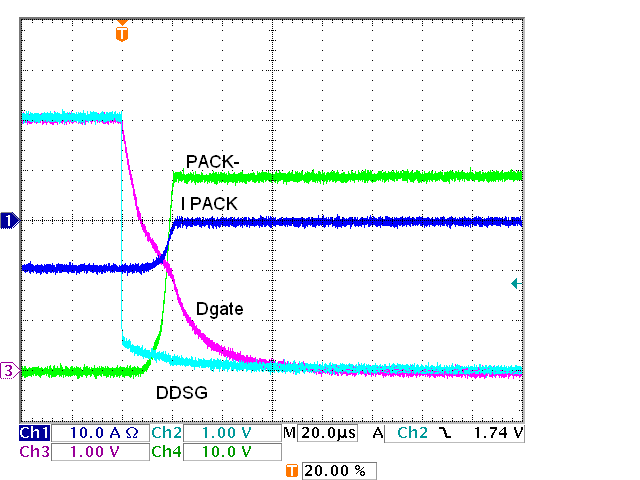

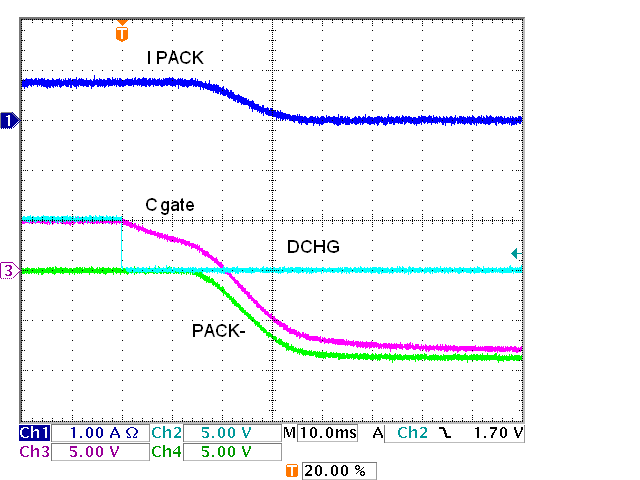

图 4-4 在 3kΩ 栅极电阻下,DDSG 驱动一个 FET 导通 图 4-5 在 3kΩ 栅极电阻下,DDSG 驱动一个 FET 关断

图 4-5 在 3kΩ 栅极电阻下,DDSG 驱动一个 FET 关断当充电 FET 关断时,充电器可以自由地将 PACK- 端子拉至电池负极(即 GND)电平以下。当 DCHG 变为高电平时,充电 FET 将导通。此情况下的电压摆幅很小,在此测试中未观察到驱动器振铃。图 4-6 展示了使用 1kΩ 栅极电阻时单个充电 FET 导通的示例。关断如图 4-7 中所示。请注意,DCHG 很快会变为低电平,因为它不驱动栅极,D3 会阻止电流进入驱动器。栅源电阻 R35 会关断 FET,在此测试中它是 1 MΩ,所以关断速度慢。另请注意,10M 示波器探头上拉 Cgate 信号,形成分压器并保持栅极略高于 PACK- 信号。

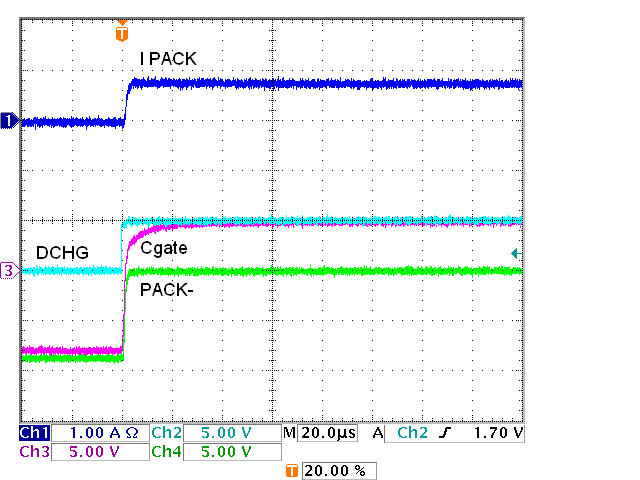

图 4-6 DCHG 驱动一个 FET 导通

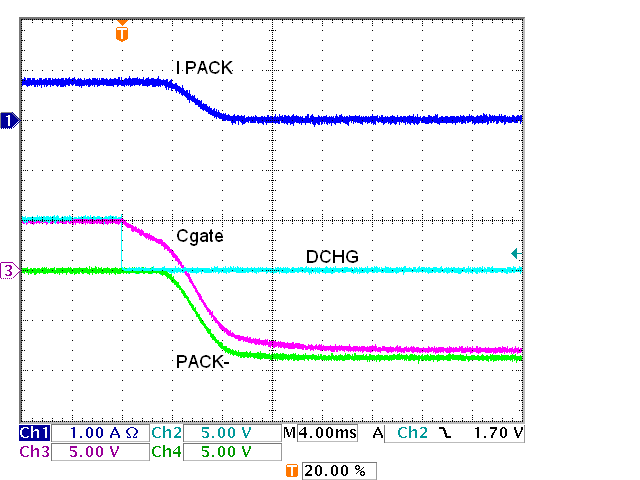

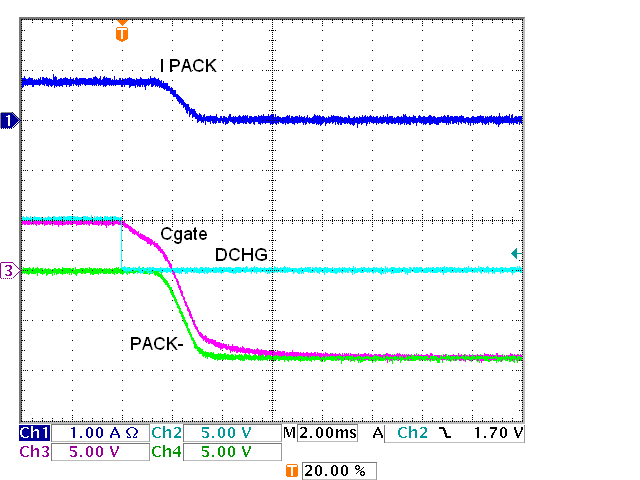

图 4-6 DCHG 驱动一个 FET 导通 图 4-7 DCHG 驱动一个 FET 关断

图 4-7 DCHG 驱动一个 FET 关断图 4-8 展示了具有四个 FET 的原理图。总栅极电阻较大,因而对 R27 使用 1kΩ 电阻。由于预期放电电流较高,放电时不希望缓慢关断,所以使用肖特基二极管提供与 R28 并联的电阻路径进行关断。二极管 D6 在导通期间阻止电流进入栅极,但允许 DDSG 在关断期间通过 R27 和 R28 从栅极拉取电流。

由于具有四个 FET 和 1kΩ 驱动电阻,此测试中的 DDSG 没有振铃。在图 4-9 中可看到,当 FET 导通时 DDSG 中有压降。图 4-10 展示了添加图 4-8 中的 D6 肖特基二极管和 R28 1kΩ 路径后的关断情况。R28 可以减小以加快关断速度,或者 PNP 晶体管电路仅需要来自 DDSG 的控制电流。

图 4-9 在 1kΩ 肖特基二极管下,DDSG 驱动四个 FET 导通

图 4-9 在 1kΩ 肖特基二极管下,DDSG 驱动四个 FET 导通 图 4-10 在 1kΩ 肖特基二极管下,DDSG 驱动四个 FET 关断

图 4-10 在 1kΩ 肖特基二极管下,DDSG 驱动四个 FET 关断使用四个 FET 导通 CHG 如图 4-11 中所示。通过 1 MΩ RGS 关断四个 FET 如图 4-12 中所示。FET 导通时使用该大电阻限制电流,因而关断缓慢。

图 4-11 DCHG 驱动四个 FET 导通,1kΩ,1 MΩ RGS

图 4-11 DCHG 驱动四个 FET 导通,1kΩ,1 MΩ RGS 图 4-12 DCHG 驱动四个 FET 关断,1kΩ,1 MΩ RGS

图 4-12 DCHG 驱动四个 FET 关断,1kΩ,1 MΩ RGS需要加快关断速度时,包含 REG1 电压和逻辑电平 FET 的电路几乎没有电压裕量。一个解决方案是使用较小的 RGS 电阻 R35。91kΩ RGS 的使用如图 4-13 和图 4-14 中所示。导通波形与较大的 RGS 波形相似,但关断速度快得多。此解决方案具有 5V 电源,当充电 FET 导通时需要大概 50μA 的额外电流。

图 4-13 在 91kΩ RGS 下,DCHG 驱动四个 FET 导通

图 4-13 在 91kΩ RGS 下,DCHG 驱动四个 FET 导通 图 4-14 在 91kΩ RGS 下,DCHG 驱动四个 FET 关断

图 4-14 在 91kΩ RGS 下,DCHG 驱动四个 FET 关断考虑使用逻辑电平 FET 解决方案时,设计人员应执行容差分析。鉴于 REG1 和 D3 肖特基二极管的容差,应使用足够低的 RGSON FET。