SPRUJ06 October 2021

- Trademarks

- 1Introduction

- 2Revisions and Assembly Variants

- 3System Description

- 4Known Issues

3.3.2 IO-Link Section Overview and Major Component Description

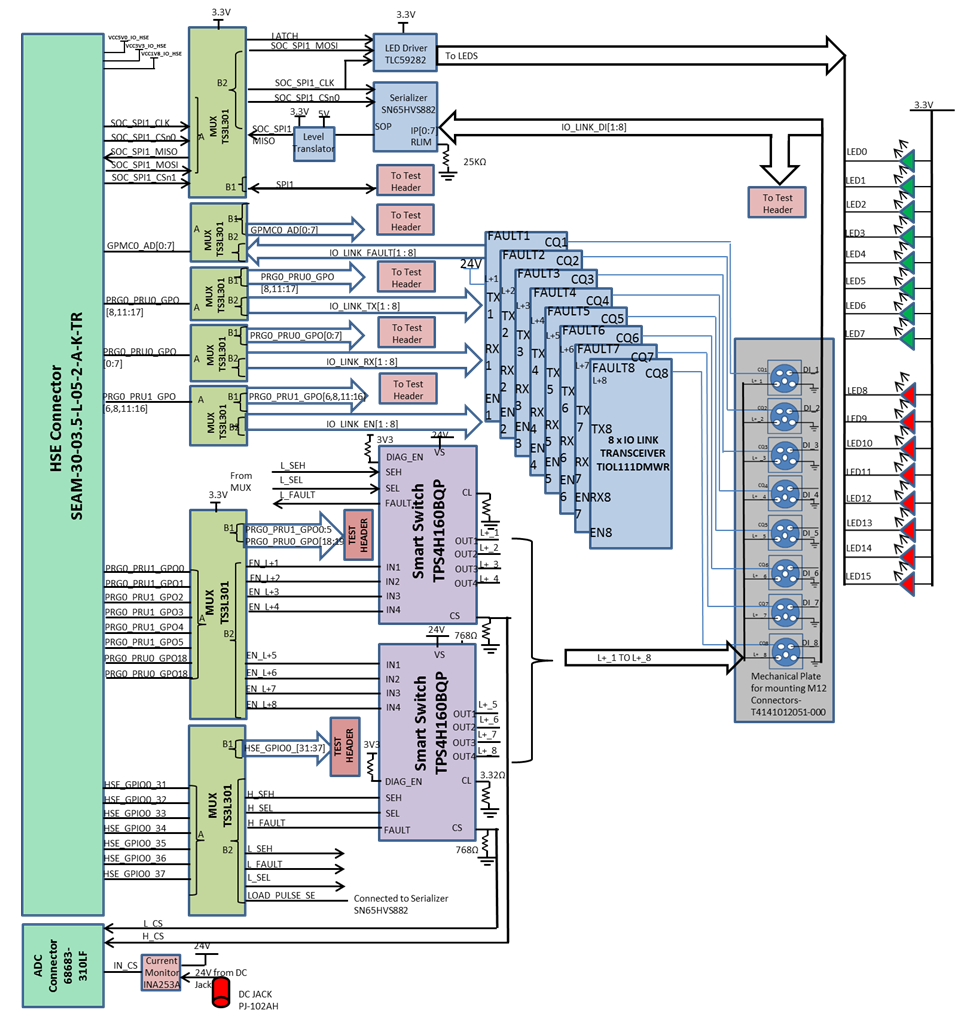

The IO-Link section of this board implements an IO-Link master using the TIOL111 device PHY and surrounding components needed to build a complete IO-Link master design. Therefore, on the physical side in addition to the TIOL111 device, a power supply for the ports, as well as a current sink is necessary. Also the hardware must be able to drive the wake-up pulse.

On the other side it is necessary to have a hardware as well as frame handler that support all three communication speeds. The TIOL111 device used as PHY here can handle all speeds (COM1, COM2, COM3). The eight port frame handler is implemented on the PRU of the used AM64x.

To realize an eight-port master, this design consists of eight M12 connectors and eight TIOL111DMWR IO-Link PHYs and associated LEDs. The IO-Link circuit is supported by two TPS4H160BQPWPRQ1 Quad channel smart high-side switches for the L+ signals and a SN65HVS882 serializer to support the D signals. The D signals are connected to a 10 pin header J21 for testing purpose. Both parts require a +24V which is supplied by a power jack on the board. A TLC59282 16bit IO expander is also included to drive the 16 LEDs. The SN65HVS882 and TLC59282 16bit IO expander are controlled by SOC_SPI1 interface from GP EVM Board. SOC_SPI0. SOC_SPI1_CS0 is connected to the serializer and SOC_SPI1_CS1 is connected to the LED driver.

Figure 3-4 IO-Link Section Functional Block

Diagram

Figure 3-4 IO-Link Section Functional Block

Diagram