ZHCSCY6A June 2014 – July 2014 LMK00804B

PRODUCTION DATA.

- 1 特性

- 2 应用

- 3 说明

- 4 简化电路原理图

- 5 修订历史记录

- 6 Device Comparison Table

- 7 Pin Configuration and Functions

-

8 Specifications

- 8.1 Pin Characteristics

- 8.2 Absolute Maximum Ratings

- 8.3 Handling Ratings

- 8.4 Recommended Operating Conditions

- 8.5 Thermal Information

- 8.6 Power Supply Characteristics

- 8.7 LVCMOS / LVTTL DC Characteristics

- 8.8 Differential Input DC Characteristics

- 8.9 Electrical Characteristics (VDDO = 3.3 V ± 5%)

- 8.10 Electrical Characteristics (VDDO = 2.5 V ± 5%)

- 8.11 Electrical Characteristics (VDDO = 1.8 V ± 0.15 V)

- 8.12 Electrical Characteristics (VDDO = 1.5 V ± 5%)

- 8.13 Typical Characteristics

- 9 Parameter Measurement Information

- 10Detailed Description

- 11Applications and Implementation

- 12Power Supply Recommendations

- 13Layout

- 14器件和文档支持

- 15机械封装和可订购信息

13 Layout

13.1 Layout Guidelines

13.1.1 Ground Planes

Solid ground planes are recommended as they provide a low-impedance return paths between the device and its bypass capacitors and its clock source and destination devices.

Avoid return paths of other system circuitry (for example, high-speed/digital logic, switching power supplies, and so forth) from passing through the local ground of the device to minimize noise coupling, which could induce added jitter and spurious noise.

13.1.2 Power Supply Pins

Follow the power supply schematic and layout example described in Power-Supply Filtering.

13.1.3 Differential Input Termination

- Place input termination or biasing resistors as close as possible to the CLK/nCLK pins.

- Avoid or minimize vias in the 50 Ω input traces to minimize impedance discontinuities. Intra-pair skew should be also be minimized on the differential input traces.

- If not used, CLK/nCLK inputs may be left floating.

13.1.4 LVCMOS Input Termination

- When the LVCMOS_CLK input is driven from a LVCMOS driver that is series terminated to match the characteristic impedance of the trace, then input termination is not necessary; otherwise, place the input termination resistor as close as possible to the LVCMOS_CLK input.

- Avoid or minimize vias in the 50 Ω input trace to minimize impedance discontinuities.

- If not used, LVCMOS_CLK input may be left floating.

13.1.5 Output Termination

- Place 43 Ω series termination resistors as close as possible to the Qx outputs at the launch of the 50 Ω traces.

- Avoid or minimize vias in the 50 Ω input traces to minimize impedance discontinuities.

- If not used, any Qx output should be left floating and not routed.

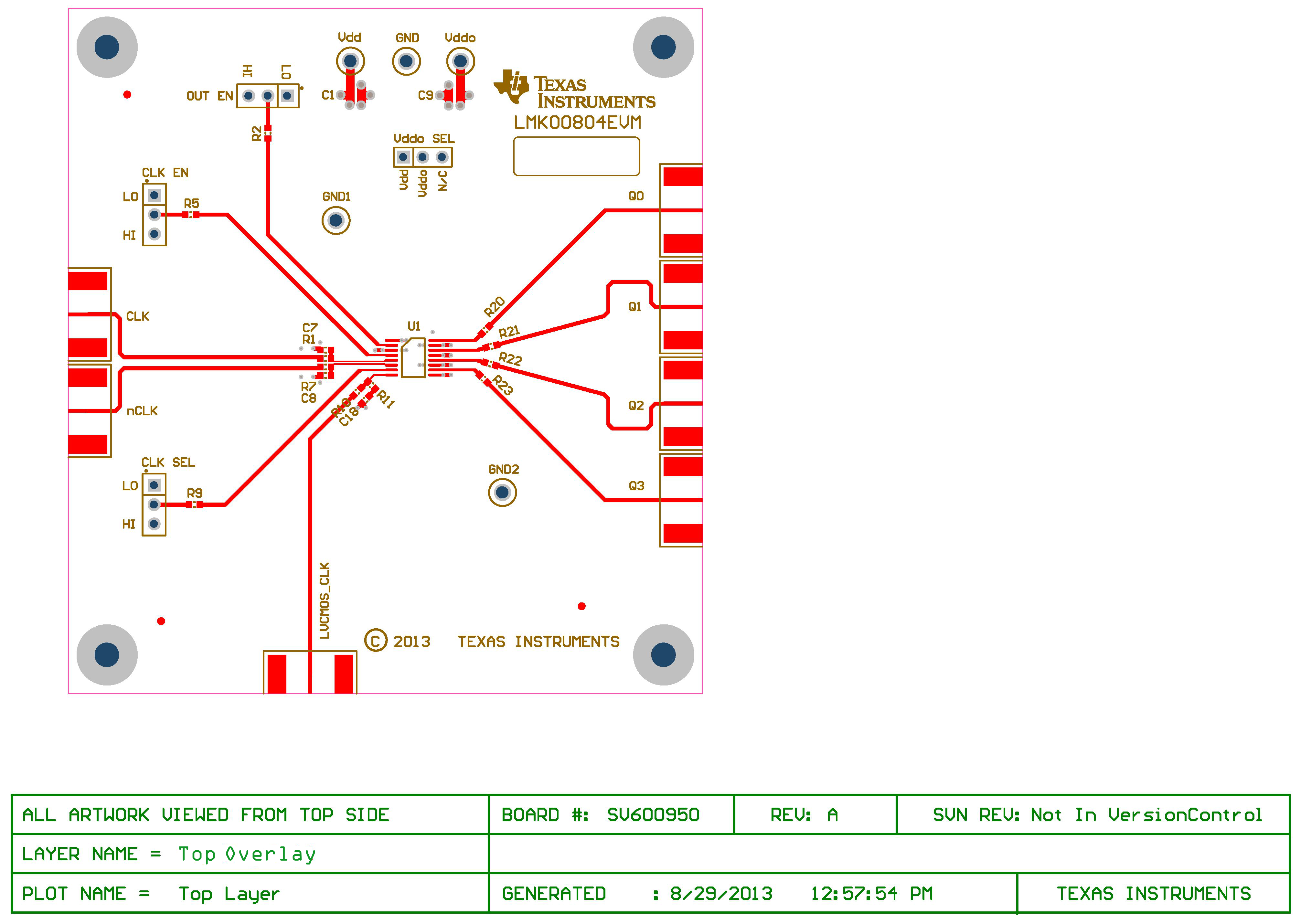

13.2 Layout Example

Please refer to the LMK00804BEVM for a layout example. A sample PCB layer is shown below.

Figure 21. Sample PCB Layout, Layer 1 (Top View)

Figure 21. Sample PCB Layout, Layer 1 (Top View)