ZHCSOT2D January 2022 – May 2025 AFE7906

PRODUCTION DATA

- 1

- 1特性

- 2应用

- 3说明

- 4规格

- 5器件和文档支持

- 6修订历史记录

- 7机械、封装和可订购信息

封装选项

机械数据 (封装 | 引脚)

散热焊盘机械数据 (封装 | 引脚)

订购信息

4.11.1 30 MHz 和 400 MHz 下的 RX 典型特性

TA = +25°C 时的典型值。30MHz 下的默认条件:ADC 采样率 = 1500MSPS,输出采样率 = 62.5MSPS(抽取因子为 24x),PLL 时钟模式,fREF = 500MHz,AIN = –3dBFS,DSA 设置 = 3dB。400MHz 下的默认条件:ADC 采样率 = 1500MSPS,输出采样率 = 125MSPS(抽取因子为 12x),PLL 时钟模式,fREF = 500MHz,AIN = –3dBFS,DSA 设置 = 3dB。

| 标准化为 30MHz |

| 差分振幅误差 = PIN(DSA 设置 - 1)- PIN(DSA 设置)+ 1 |

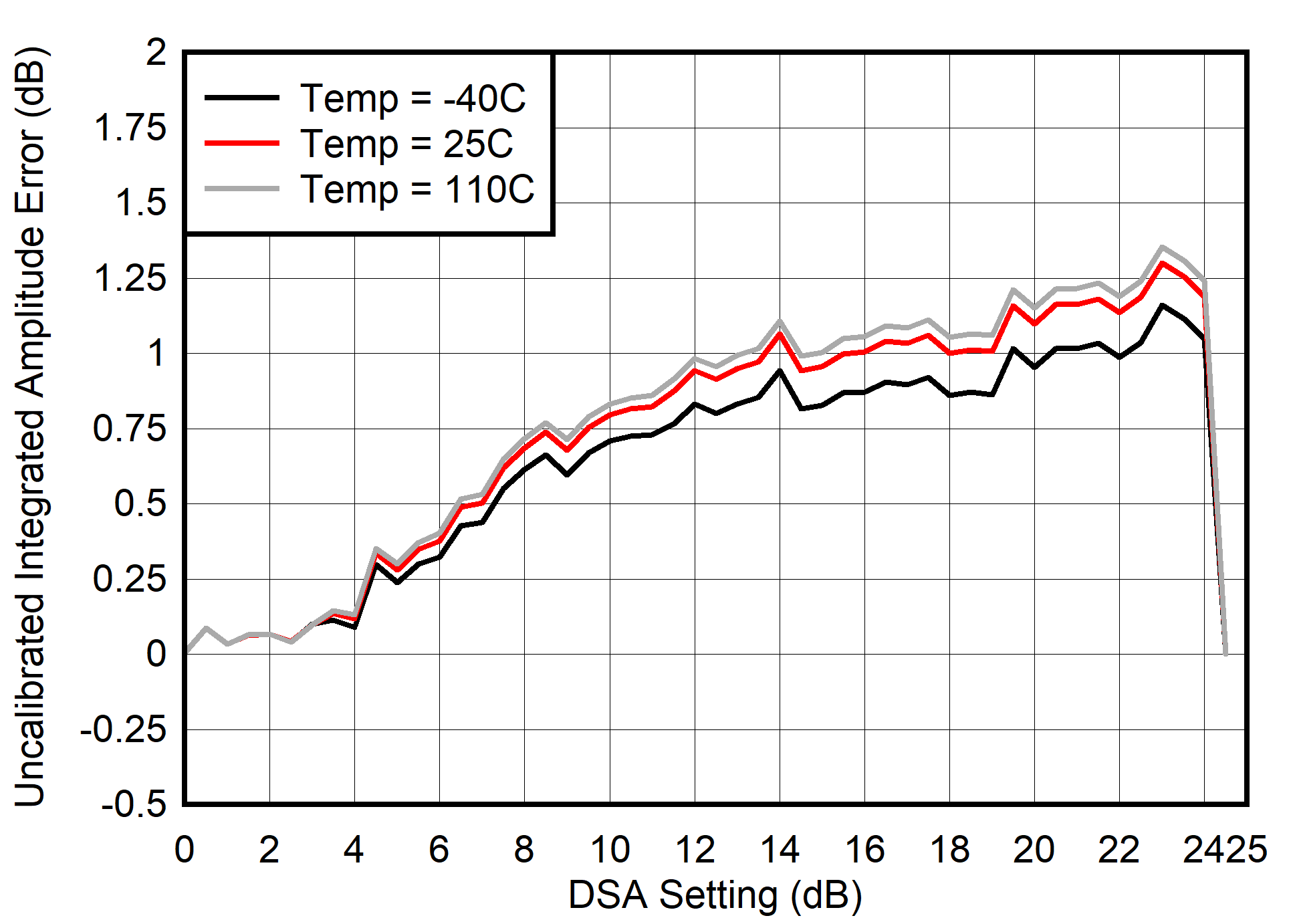

| 积分振幅误差 = PIN(DSA 设置)- PIN(DSA 设置 = 0)+(DSA 设置) |

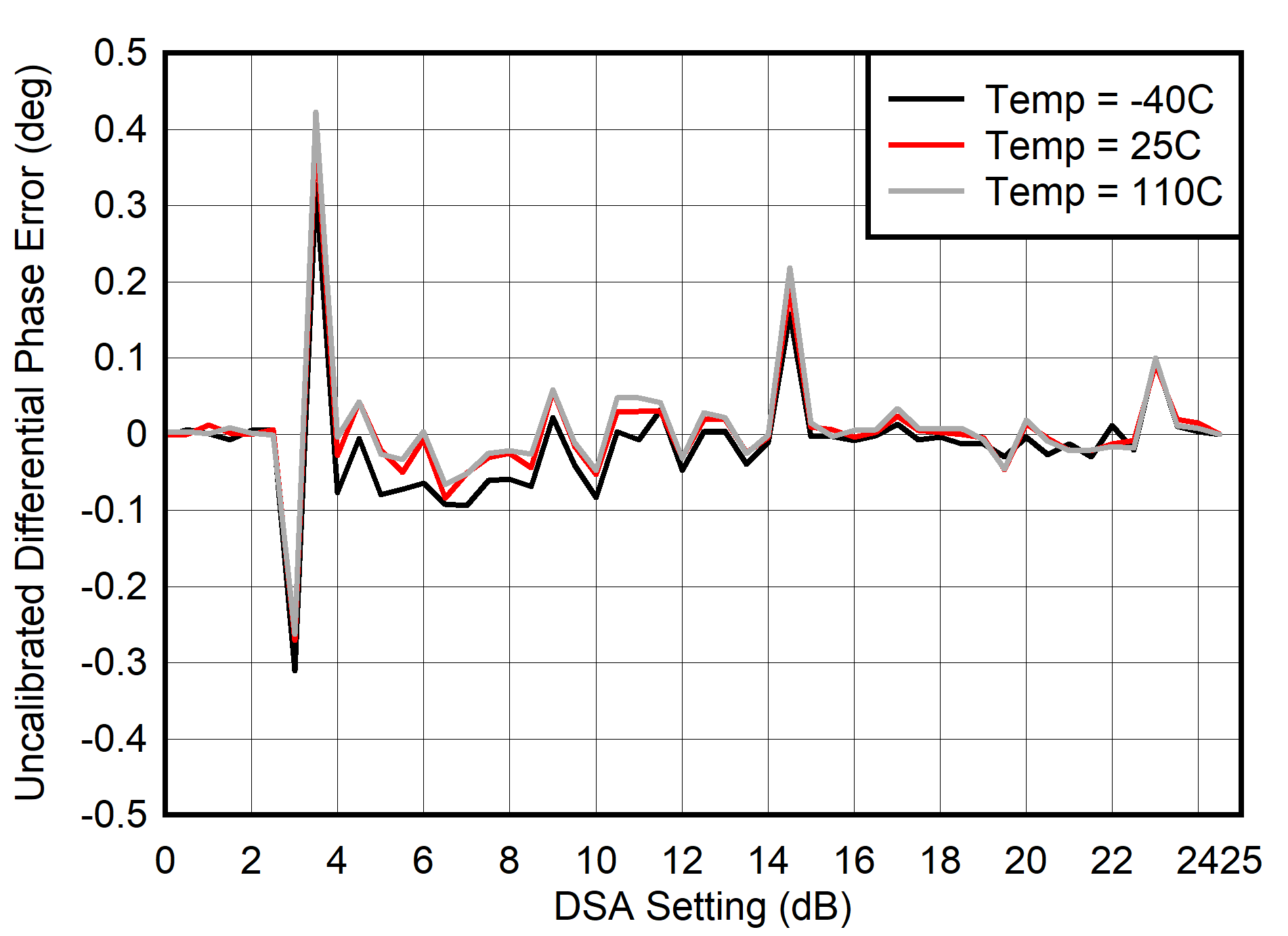

| 差分相位误差 = PhaseIN(DSA 设置 - 1)- PhaseIN(DSA 设置) |

| 使用 0.8GHz 匹配 | ||

| 积分相位误差 = Phase(DSA 设置)- Phase(DSA 设置 = 0) |

| AIN = -6dBFS,fADC = 1500MSPS,fNCO = 32.抽取因子为 24x |

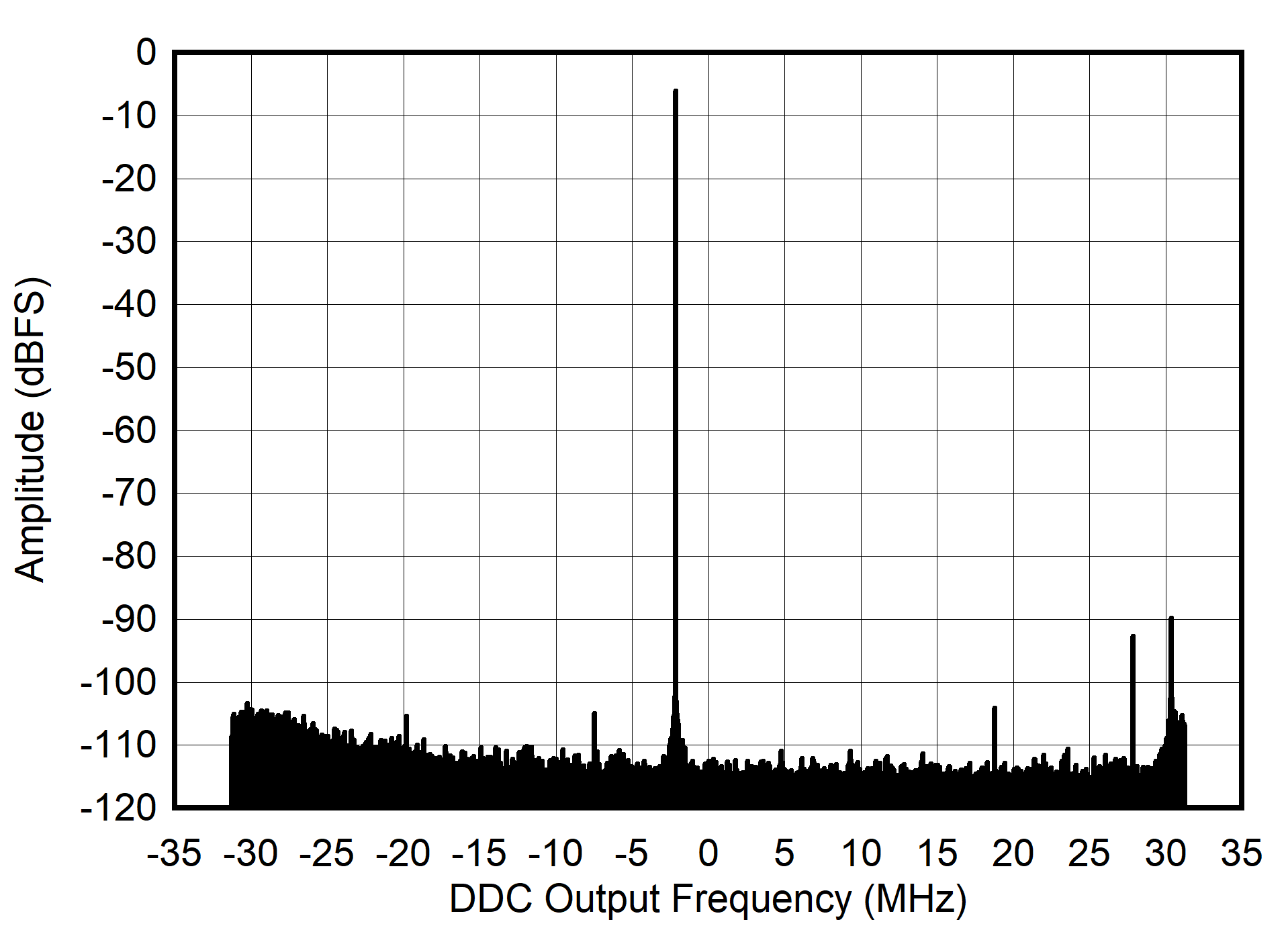

| AIN = -30dBFS,fADC = 1500MSPS,fNCO = 32.13MHz,抽取因子为 24x |

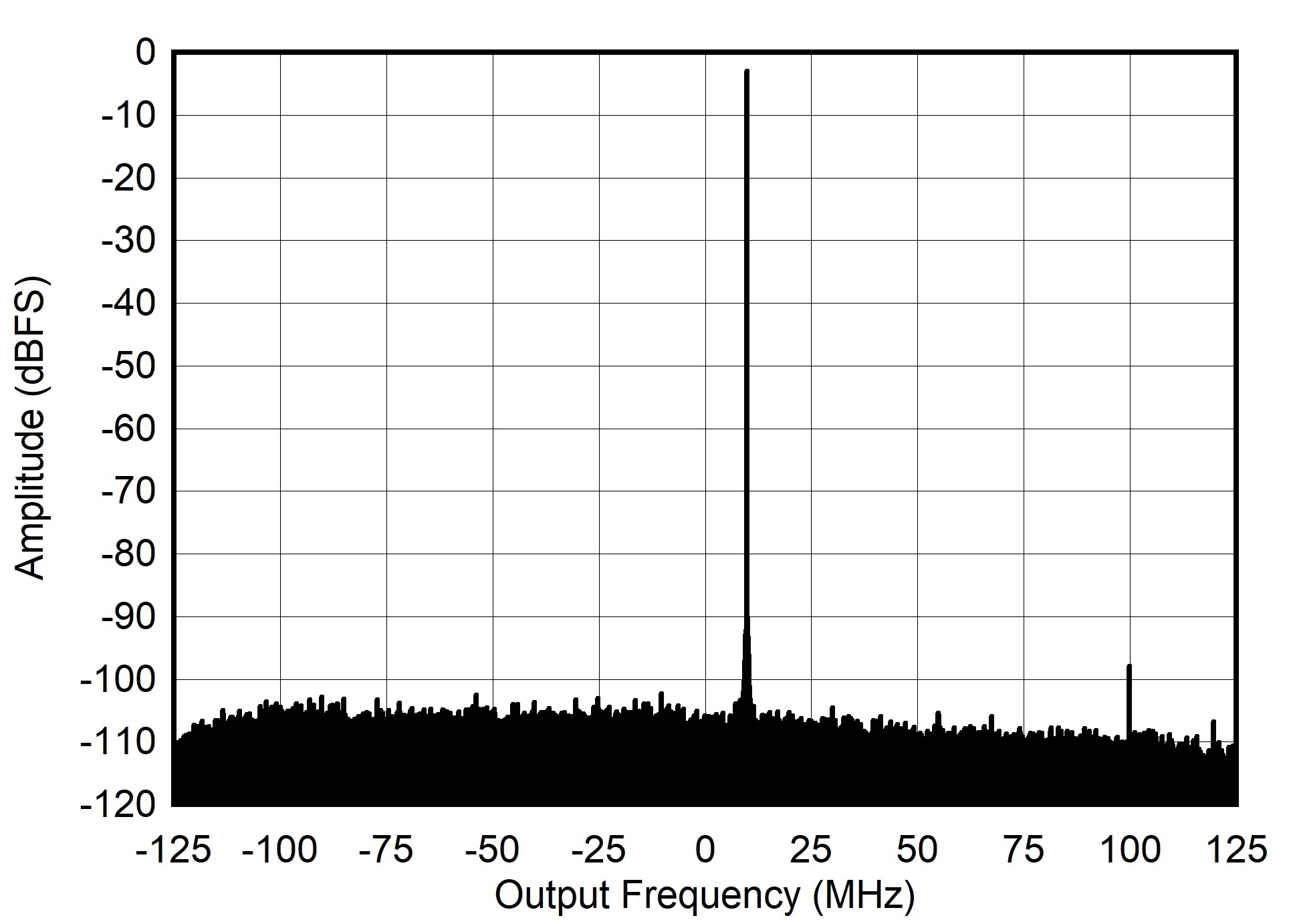

| AIN = -3dBFS,fADC = 1500MSPS,fNCO = 32.13MHz,抽取因子为 24x |

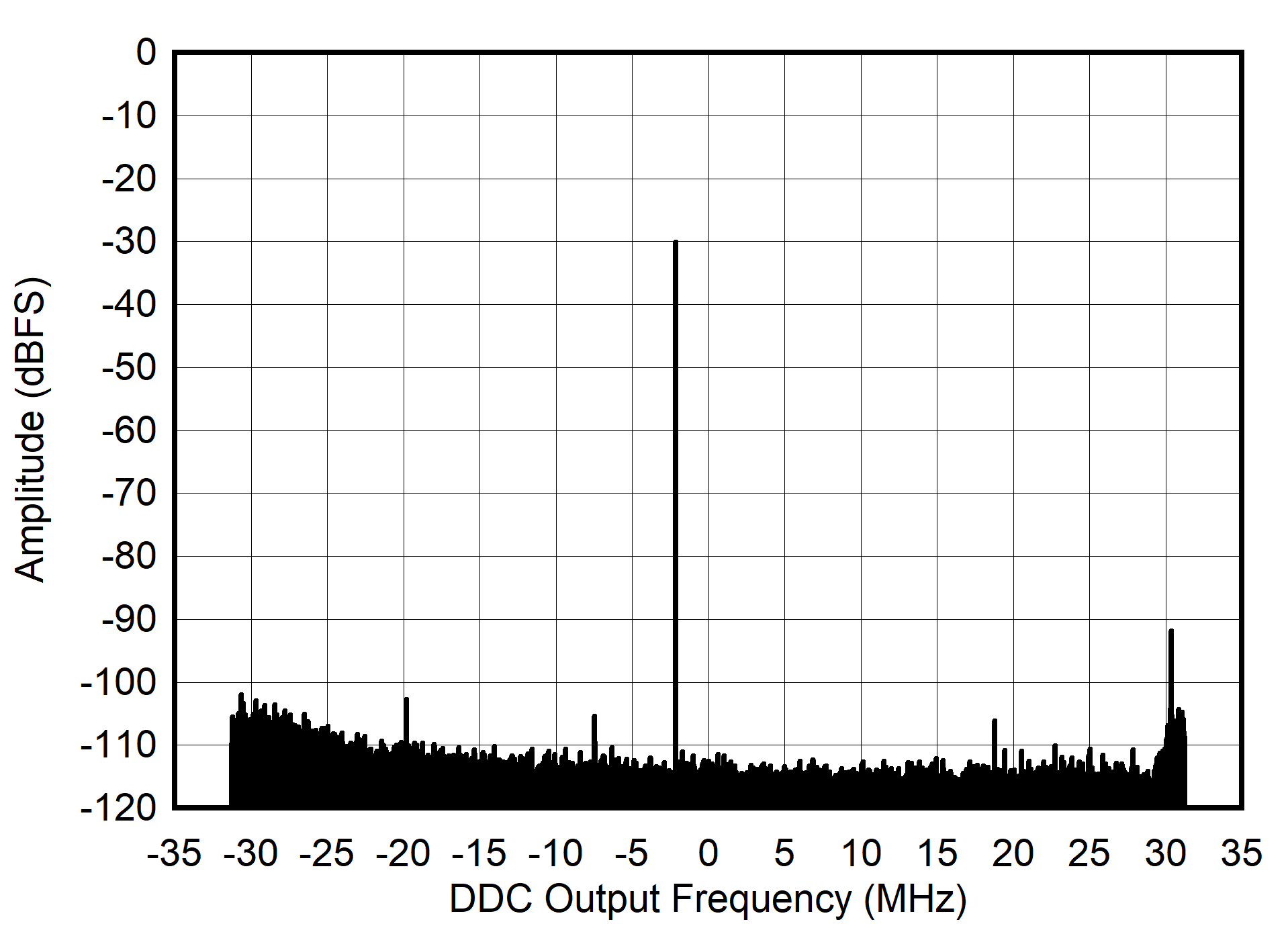

| AIN = -12dBFS,fADC = 1500MSPS,fNCO = 32.13MHz,抽取因子为 24x |

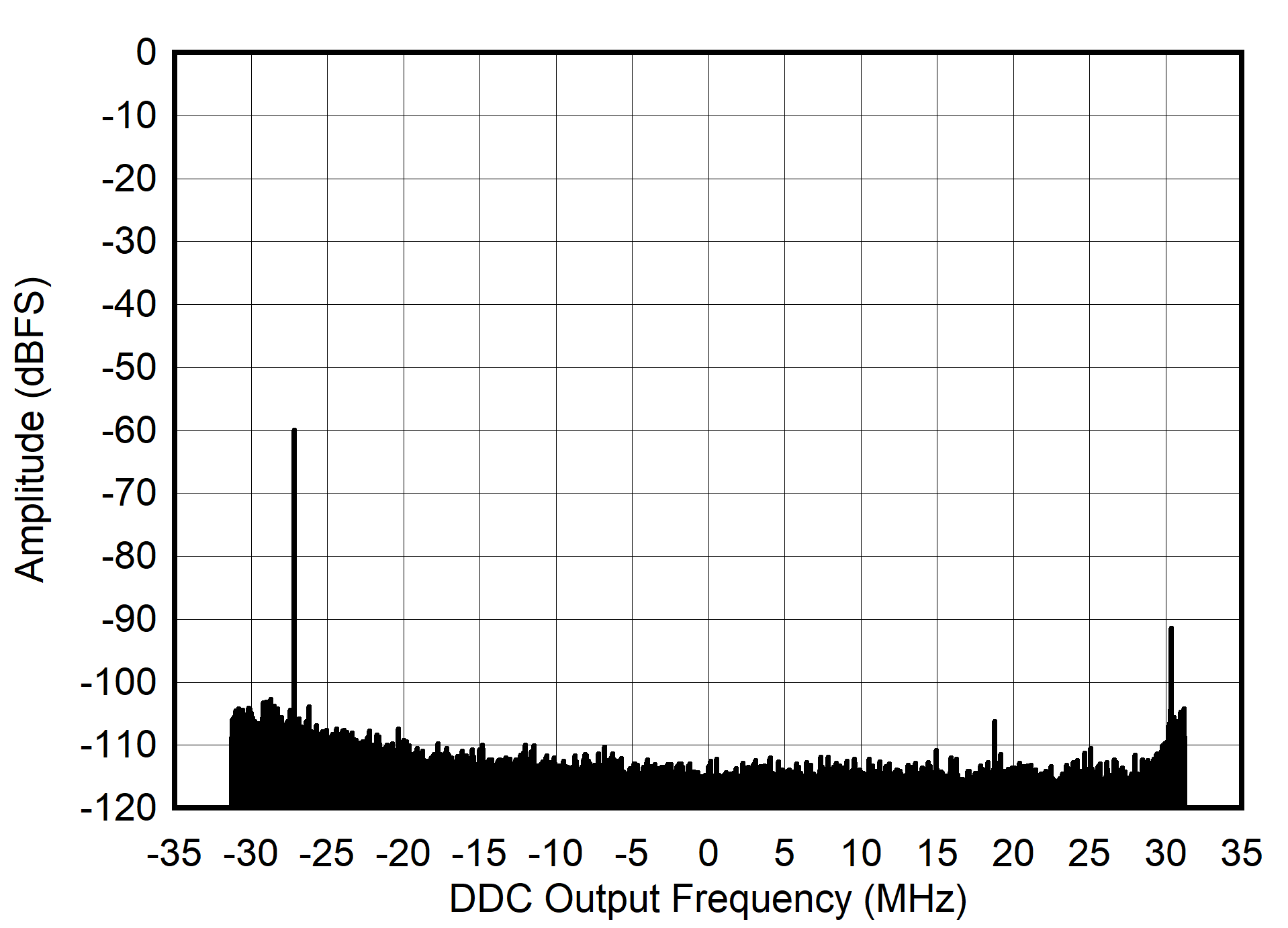

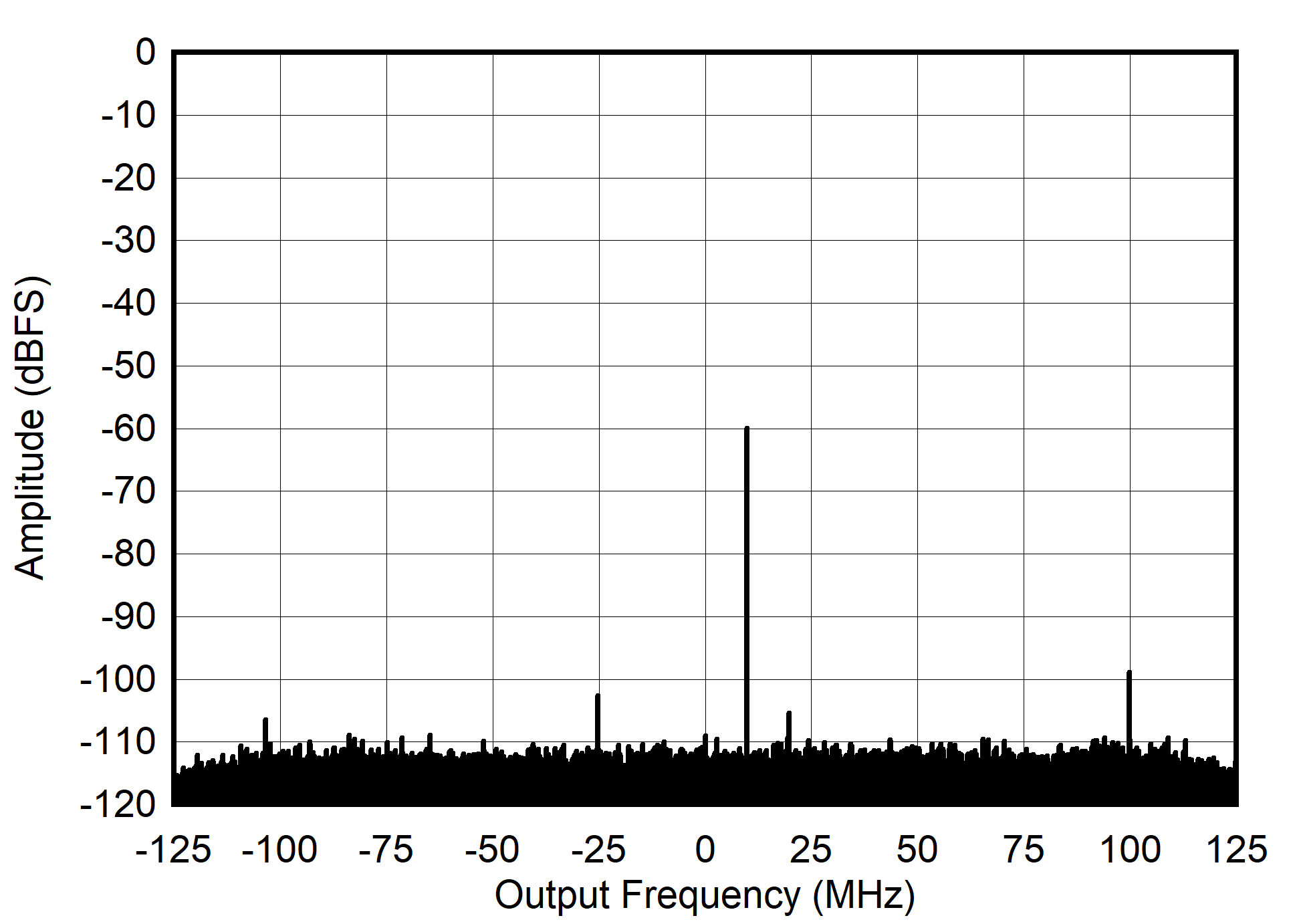

| AIN = -60dBFS,fADC = 1500MSPS,fNCO = 32.13MHz,抽取因子为 24x |

| fADC = 1500MSPS,fNCO = 32.13MHz,抽取因子为 24x |

| fADC = 1500MSPS,fNCO = 32.13MHz,抽取因子为 24x |

| fADC = 1500MSPS,fNCO = 32.13MHz,抽取因子为 24x |

| fADC = 1500MSPS,fNCO = 32.13MHz,抽取因子为 24x |

| 标准化为 4000MHz |

| 差分振幅误差 = PIN(DSA 设置 - 1)- PIN(DSA 设置)+ 1 |

| 积分振幅误差 = PIN(DSA 设置)- PIN(DSA 设置 = 0)+(DSA 设置) |

| 差分相位误差 = PhaseIN(DSA 设置 - 1)- PhaseIN(DSA 设置) |

| 积分相位误差 = Phase(DSA 设置)- Phase(DSA 设置 = 0) |

| fNCO = 400MHz |

| fNCO = 400MHz |

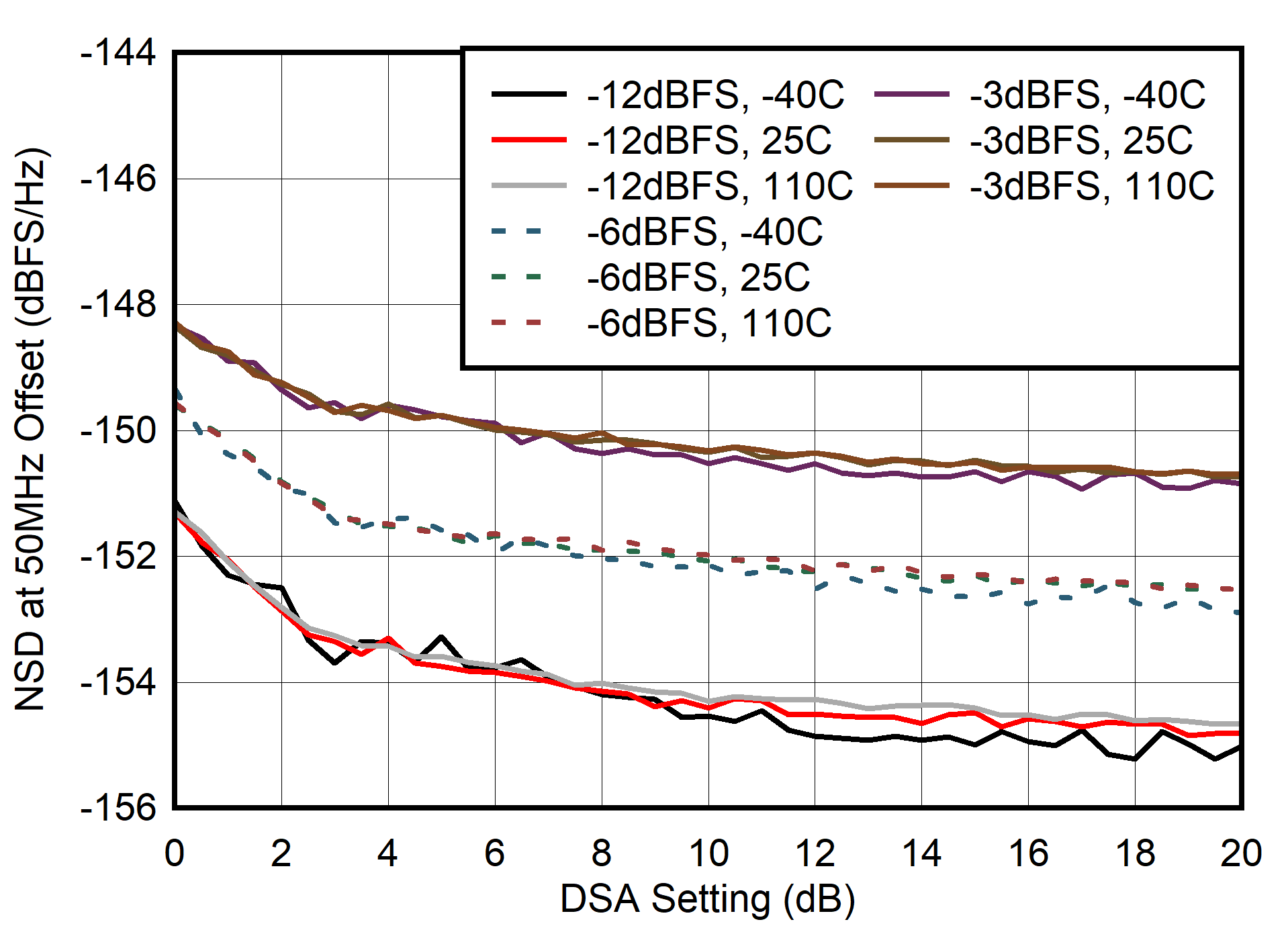

| fOFFSET = 50MHz |

| 差分振幅误差 = PIN(DSA 设置 - 1)- PIN(DSA 设置)+ 1 |

| 积分振幅误差 = PIN(DSA 设置)- PIN(DSA 设置 = 0)+(DSA 设置) |

| 差分相位误差 = PhaseIN(DSA 设置 - 1)- PhaseIN(DSA 设置) |

| 积分相位误差 = Phase(DSA 设置)- Phase(DSA 设置 = 0) |

| AIN = -3dBFS,fADC = 1500MSPS,fNCO = 32.13MHz,抽取因子为 24x |

| AIN = -12dBFS,fADC = 1500MSPS,fNCO = 32.13MHz,抽取因子为 24x |

| AIN = -60dBFS,fADC = 1500MSPS,fNCO = 32.13MHz,抽取因子为 24x |

| AIN = -6dBFS,fADC = 1500MSPS,fNCO = 32.13MHz,抽取因子为 24x |

| AIN = -30dBFS,fADC = 1500MSPS,fNCO = 32.13MHz,抽取因子为 24x |

| fADC = 1500MSPS,fNCO = 32.13MHz,抽取因子为 24x |

| fADC = 1500MSPS,fNCO = 32.13MHz,抽取因子为 24x |

| fADC = 1500MSPS,fNCO = 32.13MHz,抽取因子为 24x |

| fADC = 1500MSPS,fNCO = 32.抽取因子为 24x |

| fADC = 1500MSPS,fNCO = 32.13MHz,抽取因子为 24x |

| 差分振幅误差 = PIN(DSA 设置 - 1)- PIN(DSA 设置)+ 1 |

| 积分振幅误差 = PIN(DSA 设置)- PIN(DSA 设置 = 0)+(DSA 设置) |

| 差分相位误差 = PhaseIN(DSA 设置 - 1)- PhaseIN(DSA 设置) |

| 积分相位误差 = Phase(DSA 设置)- Phase(DSA 设置 = 0) |

| fNCO = 400MHz |

| fNCO = 400MHz |

| fNCO = 400MHz |

| fOFFSET = 50MHz |