ZHCADI9 December 2023 TMS320F280023C , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28P650DK

5.2 基于硬件的方案

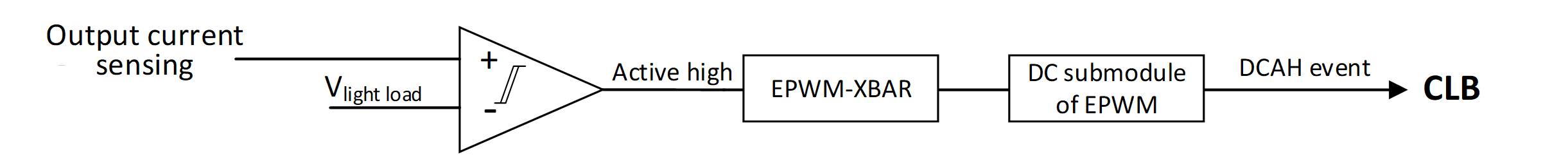

以下建议的基于硬件的方案实现了针对 SR PWM 的更快控制响应。包含由 EPWM 的 DC 子模块创建的数字比较 (DC) 事件,有助于在 CLB 的多个输入信号之间创建 CMPSS 和 CLB 模块之间的链路。图 4-2 显示了输出电流信号被馈入 CMPSS 中,Vlight_load 是指用于打开或关闭 SR PWM 的负载电流阈值。图 2-3 显示了选择作为 CLB2 的输入信号 IN5 的 DCAH 事件。使用来自 CMPSS 输出的高电平有效逻辑,当负载增加大于 Vlight_load 设置的负载阈值时,DCAH 事件变为逻辑 1。只要负载从轻负载变为重负载,SR PWM 就会导通。图 4-2 显示了用于 SR 开/关控制的 CMPSS 示例代码。

注: 激活数字滤波器,以便清除阈值负载条件附近的瞬态并具有足够的迟滞。

图 5-1 具有负载电流检测功能的基于硬件的 SR 控制

图 5-1 具有负载电流检测功能的基于硬件的 SR 控制XBAR_setEPWMMuxConfig(XBAR_TRIP10,XBAR_EPWM_MUX02_CMPSS2_CTRIPH);

XBAR_enableEPWMMux(XBAR_TRIP10, XBAR_MUX02);

// Enable CMPSS2 and configure the negative input signal to come from the DAC

//

CMPSS_enableModule(CMPSS2_BASE);

CMPSS_configHighComparator(CMPSS2_BASE, CMPSS_INSRC_DAC);

// Set DAC reference level, refers to 6A

//

CMPSS_setDACValueHigh(CMPSS2_BASE, 112);

CMPSS_configDAC(CMPSS2_BASE, CMPSS_DACREF_VDDA);

// Enable the digital filter

CMPSS_configFilterHigh(CMPSS2_BASE,1,150,149);

CMPSS_initFilterHigh(CMPSS2_BASE);

CMPSS_configOutputsHigh(CMPSS2_BASE, CMPSS_TRIP_FILTER);

CMPSS_setHysteresis(CMPSS2_BASE,4);

EPWM_selectDigitalCompareTripInput(EPWM2_BASE,

EPWM_DC_TRIP_TRIPIN10,

EPWM_DC_TYPE_DCAH);