ZHCADI9 December 2023 TMS320F280023C , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28P650DK

3 导通延迟配置

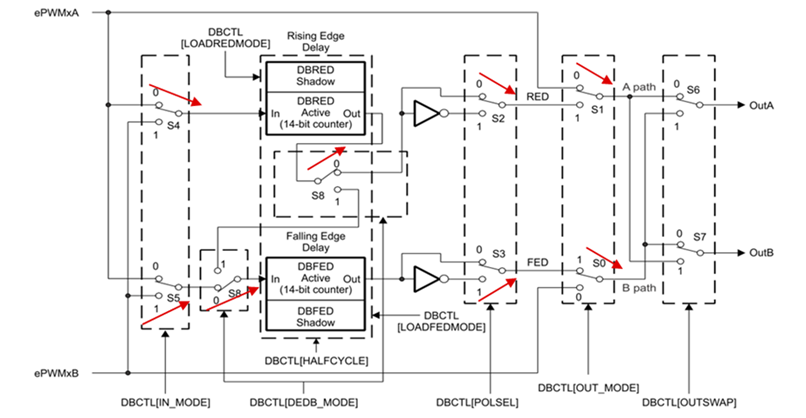

对于大多数应用,用户相对于初级侧 PWM 添加 SR PWM 的导通延迟,并且可以使用 DB 子模块。但是,只有上升沿延迟可以通过 DB 子模块直接针对 AQ 信号 (EPWM2A) 启用。因此,为了进一步利用 EPWM2B AQ 信号的下降沿延迟块,应为原始 AQ 输出创建反极性信号,并在为 DB 子模块添加下降沿延迟后使信号反转。图 3-1 中显示了详细配置,并添加了红色箭头。这些配置允许用户分别根据 SR PWM、EPWM2A 和 EPWM2B 的 DB 子模块的现有上升沿和下降沿延迟添加导通延迟。

图 3-1 死区子模块配置

图 3-1 死区子模块配置