ZHCACF6A february 2021 – march 2023 TMS320F2800132 , TMS320F2800133 , TMS320F2800135 , TMS320F2800137 , TMS320F2800152-Q1 , TMS320F2800153-Q1 , TMS320F2800154-Q1 , TMS320F2800155 , TMS320F2800155-Q1 , TMS320F2800156-Q1 , TMS320F2800157 , TMS320F2800157-Q1 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384D-Q1 , TMS320F28384S , TMS320F28384S-Q1 , TMS320F28386D , TMS320F28386D-Q1 , TMS320F28386S , TMS320F28386S-Q1 , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

2.5 采样率和源阻抗与跟踪误差之间的关系

基于高速运算放大器的 ADC 信号调节电路的设计人员需要权衡建立速度与运算放大器带宽和外部元件尺寸。源电容值满足电荷共享标准可确保,无论源阻抗如何,都可以使用最小 ADC S+H 窗口持续时间。然而,这会产生需要优化的新权衡:采样率和源阻抗与跟踪误差。

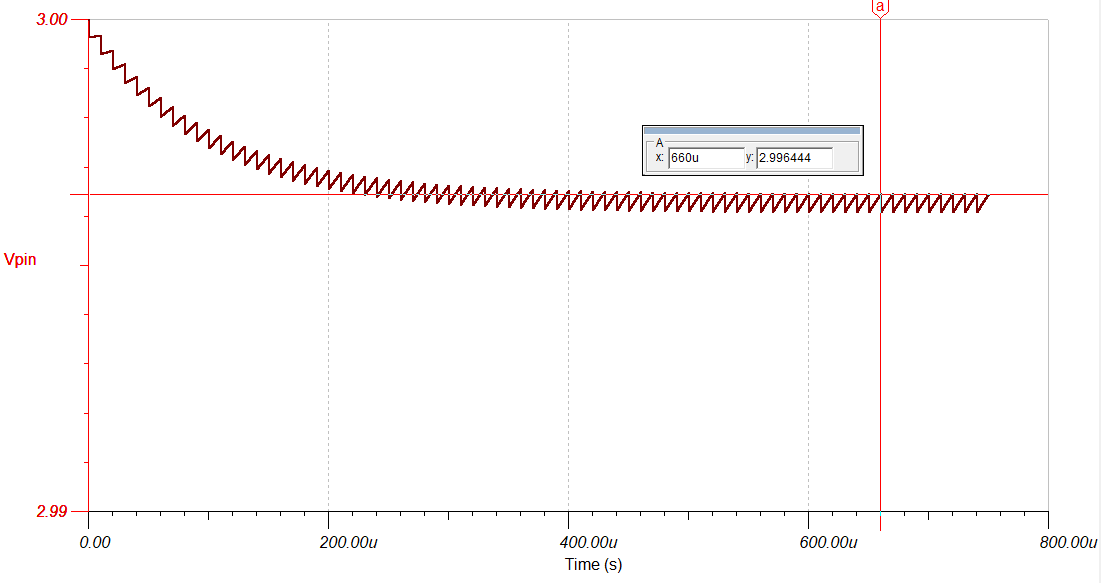

当 ADC 采样速度相对于电源在采样间隔时间内通过 Rs 对 Cs 充电的能力而言过快时,会在样本之间发生显著的跟踪误差。可以通过对电路进行仿真来说明这一点,如图 2-3 所示。图 2-4 显示了该仿真的结果:锯齿波形中的每次降压都是由于 ADC 采样引起的电荷均衡。在这种情况下,第一次采样会使引脚上的电压下降约 0.5LSB,从而实现良好的直流输入电压采样。然而,在进行下一次采样之前,外部电源只能部分地为 Cs 充电。后续的每次采样都会释放 Cs 上的部分电荷。最终,当引脚电压和源电压之间的差值增加到足以在采样间隔时间内驱动 0.5LSB 的恢复时,就会达到平衡。在图 2-4 的仿真结果中,在大约 3.5mV 的跟踪误差下达到平衡。

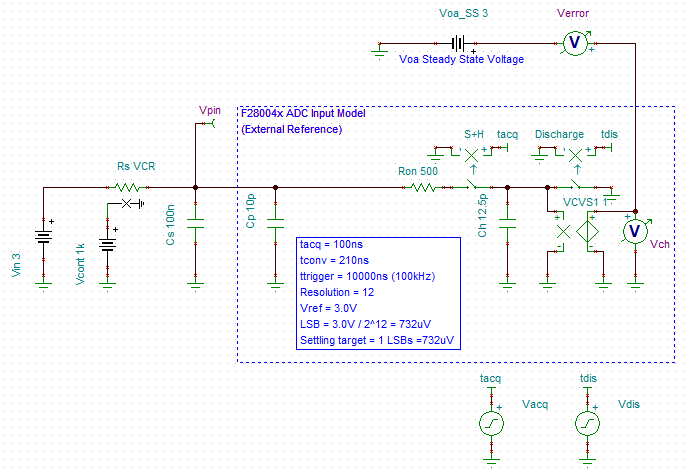

图 2-3 具有 1kΩ Rs 和 100kHz 采样率的 ADC 输入电路

图 2-3 具有 1kΩ Rs 和 100kHz 采样率的 ADC 输入电路 图 2-4 1kΩ Rs 和 100kHz 采样率的仿真结果

图 2-4 1kΩ Rs 和 100kHz 采样率的仿真结果建立误差目标通常设置为 0.5LSB,但应用可能允许更大或更小的建立误差。如果采用 1LSB 的目标建立误差,则前面的示例电路仍然远超出目标范围,该示例电路具有 0.5LSB 的电荷共享误差加上 3.5mV(约 5LSB)的跟踪误差。要使跟踪误差处于容差范围之内,需要降低采样率或降低源阻抗 Rs(或同时降低这两者)。

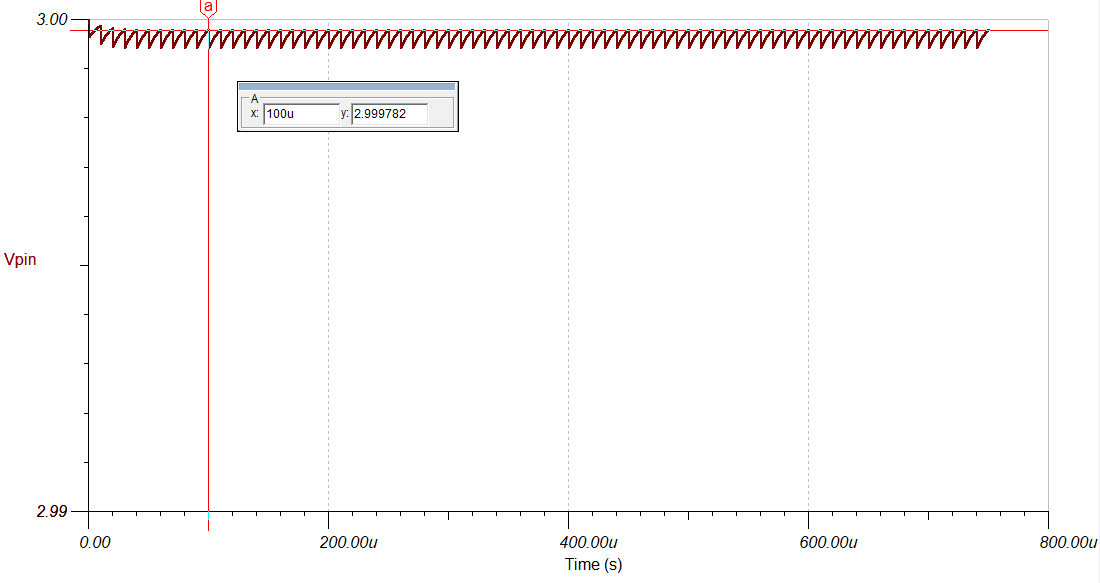

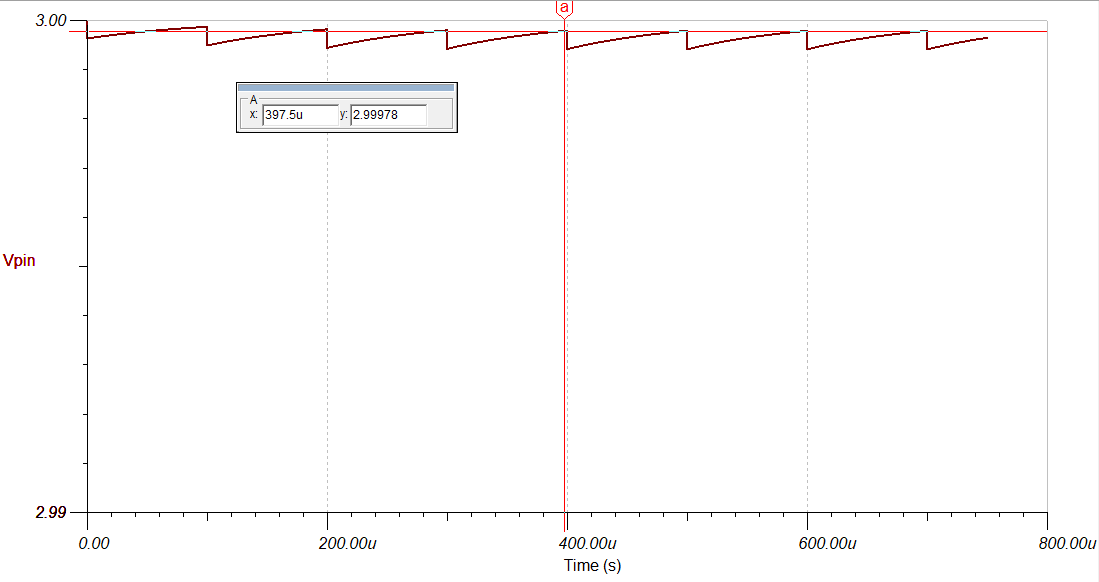

图 2-5 和图 2-6 表明,通过显著降低源阻抗或采样率,可以使跟踪误差与电荷均衡误差的大小相似,从而使总体建立误差处于 1LSB 的目标范围之内。

图 2-5 100Ω Rs 和 100kHz 采样率的仿真结果

图 2-5 100Ω Rs 和 100kHz 采样率的仿真结果 图 2-6 1kΩ Rs 和 10kHz 采样率的仿真结果

图 2-6 1kΩ Rs 和 10kHz 采样率的仿真结果