ZHCSOF3G April 2006 – July 2021 TLV320AIC3106

PRODUCTION DATA

- 1 特性

- 2 应用

- 3 说明

- 4 Revision History

- 5 说明(续)

- 6 Device Comparison Table

- 7 Pin Configuration and Functions

- 8 Specifications

- 9 Parameter Measurement Information

-

10Detailed Description

- 10.1 Overview

- 10.2 Functional Block Diagram

- 10.3

Feature Description

- 10.3.1 Hardware Reset

- 10.3.2 Digital Audio Data Serial Interface

- 10.3.3 Audio Data Converters

- 10.3.4 Audio Analog Inputs

- 10.3.5 Analog Fully Differential Line Output Drivers

- 10.3.6 Analog High Power Output Drivers

- 10.3.7 Input Impedance and VCM Control

- 10.3.8 General-Purpose I/O

- 10.3.9 Digital Microphone Connectivity

- 10.3.10 Micbias Generation

- 10.3.11 Short Circuit Output Protection

- 10.3.12 Jack/Headset Detection

- 10.4 Device Functional Modes

- 10.5 Programming

- 10.6 Register Maps

- 11Application and Implementation

- 12Power Supply Recommendations

- 13Layout

- 14Device and Documentation Support

封装选项

请参考 PDF 数据表获取器件具体的封装图。

机械数据 (封装 | 引脚)

- RGZ|48

- ZXH|80

散热焊盘机械数据 (封装 | 引脚)

- RGZ|48

订购信息

3 说明

TLV320AIC3106 是一款低功耗立体声音频编解码器,具有立体声耳机放大器以及在单端或全差分配置下可编程的多个输入和输出。包括基于寄存器的全面电源控制,可实现立体声 48kHz DAC 回放,在 3.3V 模拟电源电压下的功耗低至 15mW,因此非常适合便携式电池供电类音频和电话应用。

TLV320AIC3106 的录音路径包含集成式麦克风偏置、数控立体声麦克风前置放大器和自动增益控制 (AGC),并在多个模拟输入中提供混频器/多路复用器功能。在录音过程中可使用可编程滤波器,滤除在数码相机光学变焦期间可能产生的可闻噪声。

器件信息(1)

| 器件型号 | 封装 | 封装尺寸(标称值) |

|---|---|---|

| TLV320AIC3106 | BGA MICROSTAR JUNIOR (80) | 5.00mm x 5.00mm |

| VQFN (48) | 7.00mm x 7.00mm |

(1) 如需了解所有可用封装,请见数据表末尾的可订购产品附录。

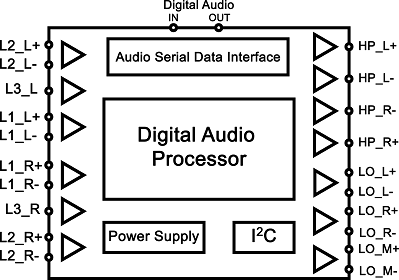

简化版图表

简化版图表