ZHCSR43 December 2023 LMK5C33216A

PRODUCTION DATA

- 1

- 1 特性

- 2 应用

- 3 说明

- 4 引脚配置和功能

- 5 规格

- 6 参数测量信息

-

7 详细说明

- 7.1 概述

- 7.2 功能方框图

- 7.3

特性说明

- 7.3.1 振荡器输入 (XO)

- 7.3.2 基准输入

- 7.3.3 时钟输入连接和端接

- 7.3.4 基准输入多路复用器选择

- 7.3.5 无中断切换

- 7.3.6 基准输入上的间隙时钟支持

- 7.3.7 输入时钟和 PLL 监控、状态和中断

- 7.3.8

PLL 关系

- 7.3.8.1 PLL 频率关系

- 7.3.8.2 模拟 PLL(APLL1、APLL2、APLL3)

- 7.3.8.3 APLL 参考路径

- 7.3.8.4 APLL 相位频率检测器 (PFD) 和电荷泵

- 7.3.8.5 APLL 反馈分频器路径

- 7.3.8.6 APLL 环路滤波器(LF1、LF2、LF3)

- 7.3.8.7 APLL 压控振荡器(VCO1、VCO2、VCO3)

- 7.3.8.8 APLL VCO 时钟分配路径

- 7.3.8.9 DPLL 基准 (R) 分频器路径

- 7.3.8.10 DPLL 时间数字转换器 (TDC)

- 7.3.8.11 DPLL 环路滤波器 (DLF)

- 7.3.8.12 DPLL 反馈 (FB) 分频器路径

- 7.3.9 输出时钟分配

- 7.3.10 输出通道多路复用器

- 7.3.11 输出分频器 (OD)

- 7.3.12 SYSREF/1PPS

- 7.3.13 输出延迟

- 7.3.14 时钟输出 (OUTx_P/N)

- 7.3.15 无毛刺输出时钟启动

- 7.3.16 时钟输出连接和端接

- 7.3.17 输出同步 (SYNC)

- 7.3.18 零延迟模式 (ZDM)

- 7.3.19 历时计数器 (TEC)

- 7.4 器件功能模式

- 7.5 编程

- 8 应用和实施

- 9 器件和文档支持

- 10修订历史记录

- 11机械、封装和可订购信息

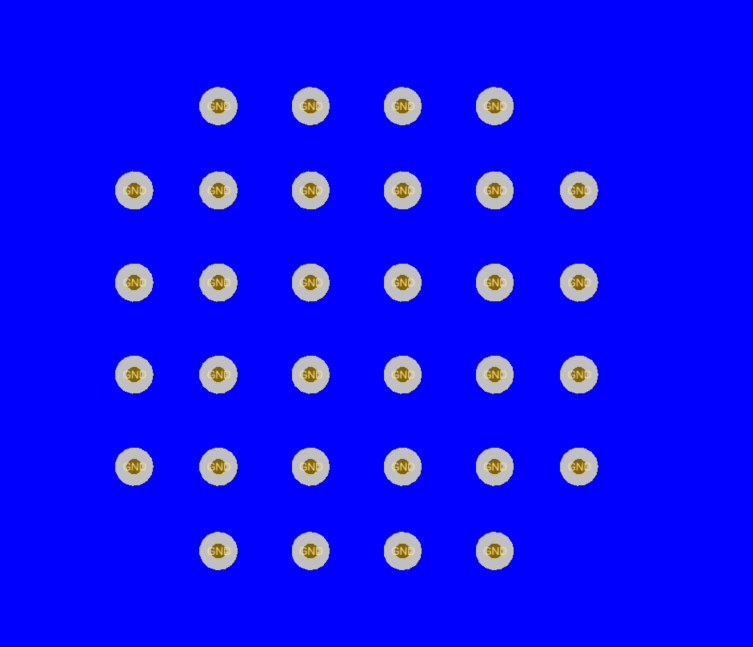

8.5.2 布局示例

以下是印刷电路板 (PCB) 布局布线示例,其中展示了热设计实践的应用以及器件 DAP 和 PCB 之间的低电感接地连接。

图 8-5 LMK5C33216A 的 PCB 布局示例,顶层.

图 8-5 LMK5C33216A 的 PCB 布局示例,顶层.  图 8-6 LMK5C33216A 的 PCB 布局示例,底层.

图 8-6 LMK5C33216A 的 PCB 布局示例,底层.