ZHCABE7A November 2021 – April 2022 PCM5120-Q1 , PCM6120-Q1 , TLV320ADC5120 , TLV320ADC6120

2 动态范围增强器

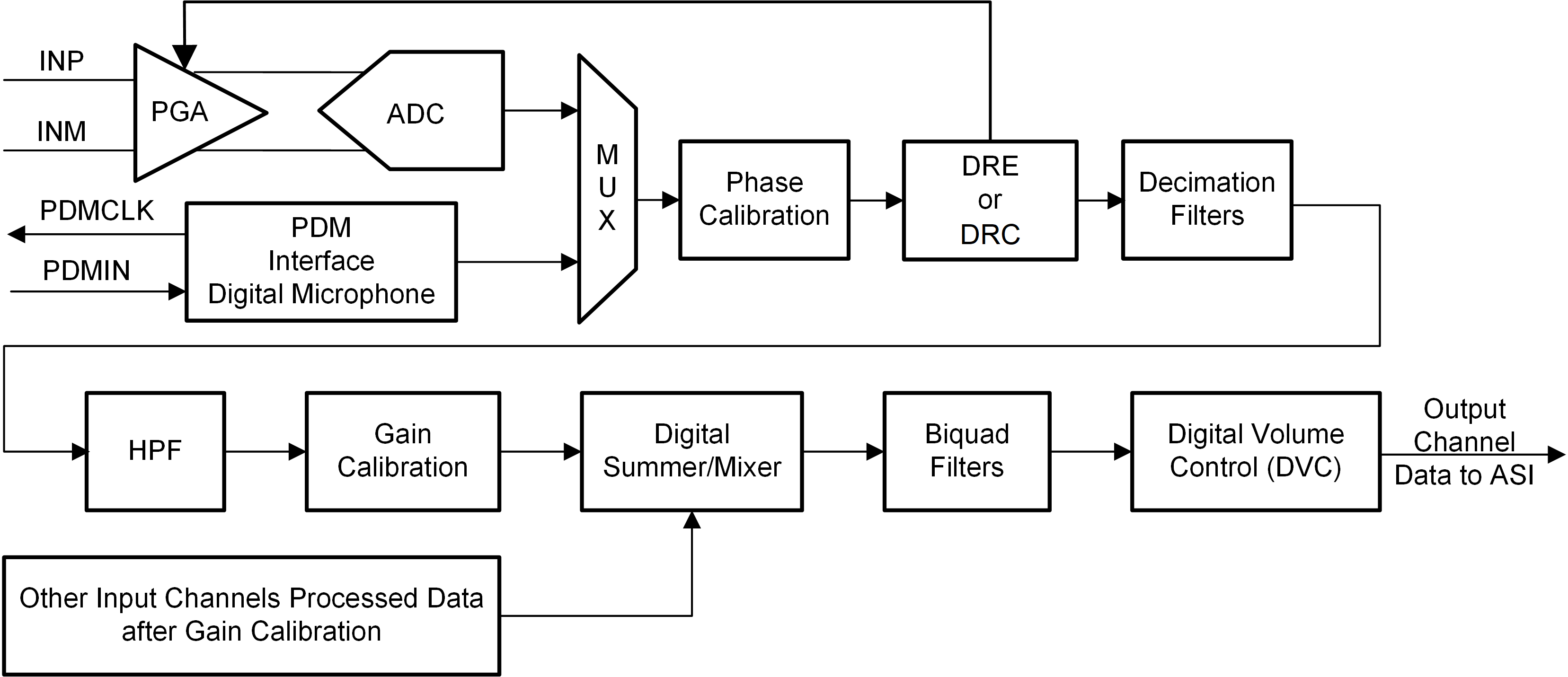

图 2-1 显示了 TLV320ADC5120/PCM5120-Q1 和 TLV320ADC6120/PCM6120-Q1 器件的信号处理链。TLV320ADC5120/PCM5120-Q1 和 TLV320ADC6120/PCM6120-Q1 器件中前端 PGA 的动态范围性能分别为 120dB 和 122dB。随后的 Δ-Σ ADC 对于 TLV320ADC5120/PCM3120-Q1 具有 108dB 动态范围,对于 TLV320ADC6120/PCM6120-Q1 具有 113dB 动态范围。在没有 DRE 的情况下,PGA 的超低噪声性能受到 ADC 性能的限制,整体通道动态范围由 ADC 的动态范围决定。在没有 DRE 的情况下,可以提高整体通道的动态范围超过 ADC 的动态范围,会更多地受到 PGA 动态范围的限制。

图 2-1 信号处理方框图

图 2-1 信号处理方框图DRE 算法监测输入信号,对低于阈值的信号电平增加模拟 PGA 的增益。同时,DRE 算法在数字电路中产生相应的倒数衰减,因此模拟 PGA 增益和数字衰减的净效应相互抵消。因此,DRE 可以在不增加整体通道增益的情况下扩大动态范围。DRE 不会获得超过阈值的信号。提升模拟低电平信号可使 ADC 的输入显著高于其本底噪声,从而防止 ADC 性能成为限制因素。后续处理使用了高性能 32 位数字信号处理器,具有非常低的量化噪声,因此 PGA 性能成为整体通道性能的限制因素。TLV320ADC5120/PCM5120-Q1 和 TLV320ADC6120/PCM6120-Q1 器件支持多达四个模拟输入通道。所有模拟输入通道都支持 DRE。这些器件支持来自模拟麦克风源或辅助线路输入的差分或单端信号。模拟麦克风输入支持驻极体电容器和微机电 (MEMS) 麦克风。尽管这些器件还支持数字脉冲密度调制 (PDM) 数字麦克风,但由于数字麦克风的模拟增益无法控制, DRE/DRC 不支持数字通道。TLV320ADCx120/PCMx120-Q1 系列器件还支持模拟通道上的自动增益控制 (AGC) 算法,以保持恒定的标称输出电平。无法同时使用 AGC、DRE 和 DRC 算法,因为所有这些算法都控制 PGA。可以使用 DSP_CFG1 寄存器(页面 = 0x00,地址 = 0x6C)的 AGC_DRE_SEL 位来选择 DRE 或 AGC,如表 2-1 所示。

| 位 | 字段 | 类型 | 复位 | 说明 |

|---|---|---|---|---|

| 3 | DRE_AGC_SEL | R/W | 0h | 当启用了任何通道时,选择 DRE 或 AGC。 0d = 选择 DRE。 1d = 选择 AGC。 |