ZHCAA83A May 2016 – April 2021 ADC32RF45 , LMX2582 , LMX2592

2 了解相位噪声和抖动以及 SNR

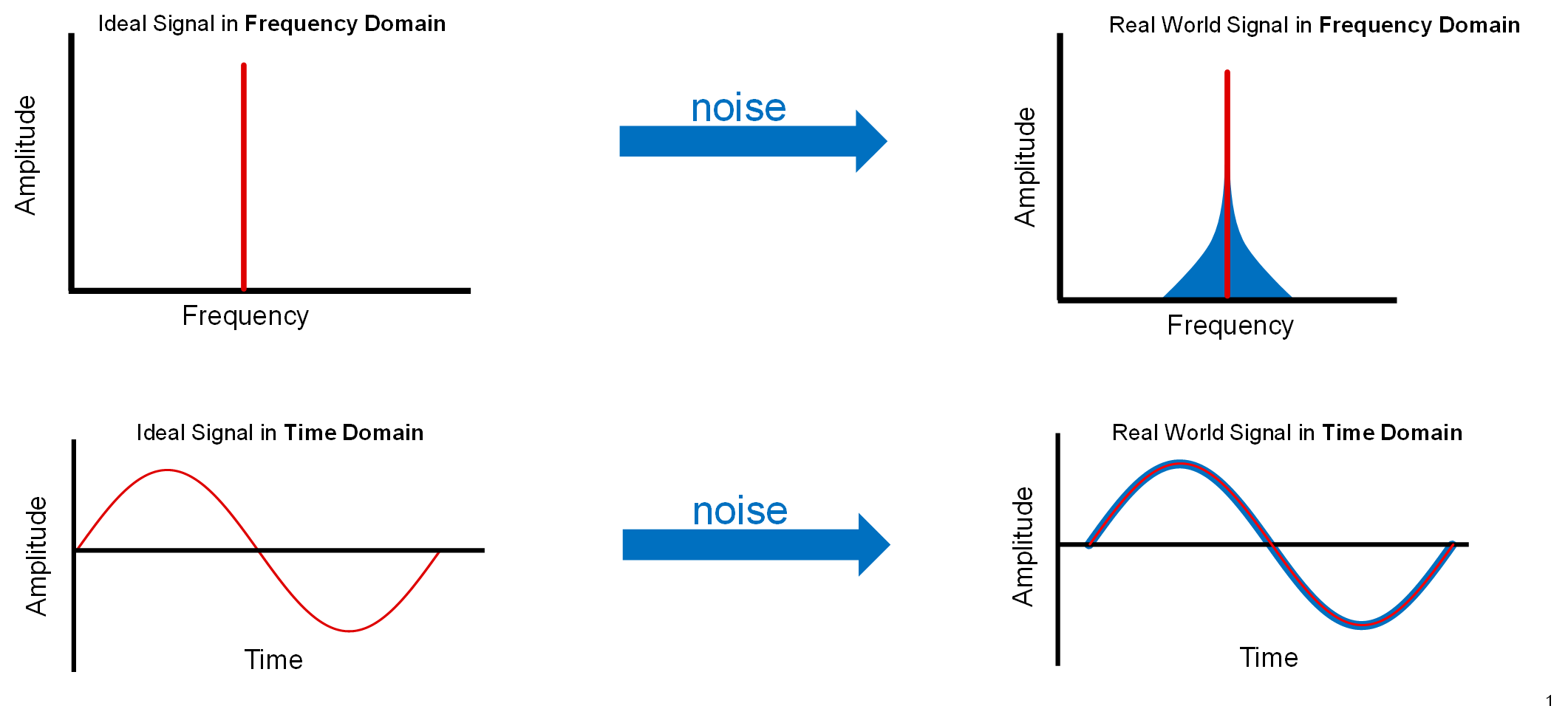

若要设计和找出超低的抖动,首先需要了解合成器时钟信号的相位噪声。图 2-1在时域中,理想的正弦波时钟信号看起来就像 左下角的波形。实际上,由于现实生活中频率合成器的器件不完善,因此会产生额外的噪声,从而使波形偏离其理想位置。同样道理,转换为频域的同一正弦波在振荡频率下是单个脉冲。噪声的增加以相位噪声的形式(理想脉冲旁的裙边)出现。Topic Link Label3合成器的低相位噪声表明信号更纯净,提供更好的性能,并最终在 ADC 计时中具有较低的抖动(在中讨论)。

图 2-1 频域和时域中的相位噪声

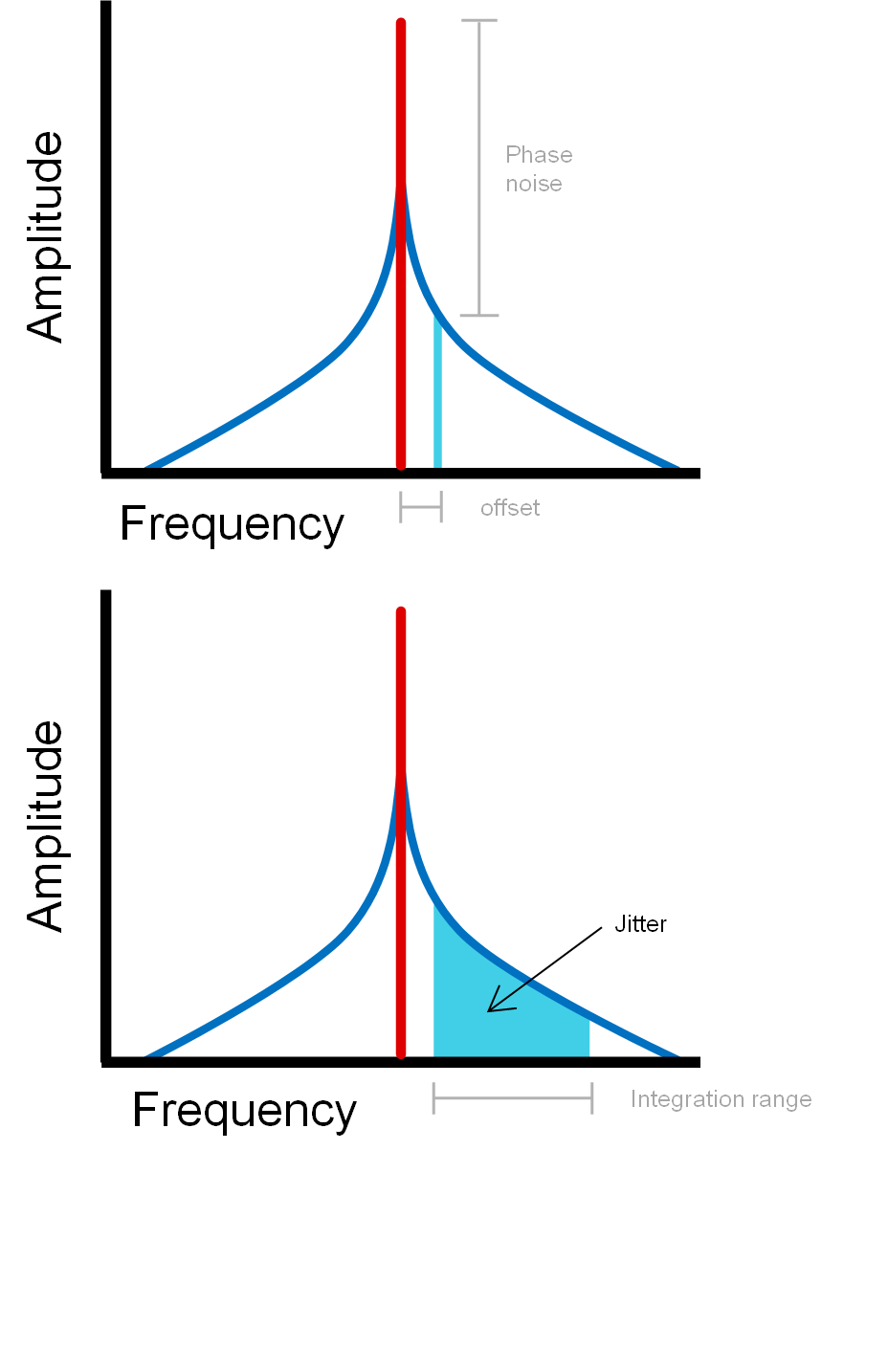

图 2-1 频域和时域中的相位噪声相位噪声 的定义是振荡信号的噪声(相对于振荡信号的偏移频率,带宽为 1Hz)与信号幅度之比。图 2-2积分噪声本质上是在相对于振荡信号的规定偏移频率范围内的所有相位噪声之和(请参阅)。Equation2抖动是使用积分噪声和信号频率从 得出的:

Equation2.

选择的积分范围很重要。这取决于 ADC 的采样设置。底部范围(更接近振荡信号)由 [采样率]/[FFT 大小] 的一半定义。https://www.ti.com/lit/pdf/SLYT379例如,在采样率为 2949.12MHz 且 FFT 大小为 65536 时,积分下降到 22.5kHz(请参阅 SLYT379 以了解更多信息)。因此,积分范围的这一下限越低,在较低偏移处的相位噪声就越重要。

图 2-2 相位噪声和抖动定义

图 2-2 相位噪声和抖动定义