SPRAD65 December 2022 TDA4VM , TDA4VM-Q1

1.6 Memory Segment Management

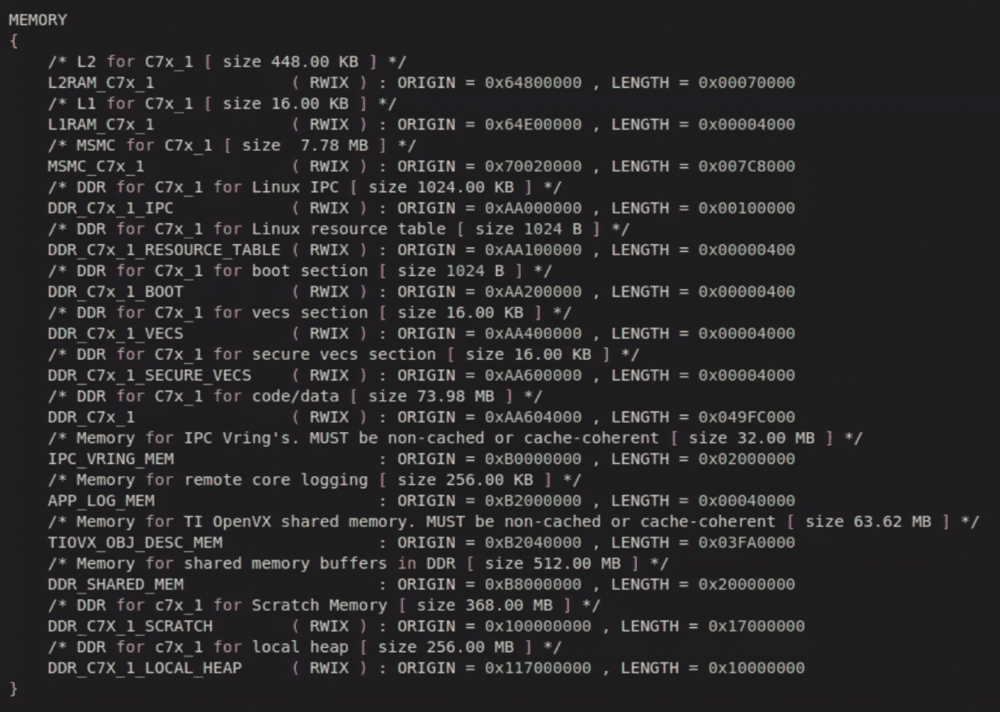

TDA4X is a multi-core heterogeneous SOC, multiple cores share the same DDR, and the 32-bit processor can only access the low 2GB 0x0000_8000_0000~ 0x0000_FFFF_FFFF space, such as R5F, C66, and so forth. But 64-bit processors can access the full memory space, such as A72, C7X. In order to avoid conflicts in memory usage, you need to divide and manage the DDR memory space. In the SDK, the memory of each processor is divided and managed through python scripts. For details, see ti-processor-sdk-rtos-j721e-evm-08_04_00_02/vision_apps/platform/j721e/rtos/gen_linker_mem_map.py,The memory management of A72 is not in this document. If the A72 runs Linux, the memory management is set in DTS. Reference documentation for the use of memory management tools Understanding and updating SDK memory map for J721E. The memory segment of C7X DSP is divided as follows:

Figure 1-4 C7X Memory Map

Figure 1-4 C7X Memory Map