SLVUCF4 August 2022

PRODUCTION DATA

2 EVM Connectors and Test Points

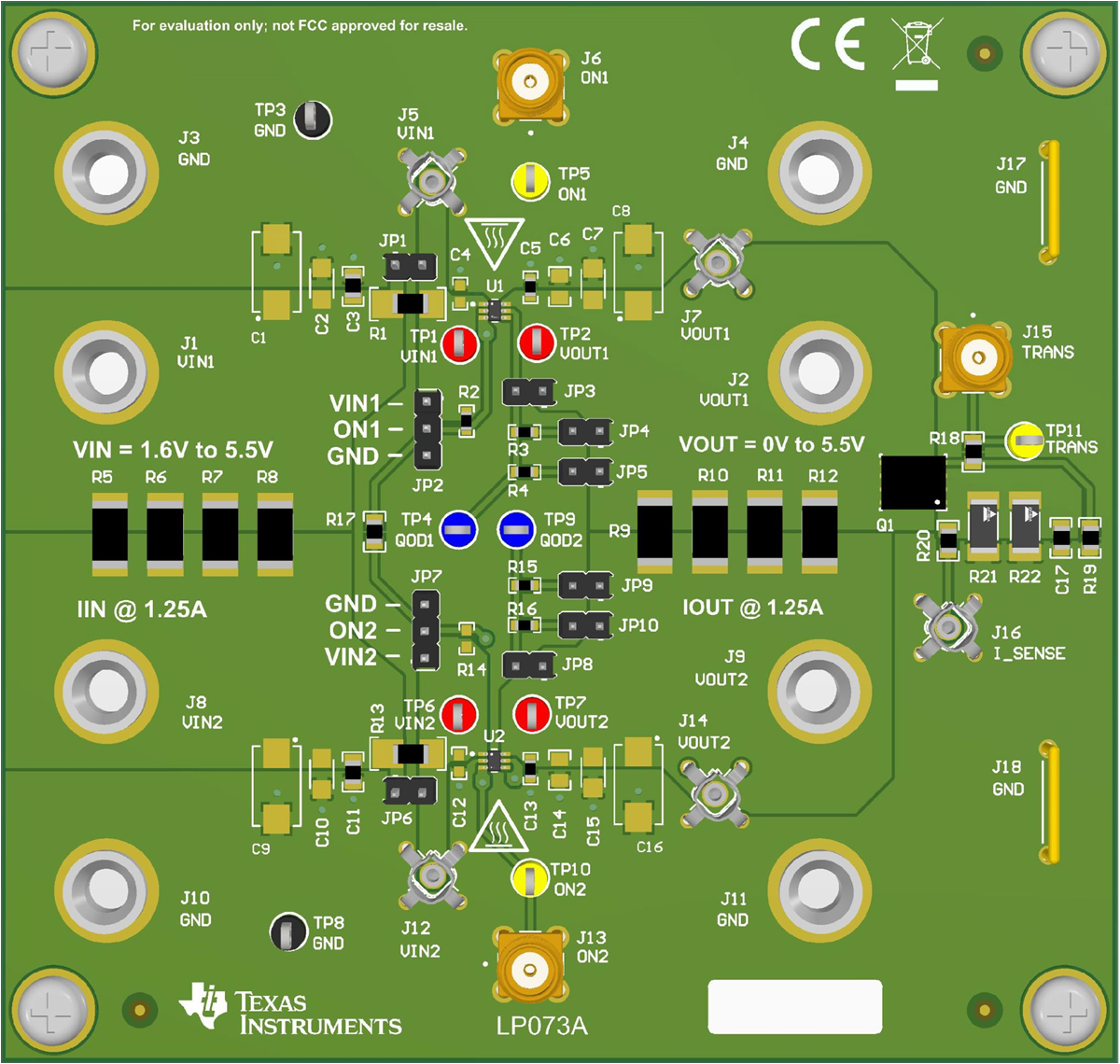

Figure 2-1 TPS7H2221EVM 3D Rendering

(Top)

Figure 2-1 TPS7H2221EVM 3D Rendering

(Top)Table 2-1 Summary of Connectors and Test Points

| Connector or Jumper | Test Point | Function | |

|---|---|---|---|

| J1 | J5, TP1 | VIN1 | Input Power for Board |

J8 | J12, TP6 | VIN2 | |

| J2 | J7, TP2 | VOUT1 | Output Power for Board |

J9 | J14, TP7 | VOUT2 | |

J3, J4, J10, J11 | J17, J18, TP3, TP8 | GND | Ground |

J6, JP2 | TP5 | ON1 | ON Pin |

J13, JP7 | TP10 | ON2 | |

JP3, JP4, JP5 | TP4 | QOD1 | QOD Pin |

JP8, JP9, JP10 | TP9 | QOD2 | |

| J15 | TP11 | TRANS | Output Transient FET Gate Signal |

N/A | J16 | I_SENSE | Output Transient Current Sense Test Point |