SLUUCK3 November 2021

4.1 Input/Output Connections

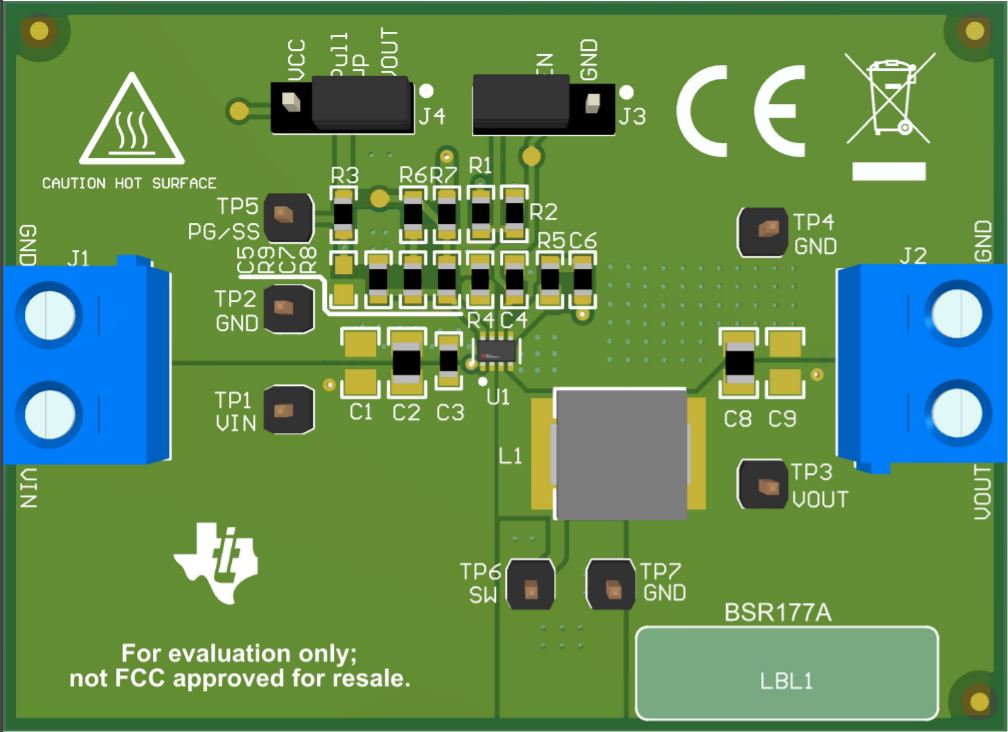

The TPS563212EVM is provided with input and output connectors and test points as shown in Table 4-1. Figure 4-1 shows connectors and jumpers placement on TPS563212EVM board.

A power supply capable of supplying 3 A must be connected to J1 through a pair of 20-AWG wires. The load must be connected to J2 through a pair of 20-AWG wires. The maximum load current capability is 3 A. Wire lengths must be minimized to reduce losses in the wires. Test point TP1 provides a place to monitor the VIN input voltages with TP2 providing a convenient ground reference. TP3 is used to monitor the output voltage with TP4 as the ground reference.

Figure 4-1 Connectors and Jumpers Placement

Figure 4-1 Connectors and Jumpers PlacementTable 4-1 Connection and Test Points

| REFERENCE DESIGNATOR | FUNCTION |

|---|---|

| J1 | VIN (see Table 1-1 for VIN range) |

| J2 | VOUT, 3.3 V at 3 A maximum |

| J3 | EN control. Shunt EN to GND to disable. |

| J4 | Source selection for PGOOD |

| TP1 | VIN positive power point |

| TP3 | VOUT positive monitor point |

| TP2, TP4, TP7 | GND monitor point |

| TP5 | Test point for PG/SS measurment |

| TP6 | Switch node test point |