SBAU412A November 2022 – May 2024 AFE7900 , AFE7903 , AFE7906 , AFE7920 , AFE7921 , AFE7950

- 1

- Abstract

- Trademarks

- 1 Introduction

- 2 Prerequisites

- 3 Typical Bare-Metal Design Flow

- 4 Background

- 5 Add Microblaze and SPI IP for Use in Vitis for Embedded Development

- 6 Create New Platforms in Vitis

- 7 Create New Application Projects in Vitis

- 8 Build Application Projects

- 9 Generate SPI Log for AFE79xx EVM

- 10AFE79xxEVM Board Modifications

- 11Configure the AXI GPIO

- 12Configure the AXI SPI

- 13Set Up and Power on Hardware

- 14Set up ZCU102 Board Interface for VADJ_FMC

- 15Debug Application Projects and Set up Vitis Serial Terminal

- 16Execute the Application

- 17Revision History

15 Debug Application Projects and Set up Vitis Serial Terminal

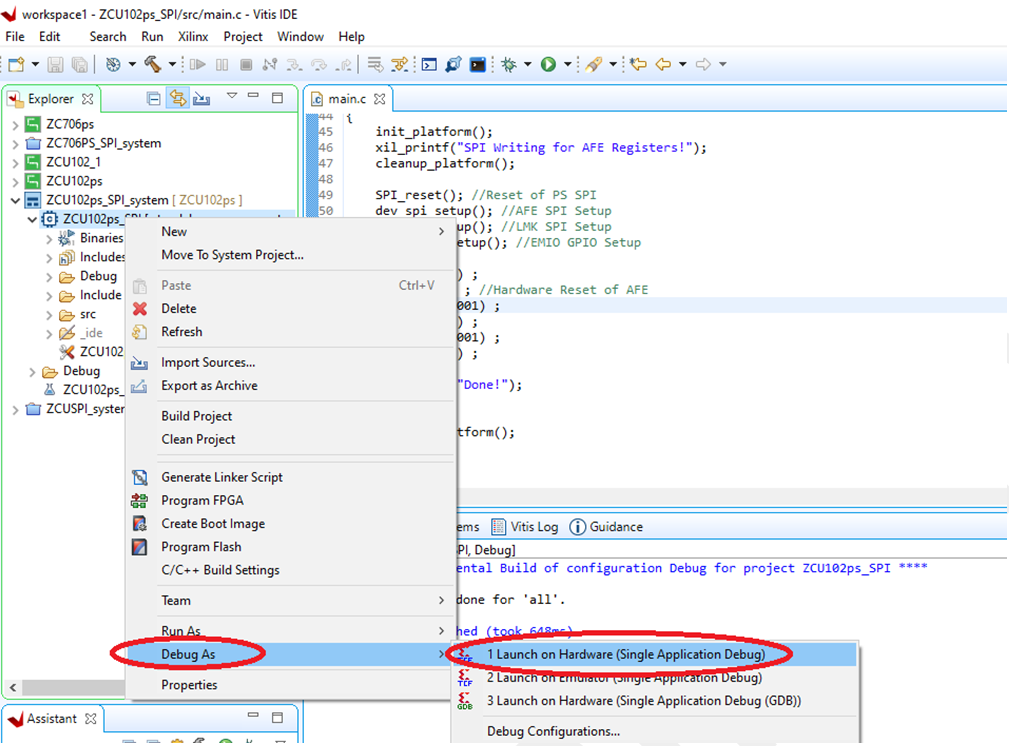

To debug the application project and set up the Vitis serial terminal. follow these steps:

- Right-click the project name and

go to Debug As from the drop-down menu. Click Launch on Hardware

(Single Application Bug) to run the debug (see Figure 15-1).

Figure 15-1 Debugging Application

Project

Figure 15-1 Debugging Application

Project - Connect

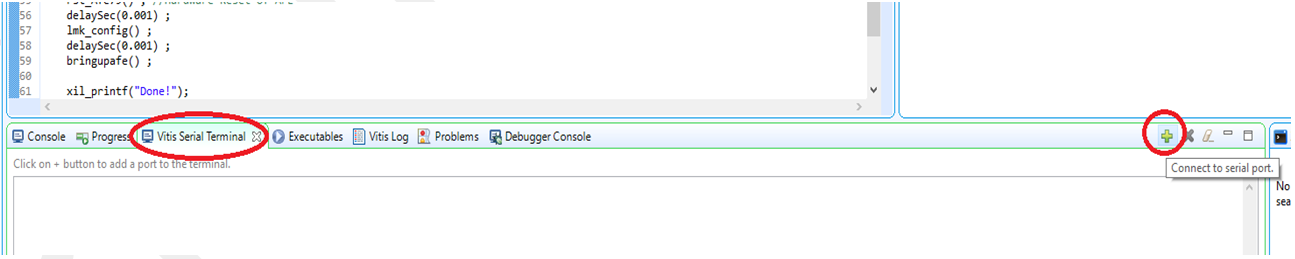

the Vitis Serial terminal (see Figure 15-2) with baudrate 115200 (this can be used to see SPI write or read status).

Figure 15-2 Vitis Serial

Terminal

Figure 15-2 Vitis Serial

Terminal