ZHCSDM4D december 2014 – may 2023 TPS65263-Q1

PRODUCTION DATA

- 1

- 1 特性

- 2 应用

- 3 说明

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3

Feature Description

- 7.3.1 Adjusting the Output Voltage

- 7.3.2 Enable and Adjusting UVLO

- 7.3.3 Soft-Start Time

- 7.3.4 Power-Up Sequencing

- 7.3.5 V7V Low-Dropout Regulator and Bootstrap

- 7.3.6 Out-of-Phase Operation

- 7.3.7 Output Overvoltage Protection (OVP)

- 7.3.8 PSM

- 7.3.9 Slope Compensation

- 7.3.10 Overcurrent Protection

- 7.3.11 Power Good

- 7.3.12 Thermal Shutdown

- 7.4 Device Functional Modes

- 7.5 Register Maps

- 8 Application and Implementation

- 9 Device and Documentation Support

- 10Mechanical, Packaging, and Orderable Information

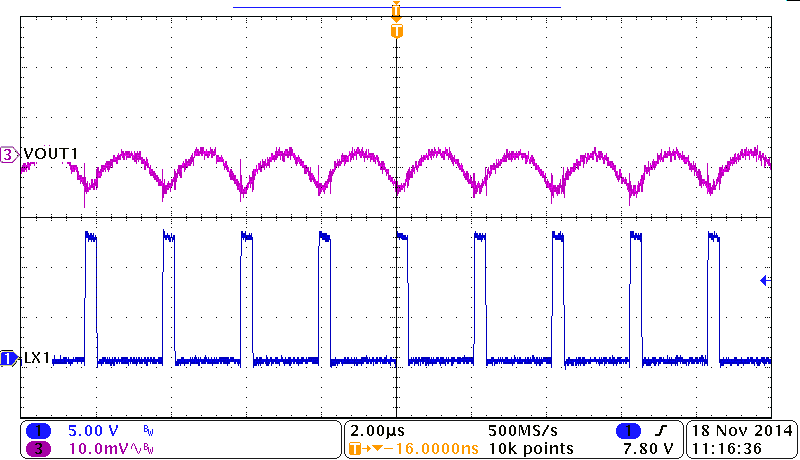

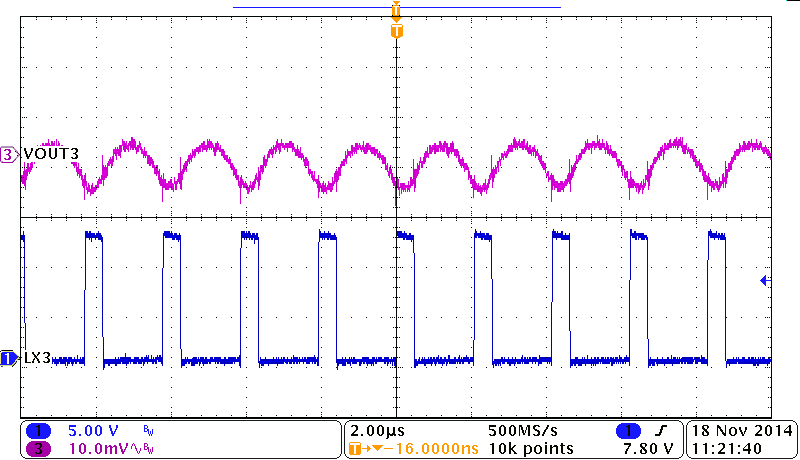

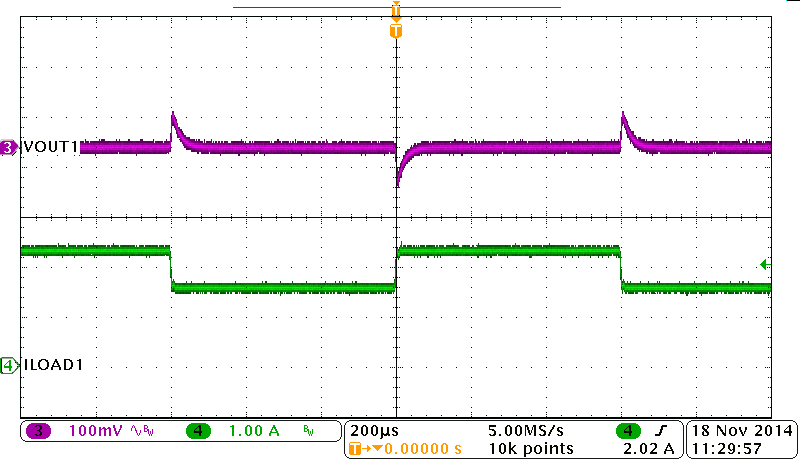

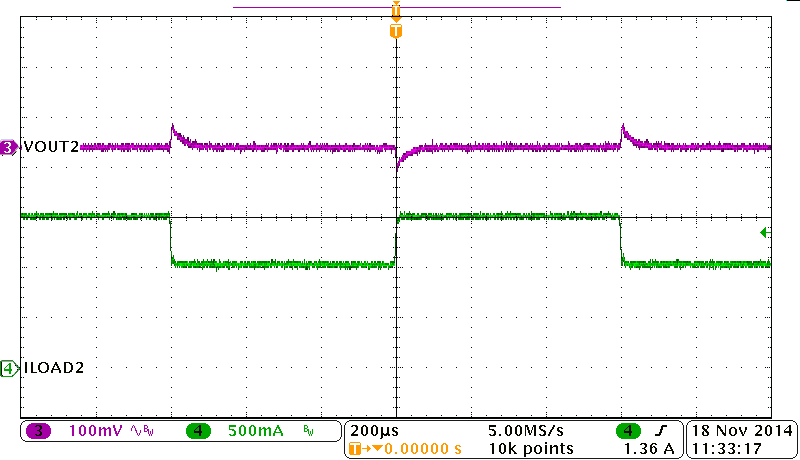

8.2.3 Application Curves

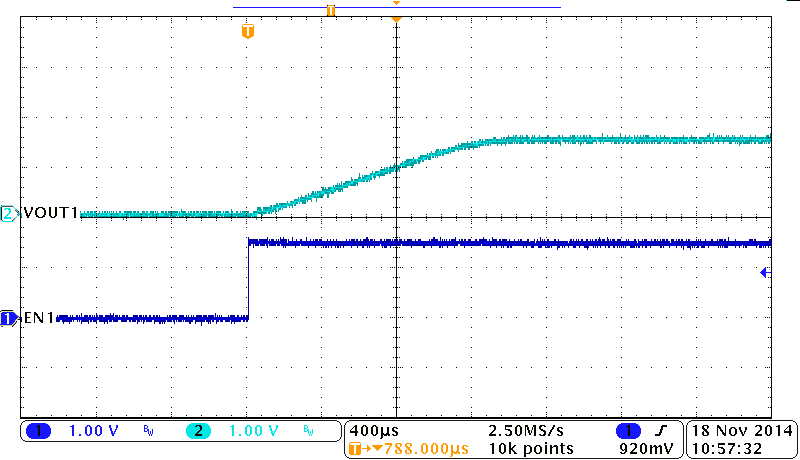

| Iout = 3 A |

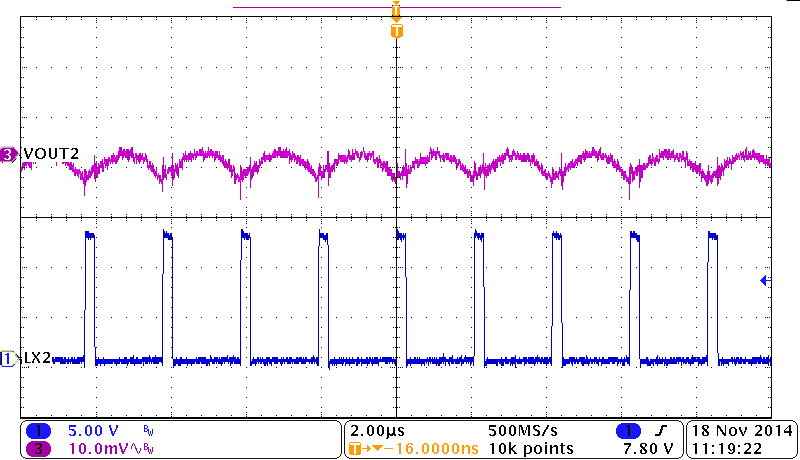

| Iout = 2 A |

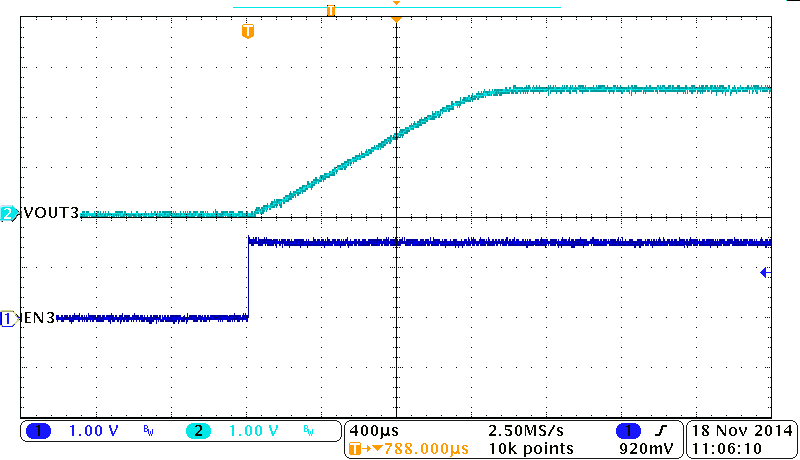

| Iout = 2 A |

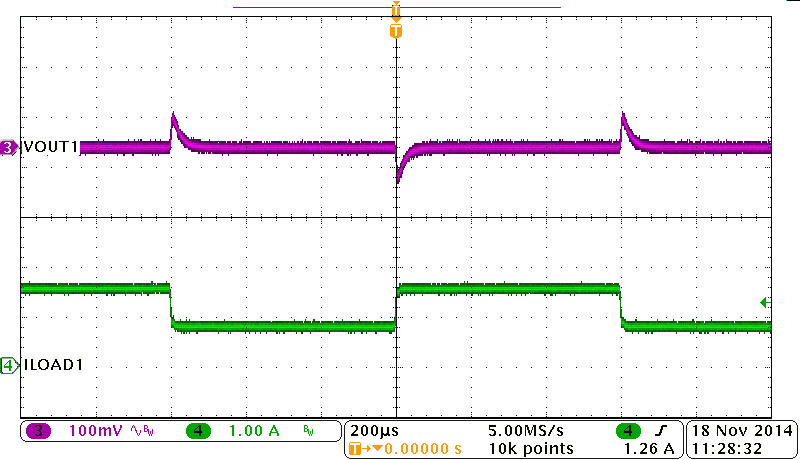

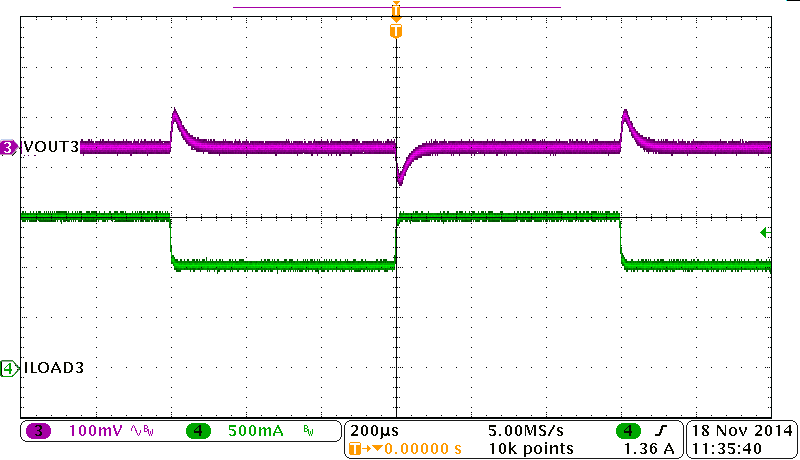

| 0.75 to 1.5 A | SR = 0.25 A/µs |

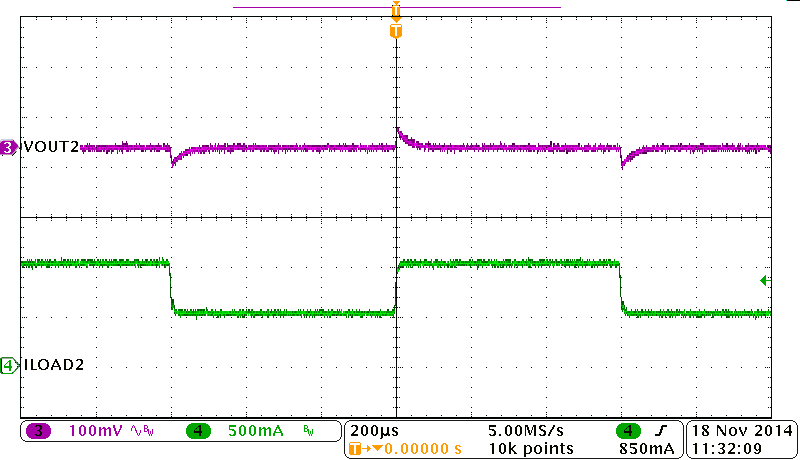

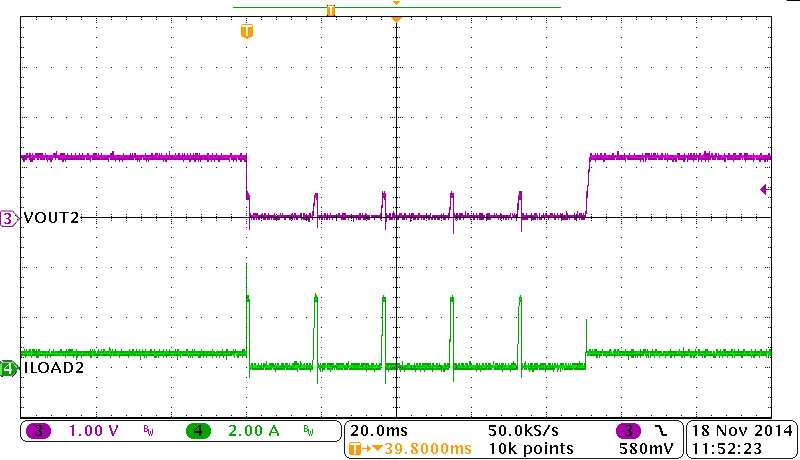

| 0.5 to 1.0 A | SR = 0.25 A/µs |

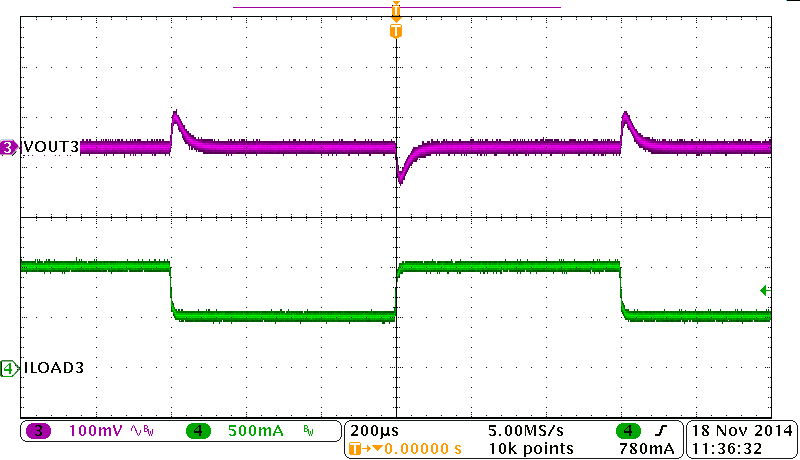

| 0.5 to 1.0 A | SR = 0.25 A/µs |

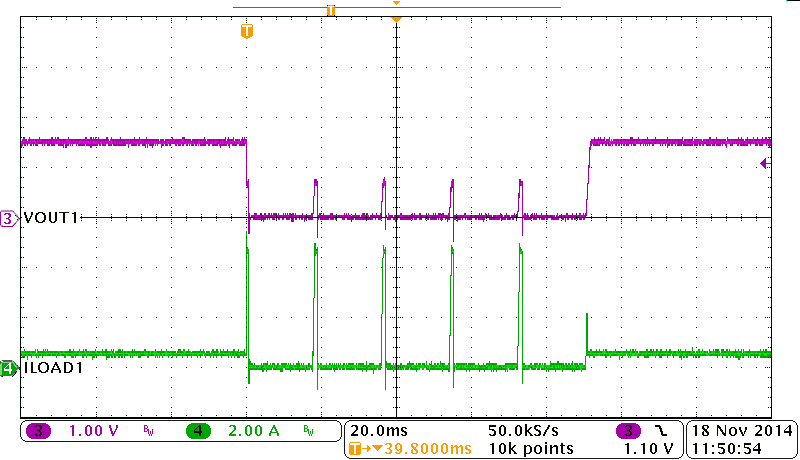

Figure 8-15 BUCK1, Hiccup and Recovery

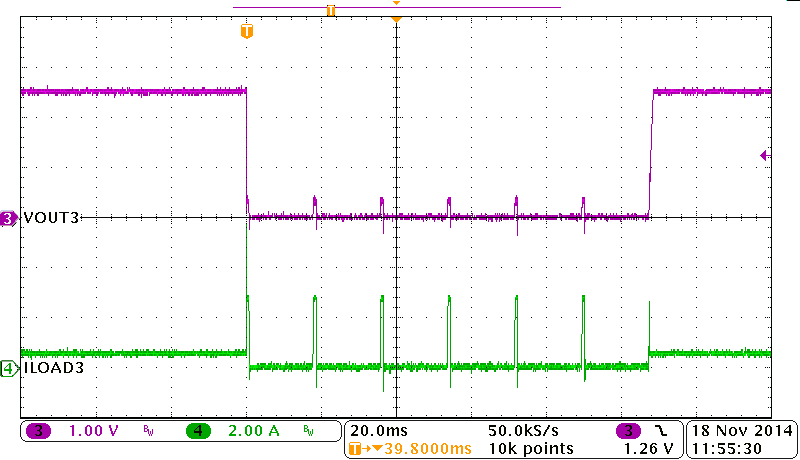

Figure 8-15 BUCK1, Hiccup and Recovery Figure 8-17 BUCK3, Hiccup and Recovery

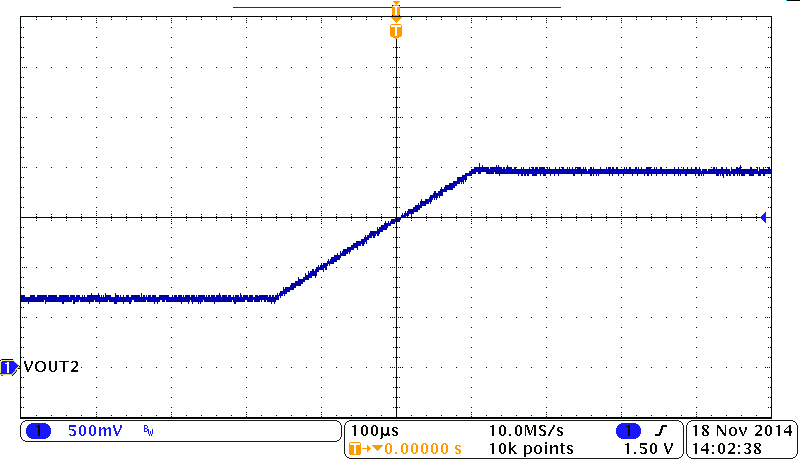

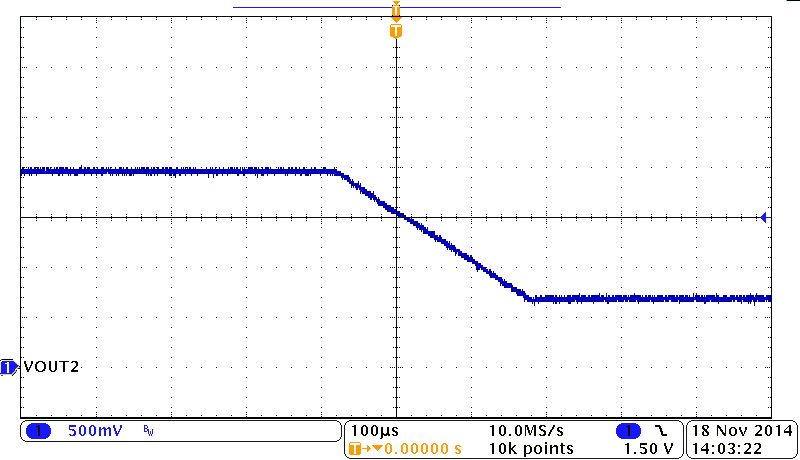

Figure 8-17 BUCK3, Hiccup and Recovery Figure 8-19 VID2

from 00 to 7F, SR = 10 mV/Cycle

Figure 8-19 VID2

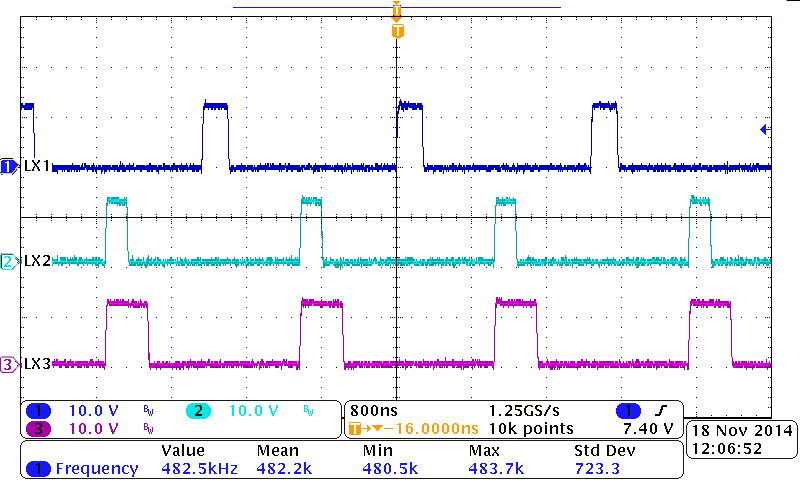

from 00 to 7F, SR = 10 mV/Cycle Figure 8-21 180°

Out-of-Phase

Figure 8-21 180°

Out-of-Phase Figure 8-23 Operation at VIN Drop to 2.5 V

Figure 8-23 Operation at VIN Drop to 2.5 V

| Iout = 2 A |

A.

Figure 8-6 BUCK1, Output Voltage Ripple| Iout = 3 A |

| Iout = 2 A |

| 1.5 to 2.25 A | SR = 0.25 A/µs |

| 1.0 to 1.5 A | SR = 0.25 A/µs |

| 1.0 to 1.5 A | SR = 0.25 A/µs |

Figure 8-16 BUCK2, Hiccup and Recovery

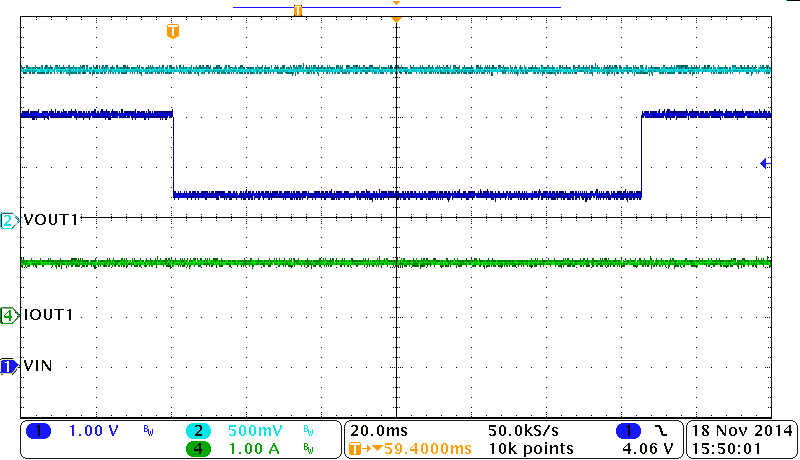

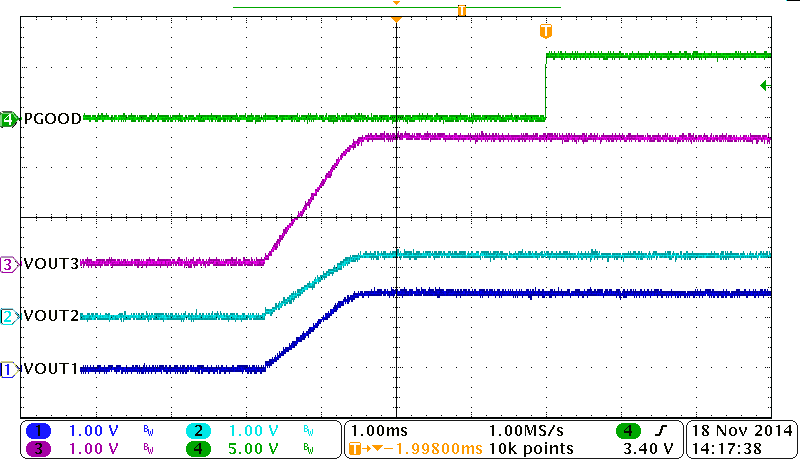

Figure 8-16 BUCK2, Hiccup and Recovery Figure 8-18 PGOOD

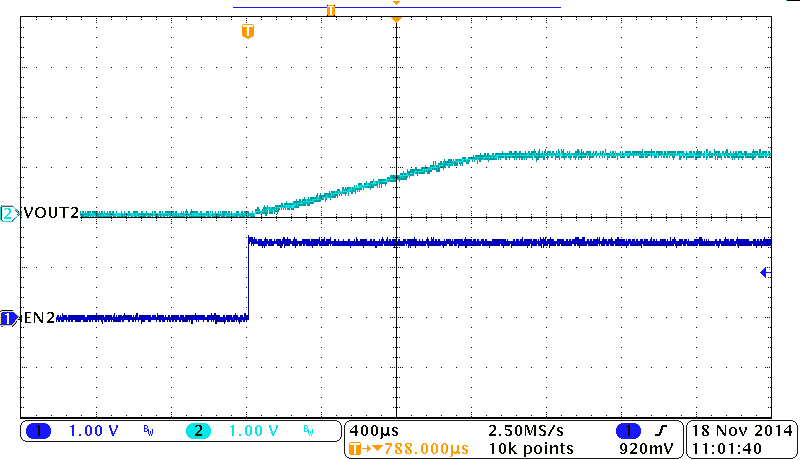

Figure 8-18 PGOOD Figure 8-20 VID2

from 7F to 00, SR = 10 mV/Cycle

Figure 8-20 VID2

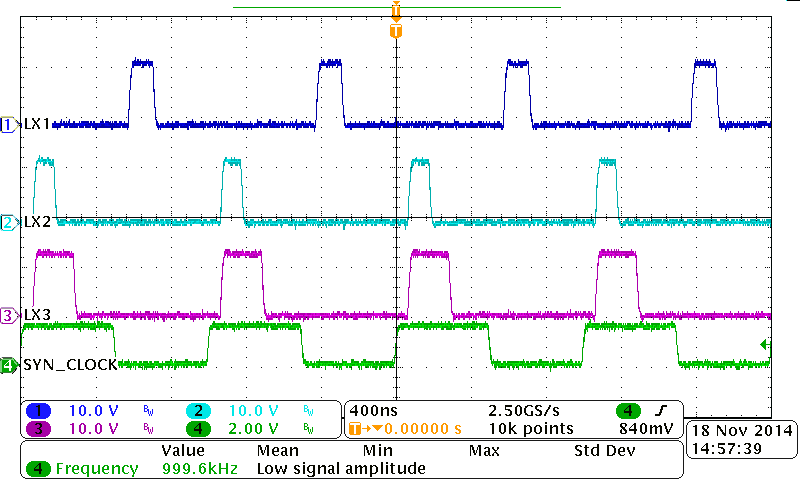

from 7F to 00, SR = 10 mV/Cycle Figure 8-22 Synchronization with External Clock

Figure 8-22 Synchronization with External Clock

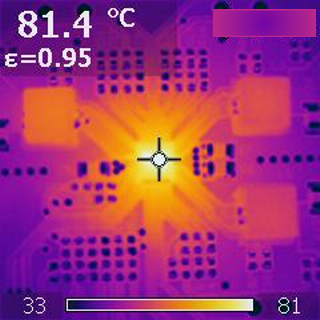

| VIN = 12 V, VOUT1 = 1.5 V/3 A, VOUT2 = 1.2 V/2 A, |

| VOUT3 = 2.5 V/2 A, |

| TA = 26.8°C EVM condition 4 layers, 75 mm × 75 mm |