ZHCS747D January 2012 – September 2021 LMK01801

PRODUCTION DATA

- 1 特性

- 2 应用

- 3 说明

- 4 Revision History

- 5 Device Comparison

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Parameter Measurement Information

-

9 Detailed Description

- 9.1 Overview

- 9.2 Functional Block Diagram

- 9.3

Feature Description

- 9.3.1 High-Speed Clock Inputs (CLKin0/CLKin0* and CLKin1/CLKin1*)

- 9.3.2 Clock Distribution

- 9.3.3 Small Divider (1 to 8)

- 9.3.4 Large Divider (1 to 1045)

- 9.3.5 CLKout Analog Delay

- 9.3.6 CLKout0 to CLKout11 Digital Delay

- 9.3.7 CLKout12 and CLKout13 Digital Delay

- 9.3.8 Programmable Outputs

- 9.3.9 Clock Output Synchronization

- 9.3.10 Default Clock Outputs

- 9.4 Device Functional Modes

- 9.5 Programming

- 9.6 Register Map

- 10Application and Implementation

- 11Power Supply Recommendations

- 12Layout

- 13Device and Documentation Support

- 14Mechanical, Packaging, and Orderable Information

10.1.1.1.2 Driving CLKin Pins With a Single-Ended Source

The CLKin pins of the LMK01801 family can be driven using a single-ended reference clock source, for example, either a sine wave source or an LVCMOS/LVTTL source. Either AC coupling or DC coupling may be used. In the case of the sine wave source that is expecting a 50 Ω load, it is recommended that AC coupling be used as shown in Figure 10-4 the circuit below with a 50 Ω termination.

The signal level must conform to the requirements for the CLKin pins listed in the Section 7.4. CLKinX_BUF_TYPE is recommended to be set to bipolar mode (CLKinX_BUF_TYPE = 0).

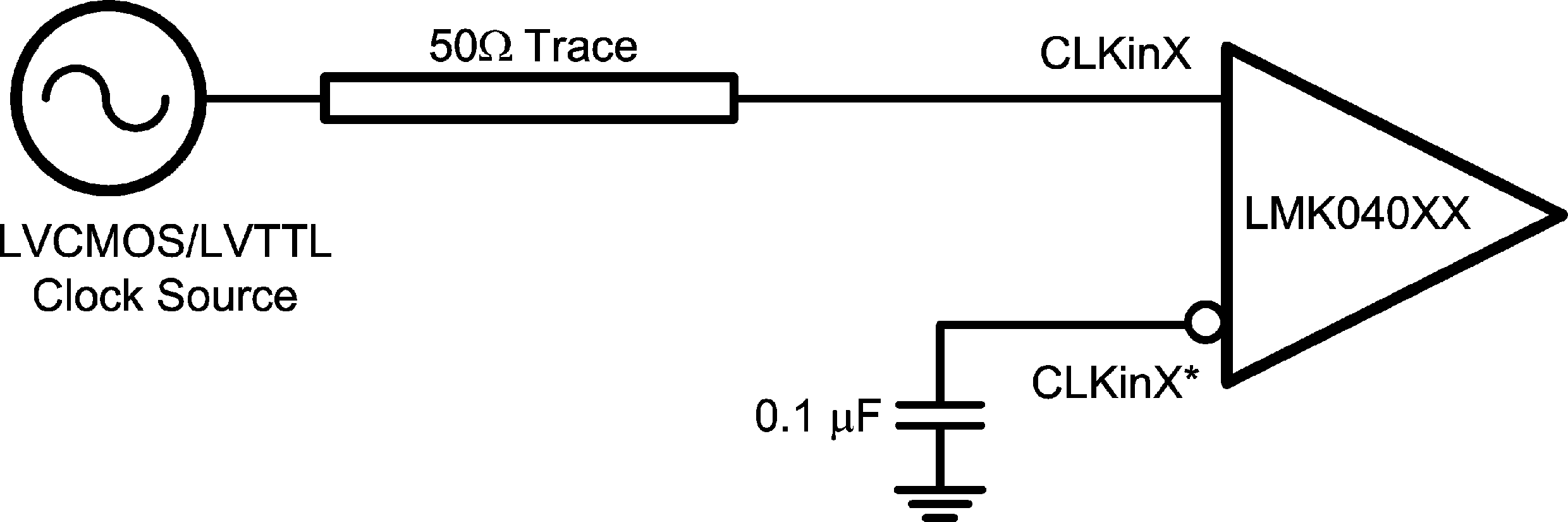

Figure 10-4 DC-Coupled LVCMOS/LVTTL Reference Clock

Figure 10-4 DC-Coupled LVCMOS/LVTTL Reference ClockIf the CLKin pins are being driven with a single-ended LVCMOS/ LVTTL source, either DC coupling or AC coupling may be used. If DC coupling is used, see Figure 10-5, the CLKinX_BUF_TYPE should be set to MOS buffer mode (CLKinX_BUF_TYPE = 1) and the voltage swing of the source must meet the specifications for DC coupled, MOS-mode clock inputs given in the table of Electrical Characteristics. If AC coupling is used, the CLKinX_BUF_TYPE should be set to the bipolar buffer mode (CLKinX_BUF_TYPE = 0). The voltage swing at the input pins must meet the specifications for AC coupled, bipolar mode clock inputs given in the table of Electrical Characteristics. In this case, some attenuation of the clock input level may be required. A simple resistive divider circuit before the AC coupling capacitor is sufficient.

Figure 10-5 DC-Coupled LVCMOS/LVTTL Reference Clock

Figure 10-5 DC-Coupled LVCMOS/LVTTL Reference Clock