ZHCSCB1 March 2014 LDC1041

PRODUCTION DATA.

- 1 特性

- 2 应用范围

- 3 说明

- 4 修订历史记录

- 5 Terminal Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Applications and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11器件和文档支持

- 12机械封装和可订购信息

10 Layout

10.1 Layout Guidelines

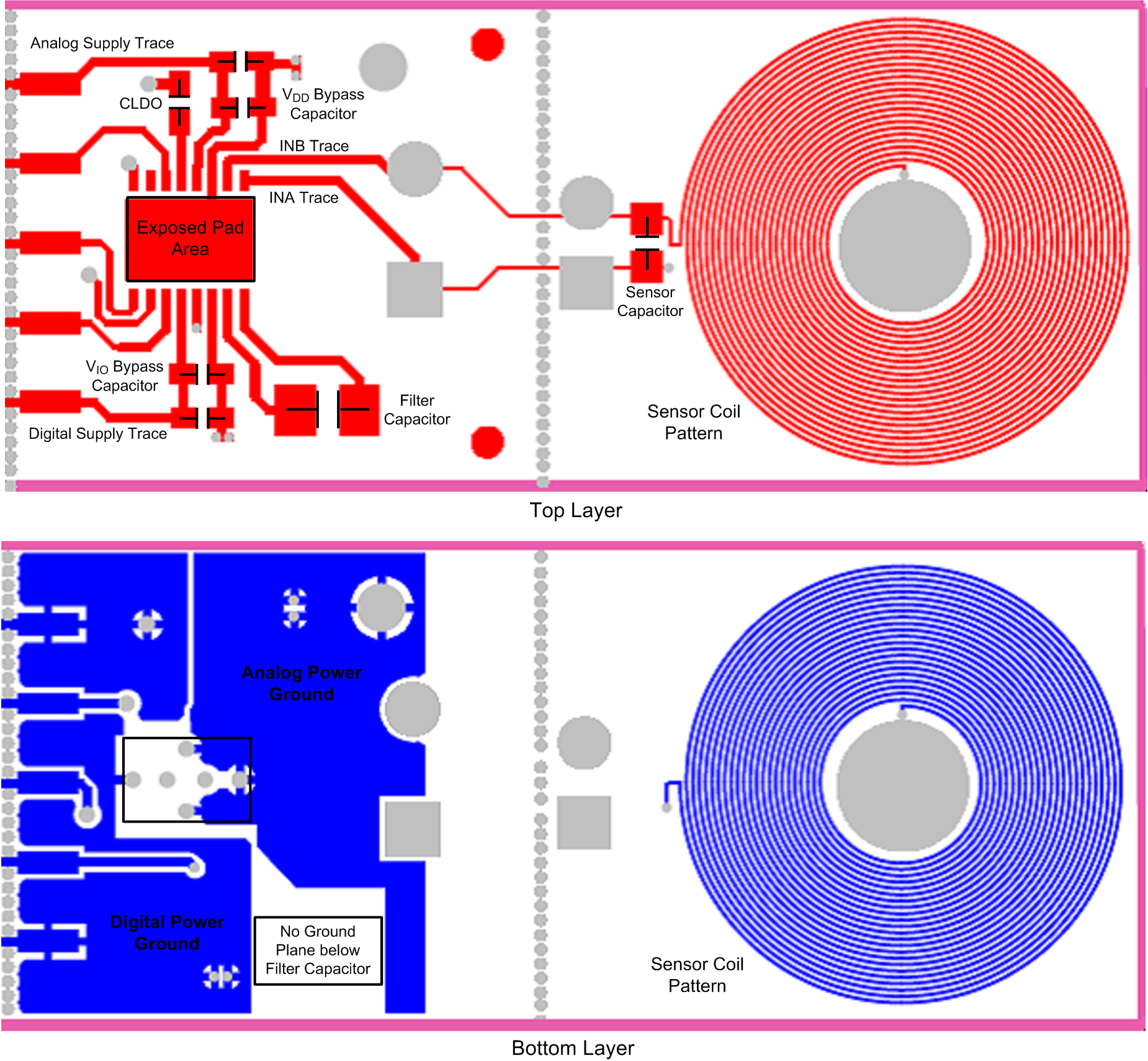

● The VDD and VIO terminal should be bypassed to ground with a low ESR ceramic bypass capacitor. The typical recommended bypass capacitance is 0.1uF ceramic with a X5R or X7R dielectric.

● The optimum placement is closest to the VDD/VIO and GND/DGND terminals of the device. Care should be taken to minimize the loop area formed by the bypass capacitor connection, the VDD/VIO terminal, and the GND/DGND terminal of the IC. See Figure 23 for a PCB layout example.

● The CLDO terminal should be bypassed to digital ground (DGND) with a 56nF ceramic bypass capacitor.

● The filter capacitor selected for the application using the procedure described in section Choosing Filter Capacitor (CFA and CFB Terminals) is connected between CFA and CFB terminals. Place the filter capacitor close to the CFA and CFB terminals. Do not use any ground/power plane below the capacitor and the trace connecting the capacitor and the CFA /CFB terminals.

● Use of two separate ground plane for GND and DGND is recommended with a start connection. See Figure 23 for a PCB layout example.

10.2 Layout Example

Figure 23. LDC10xx Board Layout

Figure 23. LDC10xx Board Layout