ZHCY068B March 2018 – January 2024 AMC1305M25 , AMC1311 , AMC1311-Q1 , ISO1042 , ISO1042-Q1 , ISO5851 , ISO7741 , ISO7841 , ISOM8710 , UCC20225-Q1 , UCC20225A-Q1 , UCC21520 , UCC21540 , UCC23513 , UCC5390

失效模式 2:测试结果

为了验证 TI 增强型隔离技术在违反安全限制电流或功率参数的应力条件下是否表现出“失效开路”行为,执行了多项测试。实验 1 和实验 2 选择了增强型隔离式栅极驱动器 ISO5851 和增强型四通道数字隔离器 ISO7841。

在实验 1 中,隔离器的输出引脚被短路,同时升高隔离器的电源电压,直到隔离器不再起作用。

在实验 2 中,使用浪涌发生器对隔离器的一侧施加重复的高压冲击(1kV 和 2kV)。其目的是模拟短路对电机驱动器、光伏逆变器和其他类似应用中高压直流总线的影响。

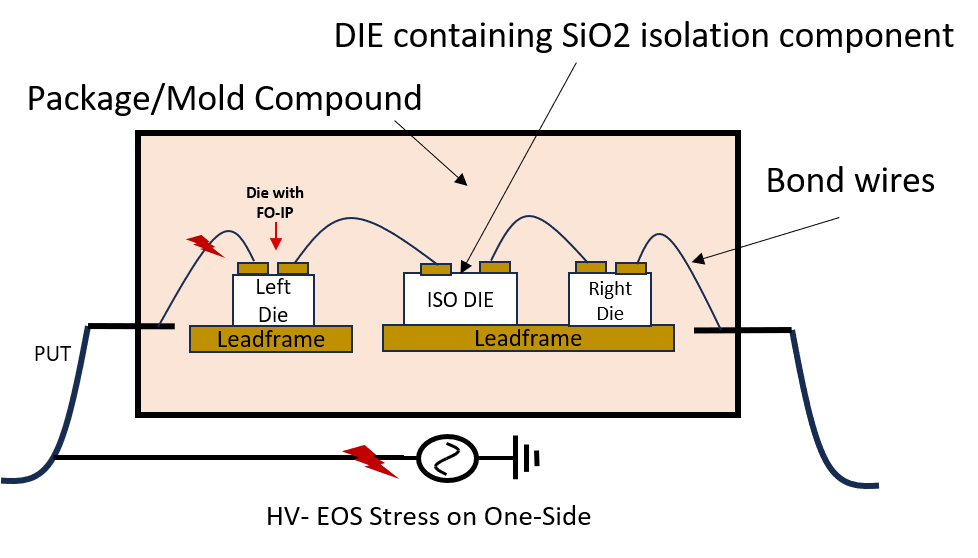

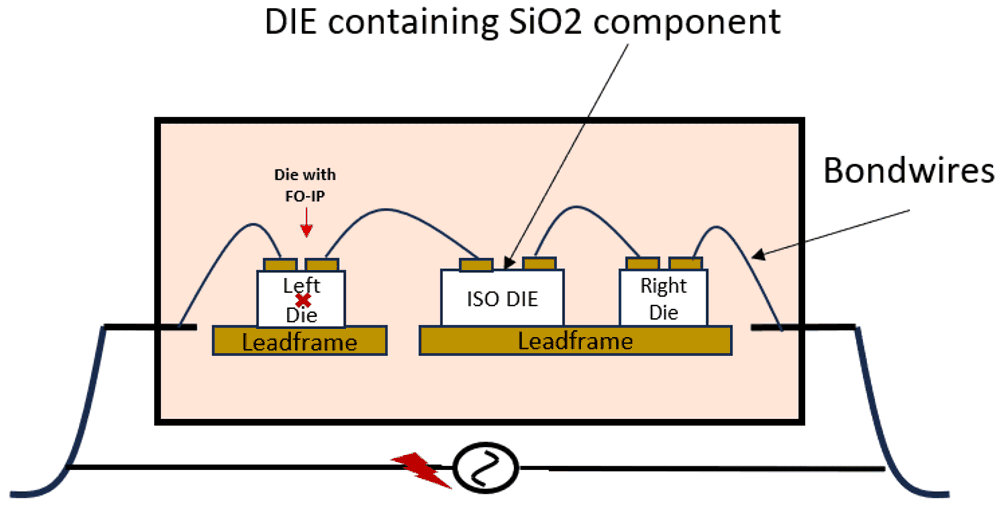

TI 还针对 ISOM8710 光耦仿真器等产品在输入芯片上实现了新的“失效断开”功能,其中隔离基于图 8 中所示的 3 芯片解决方案。这一新特性确保绝缘栅和输出芯片受到输入侧 EOS 事件的保护。图 9 提供了具有输入失效断开 IP 的 3 芯片光耦仿真器的截面视图。

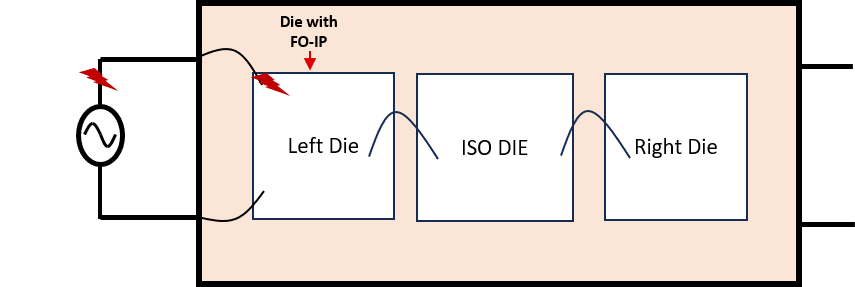

图 8 在 3 芯片隔离器的一侧施加高压应力。采用失效断开 (FO) IP 设计的左芯片可确保 ISO 芯片和右芯片在 EOS 事件下的完整性。

图 8 在 3 芯片隔离器的一侧施加高压应力。采用失效断开 (FO) IP 设计的左芯片可确保 ISO 芯片和右芯片在 EOS 事件下的完整性。 图 9 具有失效断开 IP 的 3 芯片光耦仿真器的截面视图。

图 9 具有失效断开 IP 的 3 芯片光耦仿真器的截面视图。为了演示失效断开特性,在实验 3-5 中对具有三种 EOS 类型的输入芯片施加了应力,并查看了施加应力后的隔离完整性。

在实验 3 中,使用直流电源通过不同的源阻抗在室温和高温下向输入侧(阳极和阴极之间)施加 EOS 电压长达 10 分钟,这会导致输入芯片失效断开。这模拟了可以持续到系统关断的 DC-EOS 事件。接下来,施加 EOS 12 小时,以确保输入芯片保持失效断开,即使对于开路器件上的持续 EOS 应力也是如此。最后,在绝缘栅上执行缓升至击穿测试 (RTB),以检查左侧芯片上的 EOS 事件导致功能故障后的隔离完整性。图 10 显示了我们对隔离栅施加高压应力的 RTB 设置。

图 10 整个隔离栅的高压斜升至击穿电压 (RTB)。

图 10 整个隔离栅的高压斜升至击穿电压 (RTB)。在实验 4 中,使用类似的测试程序更改实验 3 的 EOS 输入。我们连接了预充电的电容器,以研究电容器放电对隔离输入侧的影响。

在实验 5 中,向输入侧施加了电流源,并斜升直至输入侧失效断开。实验 3 至 5 模拟上述应用中直流电源总线对输入侧的短路。

在 ISO 比较器(例如 AMC23C10)的输出芯片引脚(VDD、OUT1 和 OUT2)上也实现了失效断开功能,其中隔离基于单芯片增强型隔离电容器方法,如图 6 所示。还对这些器件进行了实验 3-5,以确保输入芯片和隔离在 EOS 事件导致输出芯片发生功能故障后完好无损。表 1 中总结了这些结果。

表 1 列出了这些实验的结果。在所有情况下,在高功率应力之后,所有隔离器都在 1 侧和 2 侧之间保持高阻抗。也就是说,它们“失效断开”。此外,针对 3kVrms 的基本隔离额定值对 ISO5851 和 ISO7841 进行了进一步测试,测试时间为 60 秒。所有器件都能够承受这种电压而不发生击穿。ISOM8710 在施加应力后在油中缓升至击穿情况下进行了进一步测试。换句话说,在高功率测试后保留基本隔离。作为一项极端测试,将正负极性的 50 2kV 浪涌脉冲施加到栅极驱动器和数字隔离器的两个单元中。即使在承受如此严重的应力后,隔离器也会在 1 侧和 2 侧之间保持高阻抗,保持基本隔离,并“失效断开”。

| 实验编号 | 器件 | 测试说明 | 器件数 | 观察结果 | 施加应力之后的 RIO | 施加应力之后的 VISO 60s 测试,3kVRMS |

|---|---|---|---|---|---|---|

| 1、2 | ISO5851 | 栅极驱动器输出短接至 2 侧接地。电源电压升至 50V,直至器件损坏 | 5 | 芯片 3 损坏 | >1TΩ | 通过 |

| 栅极驱动器输出上的 2kV 浪涌,每个极性(+ve 和 -ve)5 次 | 5 | 芯片 3 损坏 | >1TΩ | 通过 | ||

| 栅极驱动器输出上的 2kV 浪涌,每个极性(+ve 和 -ve)50 次 | 2 | 芯片 3 损坏 | >1TΩ | 通过 | ||

| 1、2 | ISO7841 | 所有 2 侧引脚短接至侧 2 接地或电源,或保持悬空。电源电压升至 25V,直至器件损坏。 | 5 | 芯片 2 损坏 | >1TΩ | 通过 |

| 所有 2 侧引脚上均为 1kV 或 2kV 浪涌,每个极性(+ve 和 -ve)5 次 | 4 | 芯片 2 损坏 | >1TΩ | 通过 | ||

| 所有 1 侧引脚上均为 2kV 浪涌,每个极性(+ve 和 -ve)5 次 | 2 | 芯片 1 损坏 | >1TΩ | 通过 | ||

| 所有 1 侧引脚上均为 2kV 浪涌,每个极性(+ve 和 -ve)50 次 | 2 | 芯片 1 损坏 | >1TΩ | 通过 | ||

| 所有 1 侧引脚上均为 2kV 浪涌,每个极性(+ve 和 -ve)500 次 | 1 | 芯片 2 损坏 | >1TΩ | 通过 | ||

| 3、4、5 | ISOM8710 | EOS 施加到引脚 1 与接地之间的输入侧,输出侧开路。高达 43V 的不同电源电压值和电流经过测试,直到输入芯片上出现失效断开。在发生故障后,施加了 12 小时的 EOS,并测量了输入芯片电阻。使用 RTB 对施加应力后的隔离完整性进行了测试。 | 270 | 隔离性能不会下降,无法正常工作 | >1TΩ | 通过 |

| 在引脚 1 与接地之间连接一个预充电的 2.2mF 电容(30V,3A)。如果发生短路故障,则继续驱动高达 3A 的电流,直到输入芯片失效断开。使用 RTB 对施加应力后的隔离完整性进行了测试。 | 5 | 隔离性能不会下降,无法正常工作 | >1TΩ | 通过 | ||

| 向初级施加逐渐升至高达 3A 的电流,直到输入芯片失效断开。在短路故障中,继续馈送直至开路。使用 RTB 对施加应力后的隔离完整性进行了测试。 | 5 | 隔离性能不会下降,无法正常工作 | >1TΩ | 通过 | ||

| 3、4、5 | AMC23C10 | EOS 施加到引脚 1 与接地之间的输入侧,输出侧开路。高达 36V 的不同电源电压值和电流经过测试,直到输入芯片上出现失效断开。在发生故障后,施加了 24 小时的 EOS,并测量了输入芯片电阻。使用 RTB 对施加应力后的隔离完整性进行了测试。 | 每个引脚 20 总共 60 | 隔离性能不会下降,无法正常工作 | >1TΩ | 通过 |

| 在引脚 1 与接地之间连接一个预充电的 2.2mF 电容(30V,3A)。如果发生短路故障,则继续驱动高达 3A 的电流,直到输入芯片失效断开。使用 RTB 对施加应力后的隔离完整性进行了测试。 | 5 | 隔离性能不会下降,无法正常工作 | >1TΩ | 通过 | ||

| 向初级施加逐渐升至高达 3A 的电流,直到输入芯片失效断开。在短路故障中,继续馈送直至开路。使用 RTB 对施加应力后的隔离完整性进行了测试。 | 5 | 隔离性能不会下降,无法正常工作 | >1TΩ | 通过 |

在施加大功率应力后,其中一些器件被拆封并拍照,以检查每个器件的内部状态(请参见图 11 和图 12)。结果符合我们对失效分析的预期。虽然面向高功率应力的芯片受到严重损坏,但至少完全保留了带有一个隔离电容器的一个芯片。该芯片负责观测到的“失效断开”性质。如果使用 ISO5851 作为三芯片模块,则仅对栅极驱动器芯片造成损坏,对隔离栅的损坏非常小。