ZHCT389 February 2023 DLP6500FLQ , DLP650LNIR , DLP7000 , DLP7000UV , DLP9000X , DLP9000XUV , DLP9500 , DLP9500UV , DLPC410 , DLPC910

3.3 支持 SPI 闪存配置方法的设计详细信息

通过 DLPC910 和 DLPC410 支持主串行外设接口 (SPI) 闪存配置的设计详细信息如下:

FPGA 控制器上的主串行外设接口闪存配置模式 M[2..0] 引脚必须更改为 M[2:0] = 001。

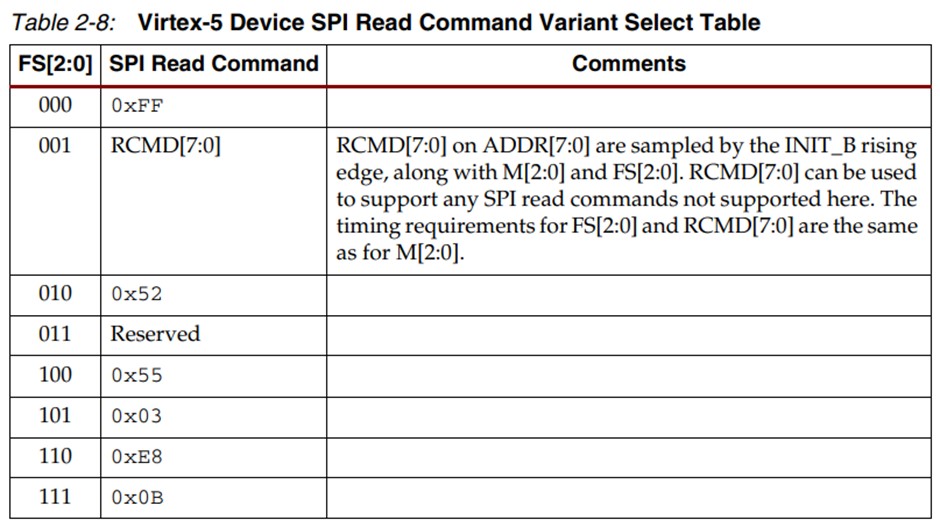

有关更多信息,请参阅 Xilinx Virtex-5 配置指南 UG191 的第 62 页:必须正确连接 FS[2:0] 引脚,以确定所选 SPI 闪存用于连接 FPGA 控制器的读取命令类型。下表(UG191 – Xilinx Virtex-5 配置指南中的表 2-8)描述了可用的选择:

FS2 = DLPC910 控制器和 DLPC410 控制器的引脚 AB11

FS1 = DLPC910 控制器和 DLPC410 控制器的引脚 AA13

FS0 = DLPC910 控制器和 DLPC410 控制器的引脚 AA14