ZHCAC41 February 2023 TMS320F280025C

4.6 步骤 5 :仿真逻辑设计

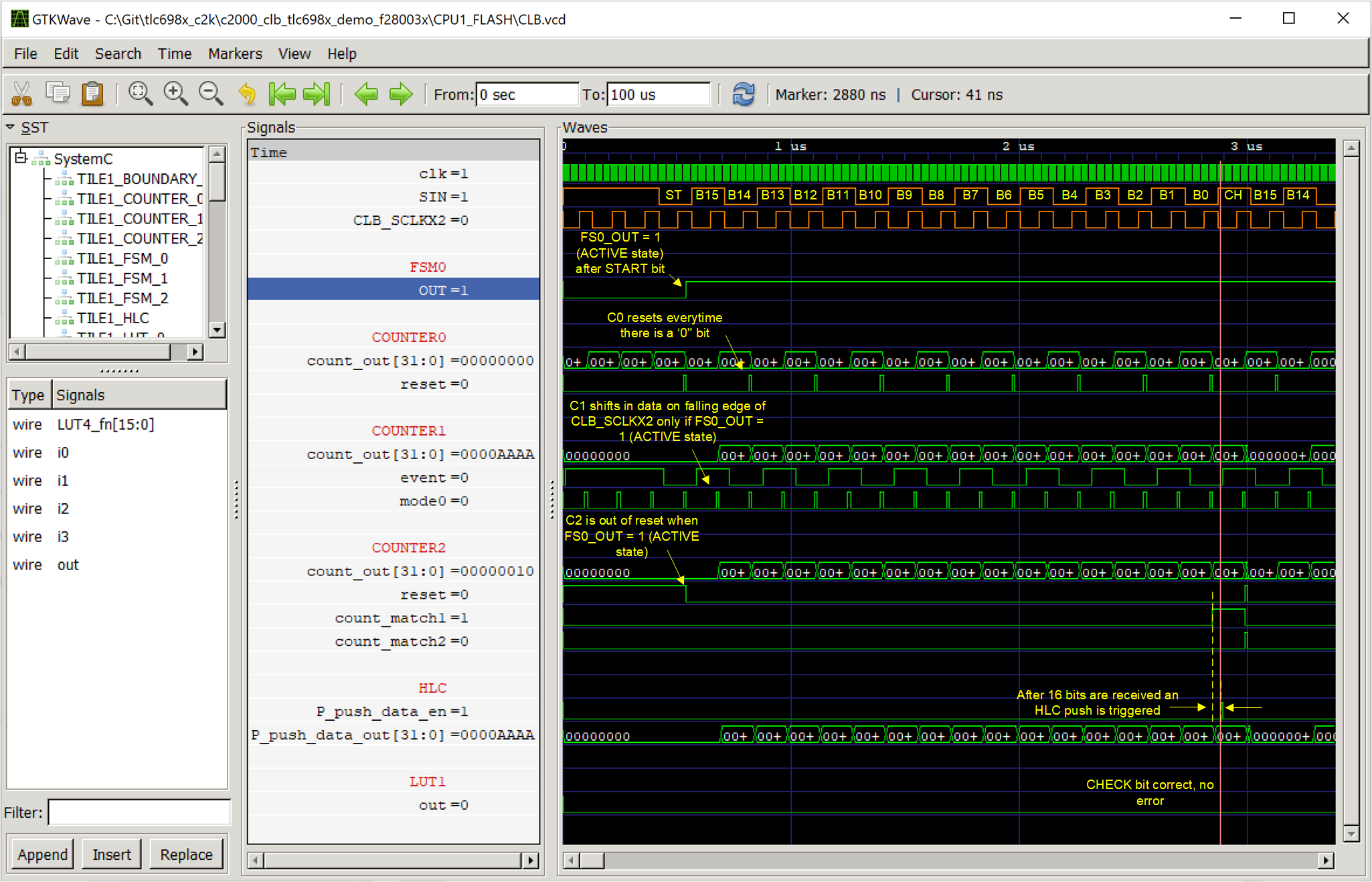

#FIG_X5K_1YC_3VB 中仿真了数据接收操作。对于此仿真,使用 0xAAAA 的简单模式作为数据输入。该仿真显示了由 START 位指示的帧开始、完整接收字的捕获以及 CHECK 位的验证。

图 4-15 LED 驱动器的数据接收仿真

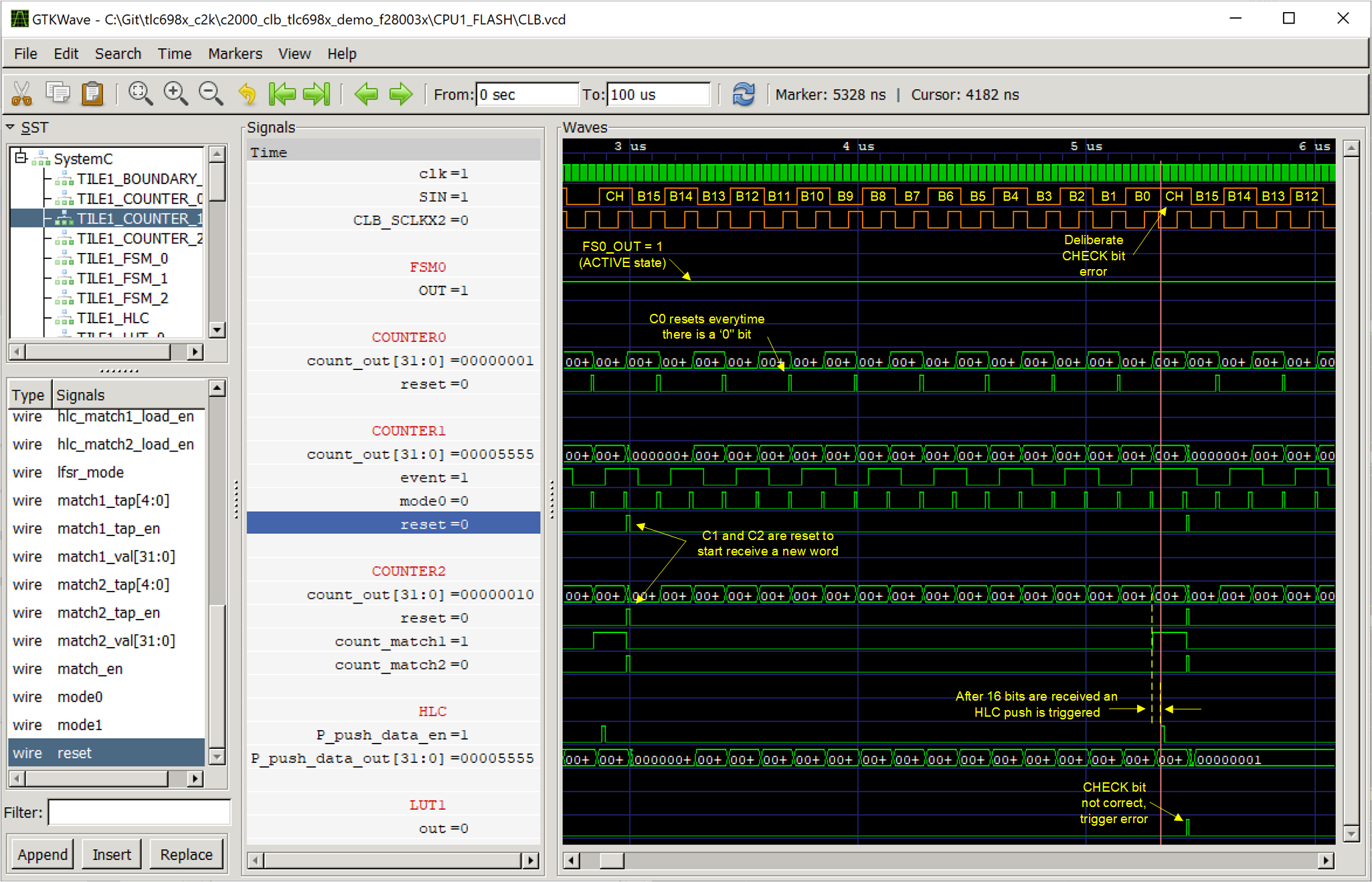

图 4-15 LED 驱动器的数据接收仿真第二个数据接收仿真如#GUID-020BC078-9055-4081-A916-44B0D9205A26 所示。在此仿真中,向传入数据流添加了不正确的 CHECK 位,以便验证 CHECK 位逻辑的操作。该仿真显示 LUT1 块的输出变为高电平,以指示检测到 CHECK 位错误。

图 4-16 CHECK 位错误逻辑仿真

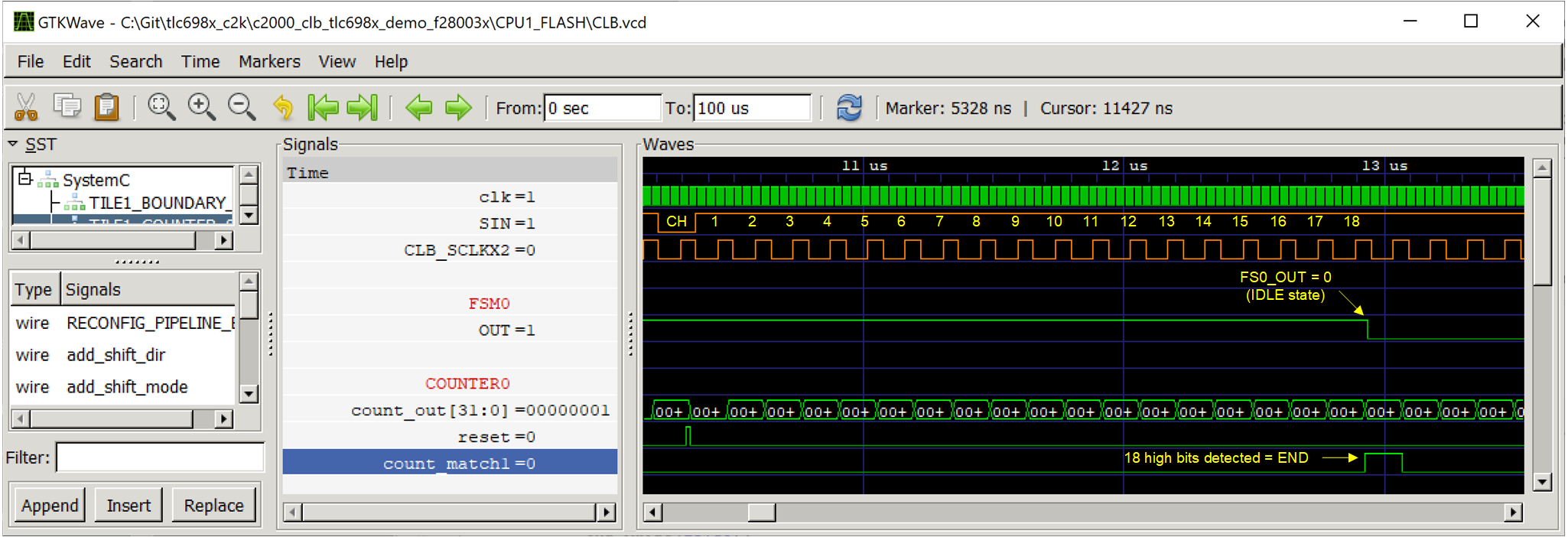

图 4-16 CHECK 位错误逻辑仿真最后,#GUID-9E7D8A06-4DBD-459E-AE35-2668AF19A138 中的仿真显示了 END 位的检测。FSM0 块在检测到 END 位时将 CLB 逻辑转换为 IDLE 状态。

图 4-17 END 帧检测

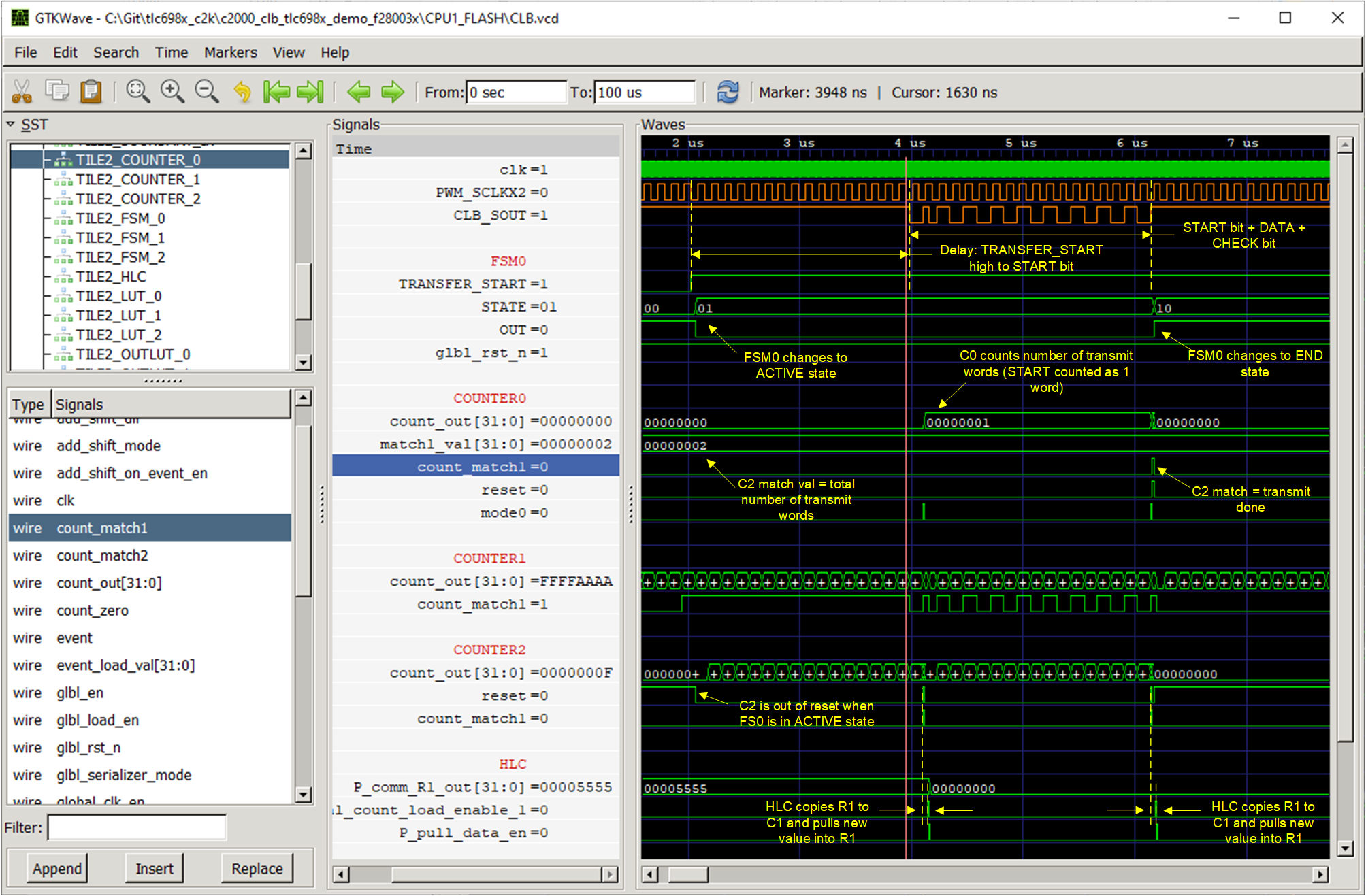

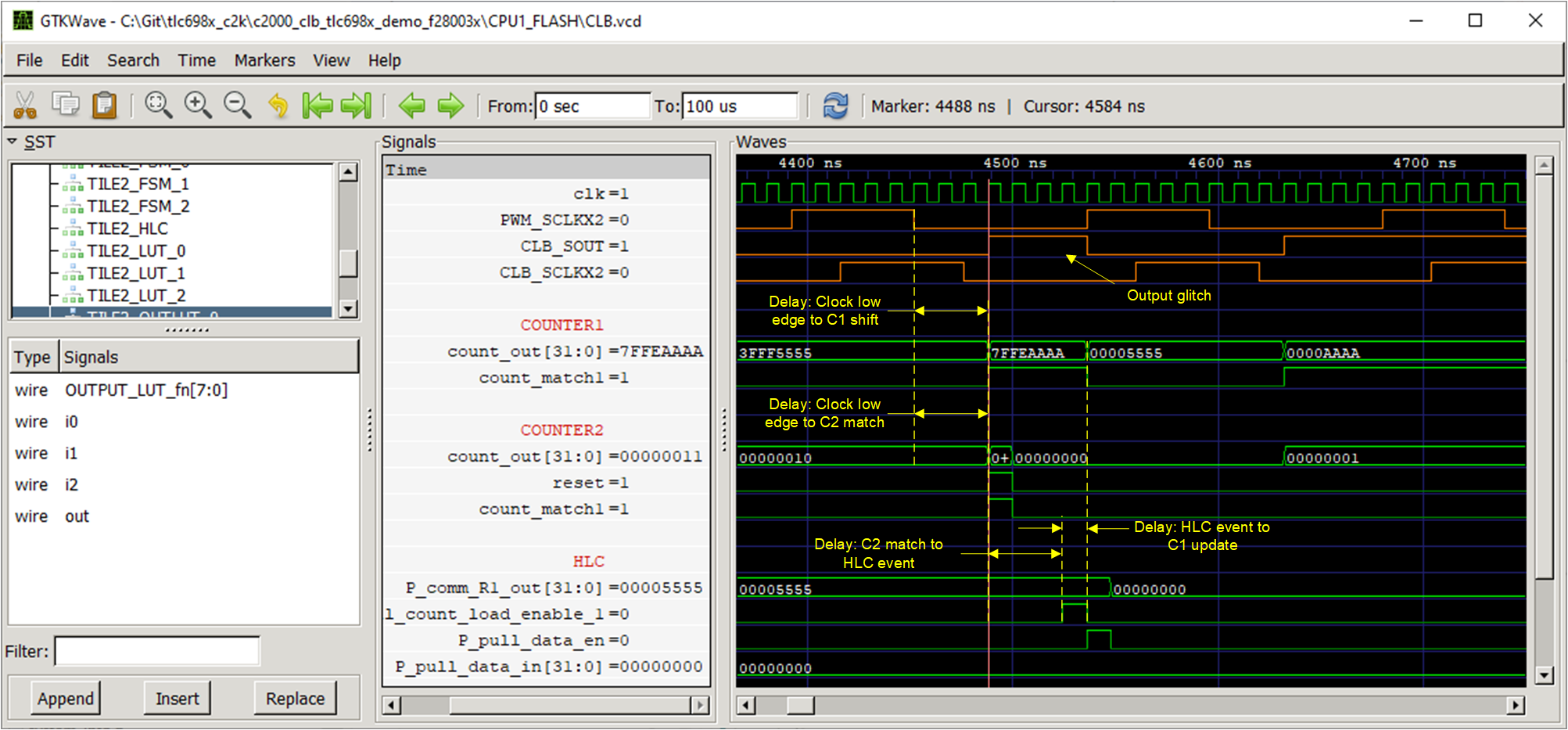

图 4-17 END 帧检测#GUID-DE20B45E-17F5-40B4-A380-DF8C0797729D 中仿真了数据发送操作。该仿真显示了单个 0x5555 字的发送,从 START 位开始,到 END 帧结束。为了简化 CLB 逻辑,通过允许逻辑块发送一个 0xFFFF 字来实施 START 位。使用逻辑块的 CHECK 位逻辑在第 17 个时钟周期生成 START 位。同样,要生成 END 帧,CLB 逻辑仅在最后一个字发送结束时将 CLB_SOUT 信号设置为 1。CLB 逻辑取决于 CPU 在开始新的数据发送之前至少等待 18 个 PWM_SCLKX2 周期。

图 4-18 LED 驱动器的数据发送仿真

图 4-18 LED 驱动器的数据发送仿真由于更新输出串行器(计数器 1)出现延迟,在数据发送操作期间会观察到输出干扰。#GUID-E12DC052-9332-4807-ABA6-44B7877A2BFD 显示了从 PWM_SCLKX2 低沿到输出串行器最终更新的内部延迟。干扰的结果是接收器件的建立时间缩短。建立时间不应从 PWM_SCLKX2 信号的上升沿计算,因为此时钟也会随着它通过 CLB 逻辑块而延迟。而是应根据 CLB_SCLKX2 信号计算建立时间。此信号是接收器件将观察到的 PWM_SCLKX2 的延迟版本。

图 4-19 输出干扰

图 4-19 输出干扰可以通过在传递到 CLB_SOUT 之前锁存串行器输出来消除干扰。但是,由于每个发送仿真预计至少有两个 CLB 周期的建立时间,这足以满足 LP5891-Q1 器件所需的 10ns 建立时间要求,因此未使用此方法。