ZHCAC41 February 2023 TMS320F280025C

3.6 步骤 5 :仿真逻辑设计

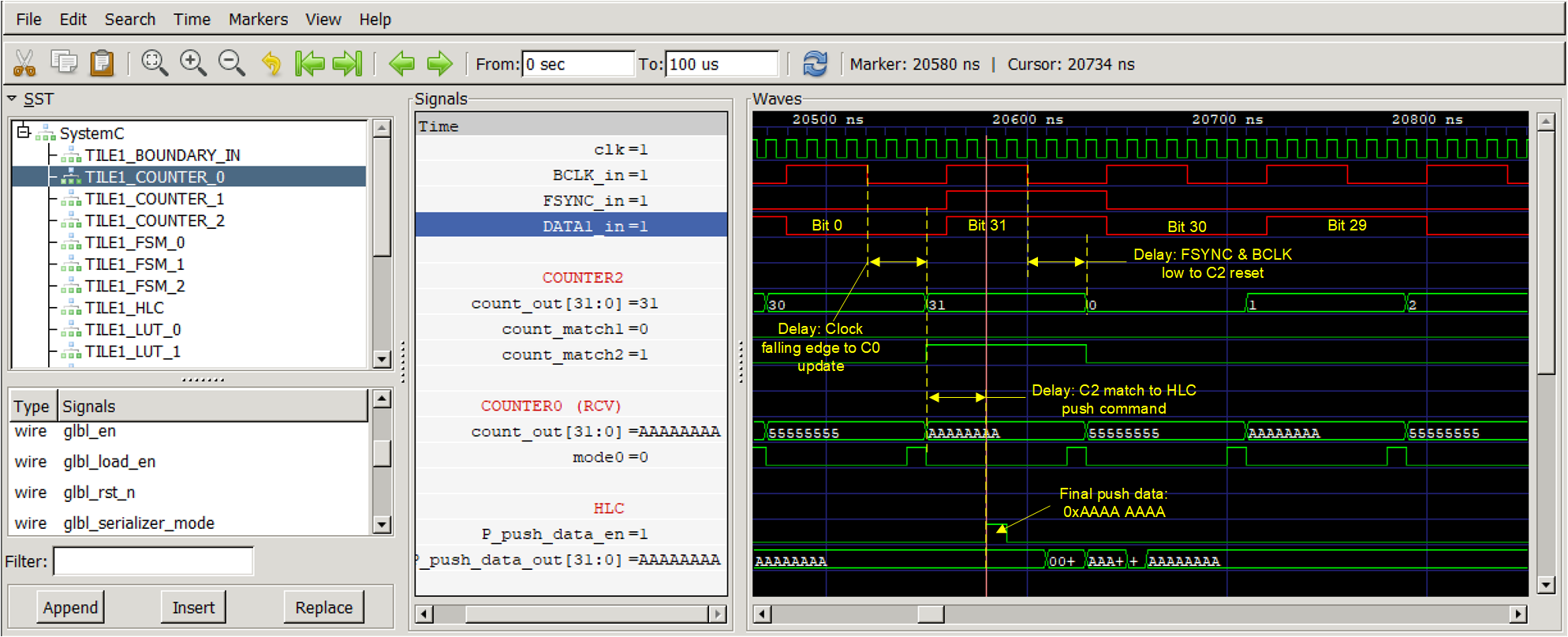

#GUID-031F478E-6F5E-4C12-A89C-E5F4B5A6ED60 中仿真了数据接收操作。对于此仿真,使用 0xAAAA AAAA 的简单模式作为数据输入。仿真显示了 TDM 帧中最后一个字的最后一位与新帧开始之间的转换。

图 3-9 TDM-8 数据接收仿真

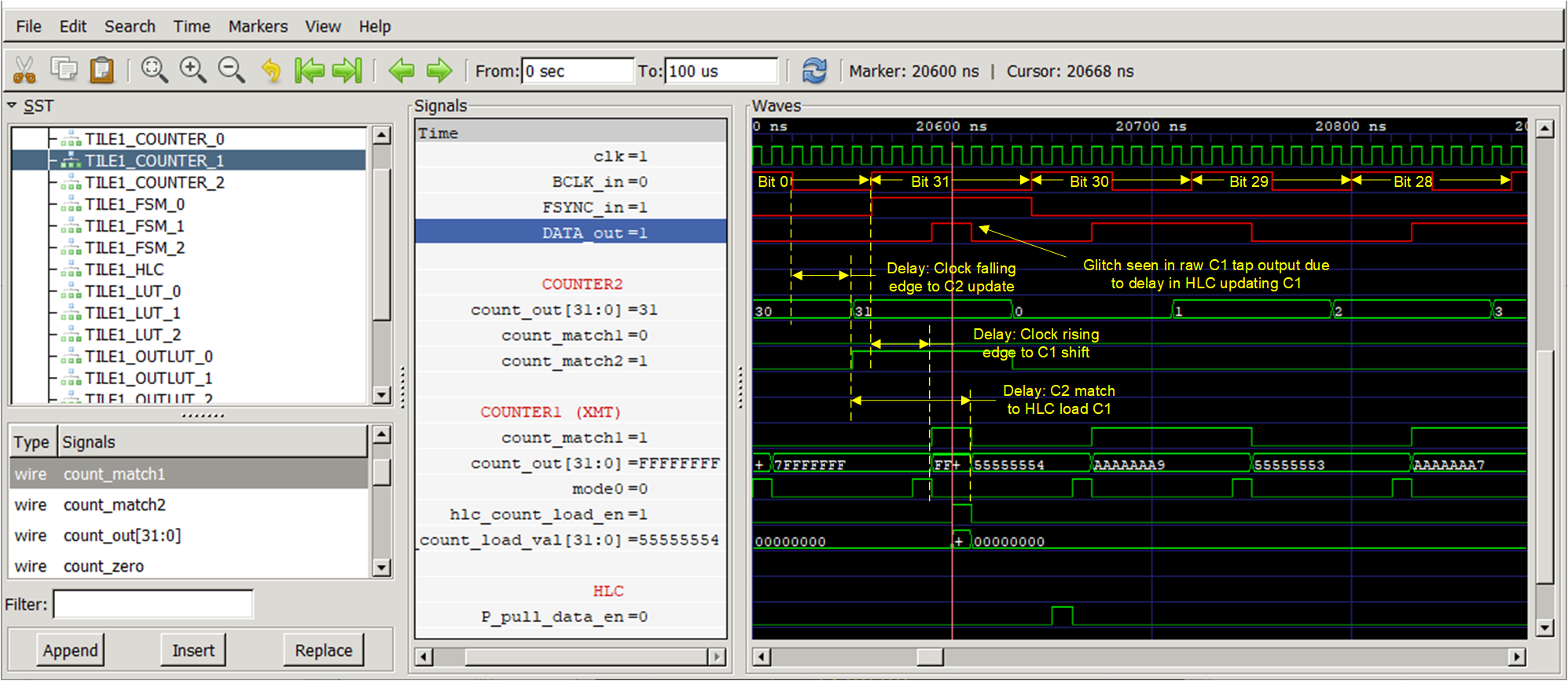

图 3-9 TDM-8 数据接收仿真#GUID-3A487FF6-386F-4A8D-959B-65AF1E9DCB8C 中仿真了数据发送操作。仿真显示了 TDM 帧中最后一个字的最后一位与新帧开始之间的转换。对于此仿真,持续发送 0x5555 5554 的模式以强调串行字之间串行器输出端可能出现短暂干扰。由于串行器必须在对其计数器值移位后 加载,以便避免丢失发送字中的最高有效位,因此串行器输出会有一小段时间无效。

图 3-10 TDM-8 数据发送仿真

图 3-10 TDM-8 数据发送仿真请注意,在此 TDM 示例中,HLC 已配置为将 C0 中的值推入 FIFO,然后将新值加载到 C1(请参阅GUID-8B5B018F-15D7-413D-9AC6-A92317D99D97.html#GUID-2167560E-7B3A-48E5-ABAF-3E67ACF28A6E)。这是有意为之,是为了确保在 BCLK_IN 的上升沿之后 加载 C1。由于 HLC 操作在 BCLK 的下降沿触发,且串行器操作依赖于 BCLK 的上升沿,因此 BCLK_IN 周期存在固有依赖关系。如果延长了 BCLK_IN 周期(降低 BCLK_IN 频率或增大 CLB 时钟频率),则存在 C1 更新发生在时钟上升沿之前的风险,这会导致串行字中最高有效位丢失。

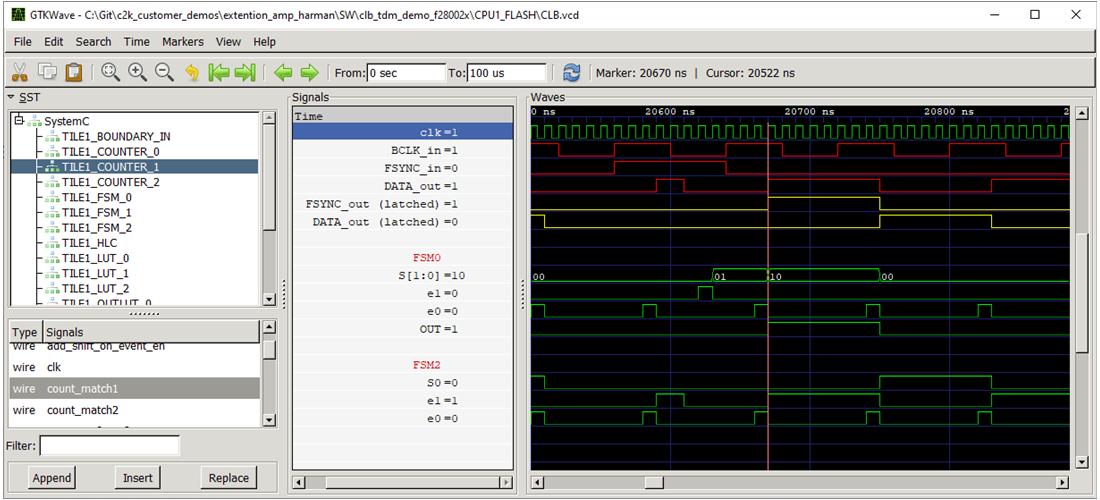

如#GUID-3A487FF6-386F-4A8D-959B-65AF1E9DCB8C 所示,输出数据与输入 FSYNC 和 BCLK 之间存在延迟。为了输出彼此同步的 FSYNC 和 DATA1 信号,使用两个 FSM 来锁存和延迟这两个信号。此功能的仿真结果如#FIG_OSQ_HGF_2VB 所示。

图 3-11 FSYNC 和 DATA1 同步

图 3-11 FSYNC 和 DATA1 同步