ZHCSMX0B September 2019 – December 2020 TPA6304-Q1

PRODUCTION DATA

- 1 特性

- 2 应用

- 3 说明

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Parameter measurement information

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3

Feature Description

- 7.3.1 Single-Ended Analog Inputs

- 7.3.2 Gain Control

- 7.3.3 Class-D Operation and Spread Spectrum Control

- 7.3.4 Gate Drive

- 7.3.5 Power FETs

- 7.3.6

Load Diagnostics

- 7.3.6.1

DC Load Diagnostics

- 7.3.6.1.1 Automatic DC Load Diagnostics at Device Initialization

- 7.3.6.1.2 Automatic DC Load Diagnostics During Hi-Z to MUTE or PLAY Transition

- 7.3.6.1.3 Manual Start of DC Load Diagnostics

- 7.3.6.1.4 Short-to-Ground

- 7.3.6.1.5 Short-to-Power

- 7.3.6.1.6 Shorted Load and Open Load

- 7.3.6.1.7 Line Output Diagnostics

- 7.3.6.2 AC Load Diagnostics

- 7.3.6.1

DC Load Diagnostics

- 7.3.7 Power Supply

- 7.3.8 Device Initialization and Power-On-Reset (POR)

- 7.3.9 Protection and Monitoring

- 7.3.10 Hardware Control Pins

- 7.4

Device Functional Modes

- 7.4.1 Internal Reporting Signals

- 7.4.2 Device States and Flags

- 7.4.3 Fault Events

- 7.4.4 Warning Events

- 7.5 Programming

- 7.6 Register Maps

- 8 Application Information Disclaimer

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

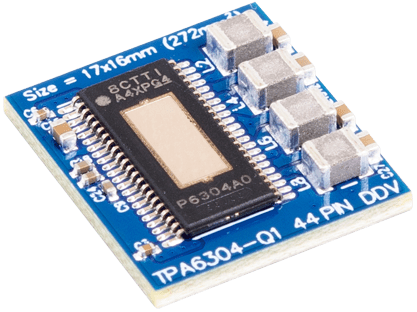

3 说明

TPA6304-Q1 器件是一款采用 2.1MHz PWM 开关频率的四通道模拟输入 D 类 Burr-Brown™ 音频放大器,可实现经成本优化的解决方案,PCB 尺寸非常小,仅为 2.7cm2,具有高阻抗单端输入,启动/停止过程中可在低至 4.5V 的电压下全面运行。

TPA6304-Q1 D 类音频放大器的设计十分出色,可适用于入门级汽车音响主机,以作为系统设计的一部分提供模拟音频输入信号。与传统的线性放大器解决方案相比,D 类拓扑技术显著提高了器件效率。

输出开关频率既可以设置为高于 AM 频带,以便消除 AM 频带干扰并降低输出滤波器尺寸及成本;也可以设置为低于 AM 频带,以便进一步优化效率。

该器件采用带外露散热焊盘的 44 引脚 HTSSOP 封装。

器件信息

| 器件型号 | 封装(1) | 封装尺寸(标称值) |

|---|---|---|

| TPA6304-Q1 | HTSSOP (44) | 14.00mm x 6.10mm |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附录。

参考板

参考板