ZHCSID6A December 2018 – December 2018 LMK05318

PRODUCTION DATA.

- 1 特性

- 2 应用

- 3 说明

- 4 修订历史记录

- 5 (说明 (续))

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Parameter Measurement Information

-

9 Detailed Description

- 9.1 Overview

- 9.2 Functional Block Diagram

- 9.3

Feature Description

- 9.3.1 Oscillator Input (XO_P/N)

- 9.3.2 Reference Inputs (PRIREF_P/N and SECREF_P/N)

- 9.3.3 Clock Input Interfacing and Termination

- 9.3.4 Reference Input Mux Selection

- 9.3.5 Hitless Switching

- 9.3.6 Gapped Clock Support on Reference Inputs

- 9.3.7 Input Clock and PLL Monitoring, Status, and Interrupts

- 9.3.8

PLL Relationships

- 9.3.8.1 PLL Frequency Relationships

- 9.3.8.2 Analog PLLs (APLL1, APLL2)

- 9.3.8.3 APLL Reference Paths

- 9.3.8.4 APLL Phase Frequency Detector (PFD) and Charge Pump

- 9.3.8.5 APLL Feedback Divider Paths

- 9.3.8.6 APLL Loop Filters (LF1, LF2)

- 9.3.8.7 APLL Voltage Controlled Oscillators (VCO1, VCO2)

- 9.3.8.8 APLL VCO Clock Distribution Paths (P1, P2)

- 9.3.8.9 DPLL Reference (R) Divider Paths

- 9.3.8.10 DPLL Time-to-Digital Converter (TDC)

- 9.3.8.11 DPLL Loop Filter (DLF)

- 9.3.8.12 DPLL Feedback (FB) Divider Path

- 9.3.9 Output Clock Distribution

- 9.3.10 Output Channel Muxes

- 9.3.11 Output Dividers (OD)

- 9.3.12 Clock Outputs (OUTx_P/N)

- 9.3.13 Glitchless Output Clock Start-Up

- 9.3.14 Clock Output Interfacing and Termination

- 9.3.15 Output Synchronization (SYNC)

- 9.3.16 Zero-Delay Mode (ZDM) Synchronization for 1-PPS Input and Output

- 9.4 Device Functional Modes

- 9.5 Programming

- 10Application and Implementation

- 11Power Supply Recommendations

- 12Layout

- 13器件和文档支持

- 14机械、封装和可订购信息

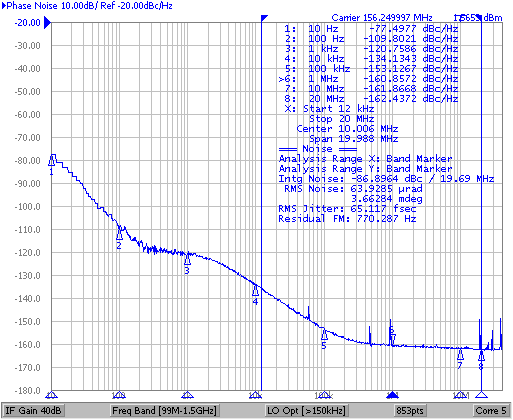

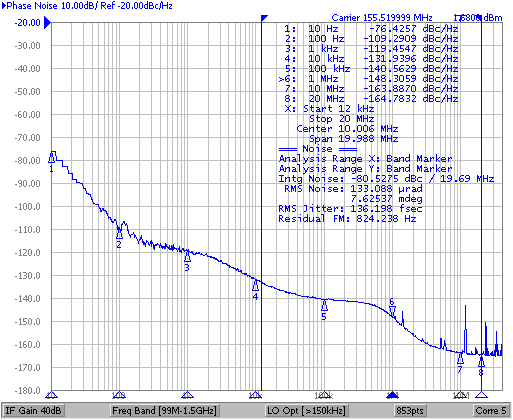

10.2.3 Application Curves

Unless otherwise noted, test conditions are the same as in Typical Characteristics. 156.25-MHz output (APLL1) on OUT3 and 155.52 MHz output (APLL2) on OUT4 running simultaneously to demonstrate minimal coupling between the PLL domains and minimal degradation in phase noise and jitter. Device operating in DPLL Mode with Cascaded APLL2. AC-LVPECL outputs measured.

| Jitter = 65 fs RMS (12 kHz to 20 MHz) |

| fVCO1 = 2500 MHz (VCO1 inverted) |

With 155.52-MHz Output Enabled (OUT4)

| Jitter = 136 fs RMS (12 kHz to 20 MHz) | ||

| fVCO2 = 6065.28 MHz (VCO2 post-divider = 3) |

With 156.25-MHz Output Enabled (OUT3)