ZHCY200 November 2023

应对 EMI 挑战

工程师可以通过将 PFC 电感器拆分为两个元件来解决 EMI 滤波器设计难题:电感较高的电感器 (Lg) 连接到交流电源,电感较低的电感器 (Lb) 与电容器串联并与功率级并联放置,如图 13 所示。拆分电感器设置的理念是允许较大的交流纹波电流流经串联电感器和电容器(较低的总阻抗),并尽可能减小 Lb(较高阻抗)和交流电源上的电流纹波。由于差模噪声较低,因此 EMI 滤波器设计变得更简单。

图 13 修改后的图腾柱无桥 PFC 电路。

图 13 修改后的图腾柱无桥 PFC 电路。尽管修改后的软开关 CRM PFC 确实使您可以克服 EMI 滤波器设计难题,但 CRM PFC 本身需要额外的检测和控制工作来确定 PFC 有源开关导通时序,从而确保软开关。一种选择是添加电流检测器件(例如电流互感器)来检测零电流点,这样您就可以根据 FET Coss 计算有源 FET 导通时序。检测和控制系统中的传播延迟和元件容差将导致有源 FET 导通时序误差。由于该控制方案需要逐周期检测和控制,因此您应该需要更高的 MCU 资源使用量。

另一种方法是根据输入和输出电压检测结果以及 PFC 电感和 FET Coss 计算所需的 FET 导通和关断时间。然后,您可以使用 FET 漏源电压检测来确定是否实现了软开关。如果在栅极信号变为高电平之前漏源电压不变为负值,则意味着 FET 处于硬开关状态。

以图 13 所示的 FET 为例,延长 HFFET_HS 导通时间允许更多负电流将 HFFET_LS Coss 放电,从而实现软开关。如果在栅极信号变为高电平之前漏源电压变为负值,则意味着 FET 已处于软开关状态。缩短 HFFET_HS 的导通时间将更大限度地减小均方根电流,从而提高效率。这样,FET 导通时间不再在每个周期更新,而是仅在没有发生软开关时进行调整,从而节省了大量 MCU 资源。

将所需的软开关检测电路与 FET 集成可以进一步简化系统。如图 5 所示,LMG3526R030 器件在一个封装中集成了 GaN FET、驱动器、保护功能和 FET 漏源电压检测功能。只要 GaN FET 在通道导通之前处于第三象限导通状态,LMG3526R030 就会发送一个零电压检测脉冲来指示软开关。

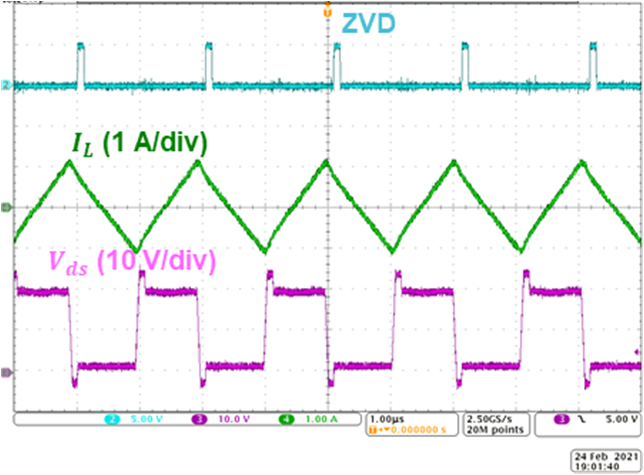

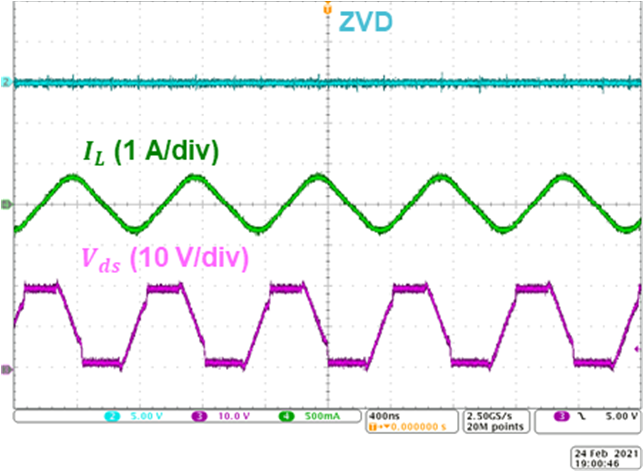

图 14 所示为具有和不具有第三象限导通的 LMG3526R030 示例波形。

图 14 具有(上面)和不具有第三象限导通的 LMG3526R030

的波形。

图 14 具有(上面)和不具有第三象限导通的 LMG3526R030

的波形。使用 LMG3526R030 中的零电压检测功能,变频、ZVS、5kW、基于 GaN 的两相图腾柱 PFC 参考设计通过结合元件、拓扑和控制系统创新技术,展示了 99.1% 以上的峰值效率。