ZHCY170 May 2017 IWR1443 , IWR1642 , IWR1843

雷达硬件加速器

雷达硬件加速器模块能够进行 FMCW 雷达信号处理中的某些常用计算,从而减轻 R4F 处理器的负担。FMCW 雷达信号处理涉及使用 FFT 和对数幅度计算,从而获得含距离、速度和角度维度的雷达图像。FMCW 雷达信号处理中的一些常用功能能够在雷达硬件加速器内执行,而与集群或物体跟踪有关的专有算法在 R4F 处理器中进行。

雷达硬件加速器的主要特性为:

- 快速 FFT 计算,具有可编程大小(2 的幂),最大为 1,024 点复数 FFT。

- 24 位(每个用于 I 和 Q)的内部 FFT 位宽可确保良好的信号与量化噪声比 (SQNR) 性能,在每个基数 2 阶段具有完全可编程的蝶式缩放,可实现用户灵活性。

- 用于进行简单前置 FFT 处理的内置功能:可编程窗口、基本二进制相位调制 (BPM) 去除和干扰消除。

- 幅度(绝对值)和对数幅度计算功能。

- 灵活的数据流和数据样本排列,能够支持高效的多维 FFT 运算并根据需要转置访问。

- 通过链接和循环机制对一组加速器操作进行排序,最大限度地减小来自主处理器的干预。

- 恒虚警率-单元平均 (CFAR-CA) 检测器,支持线性和对数模式。

- 各种各样的其他功能:FFT 拼接(高达 4k FFT)、慢离散傅里叶变换 (DFT) 和复矢量乘法功能

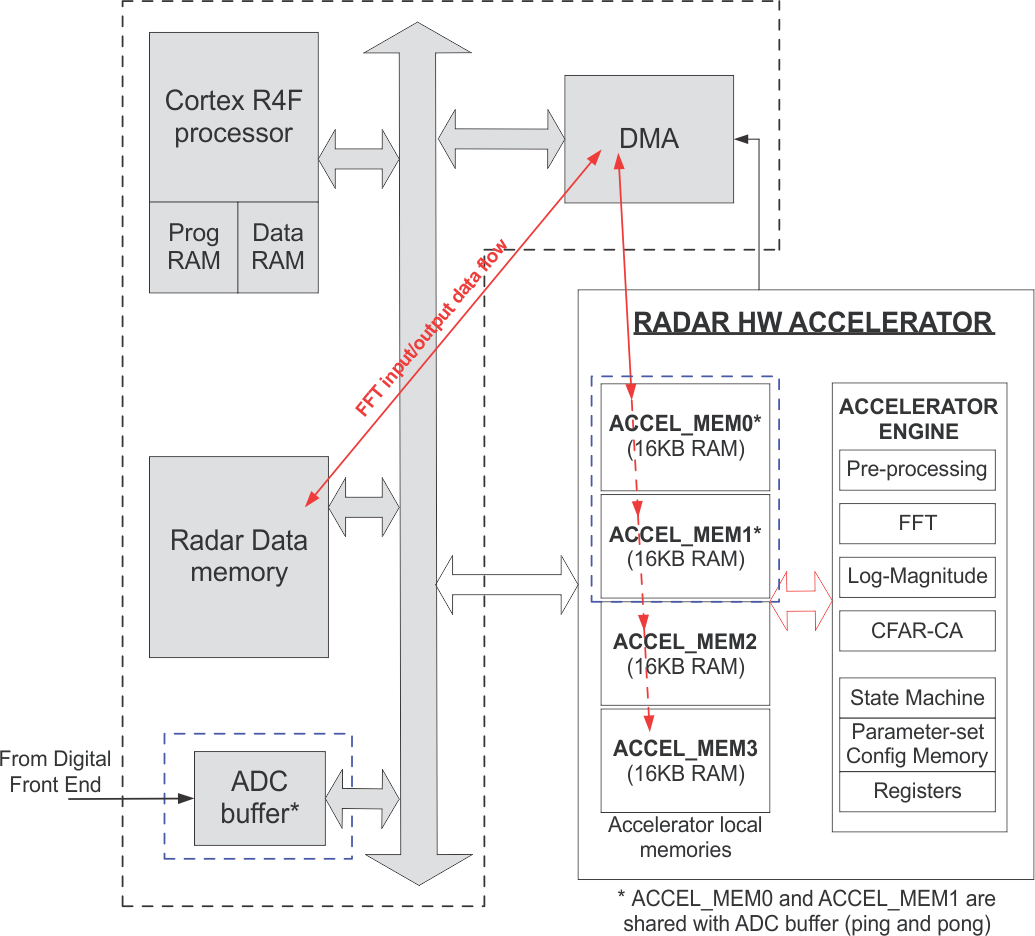

图 2 所示的雷达硬件加速器包括四个存储器(每个 16KB),用于将输入数据发送到其中并从主加速器引擎接收输出数据。这些存储器称为雷达硬件加速器的“本地存储器”,不同于上一节所描述的 576KB 总 RAM。

一般数据流是直接存储器存取 (DMA) 模块将样本(例如 FFT 输入样本)带入雷达硬件加速器的本地存储器,

图 2 雷达硬件加速器。

图 2 雷达硬件加速器。以使主加速器引擎能够访问和处理这些样本。加速器完成处理后,DMA 模块从这些本地存储器中读取输出样本,然后将它们存回雷达数据存储器或 R4F 数据 RAM 中以供 R4F 处理器进一步处理。图 2 中所示红色箭头表示执行 FFT 和其他处理步骤时数据往返于雷达数据立方体存储器以及进出本地存储器的移动方向。

雷达硬件加速器内部设置四个独立 16KB 存储器,其目的是针对输入和输出启用“乒乓”机制,使 DMA 写入(和读取)操作能与加速器的主要计算处理操作并行执行。四个存储器的存在使得这种并行机制成为可能。

有两种类型的寄存器配置雷达硬件加速器操作:“参数集”和静态(公共)寄存器。参数集可实现对完整加速器操作序列的预编程(具有适当的源和目标存储器地址以及针对该序列中每项操作而指定的其他配置),使加速器能够以最少量的 R4F 处理器干预执行这些操作。内置于加速器的状态机一次处理一个参数集配置的加载,并对预编程操作进行排序,因而 R4F 处理器不会频繁中断。

雷达硬件加速器的工作时钟频率为 200MHz。根据加速器引擎的内部架构,在初始延迟之后可实现 200MSPS 的稳态 FFT 吞吐量:每个时钟周期一个 FFT 输入和一个 FFT 输出。IWR1443 技术参考手册提供了有关加速器功能和使用过程的详细信息。