ZHCU841A August 2020 – April 2021

5.1 布局

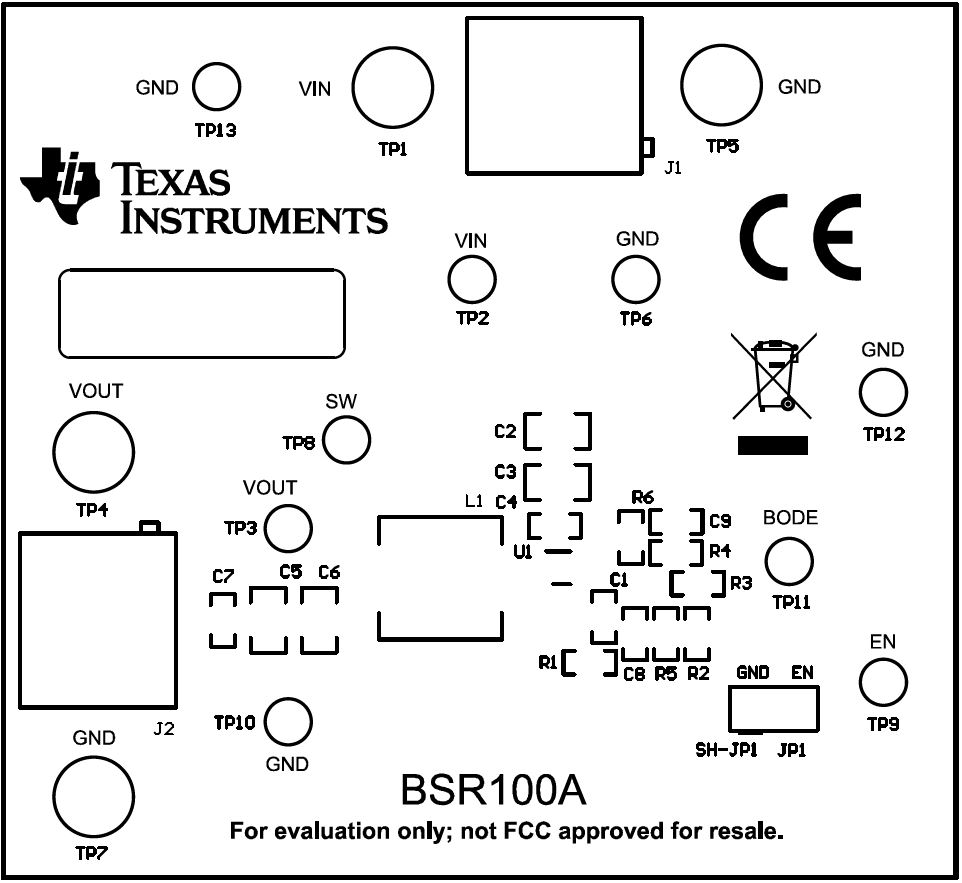

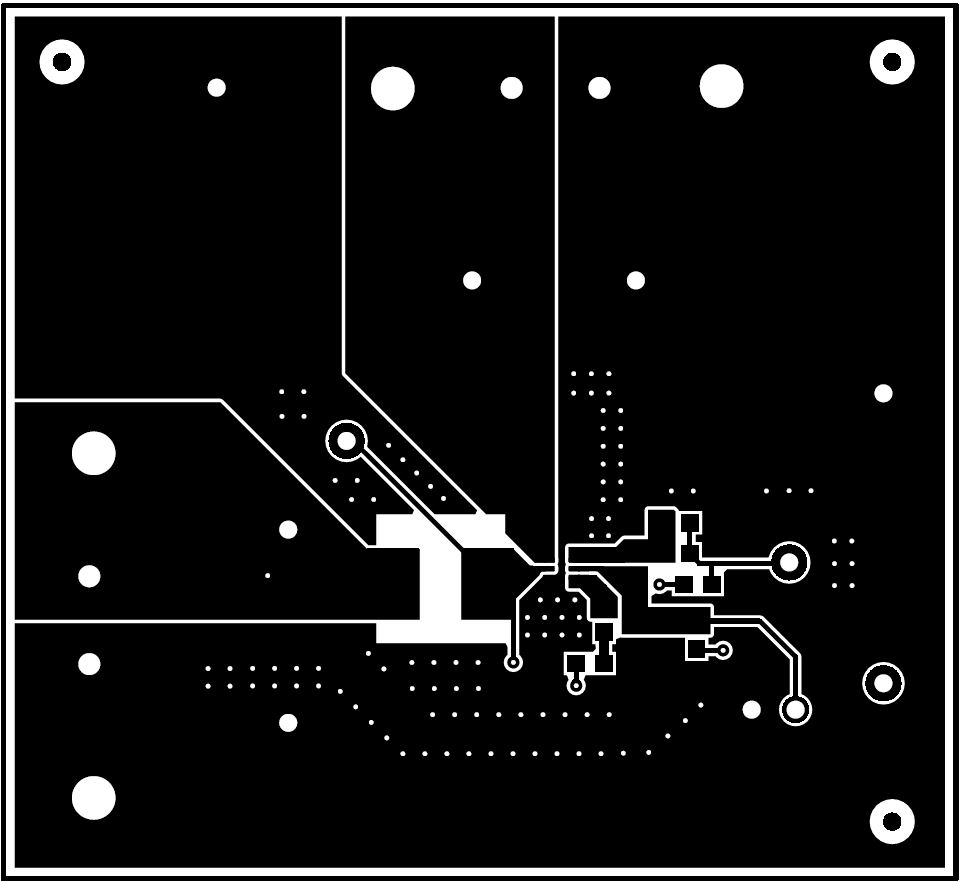

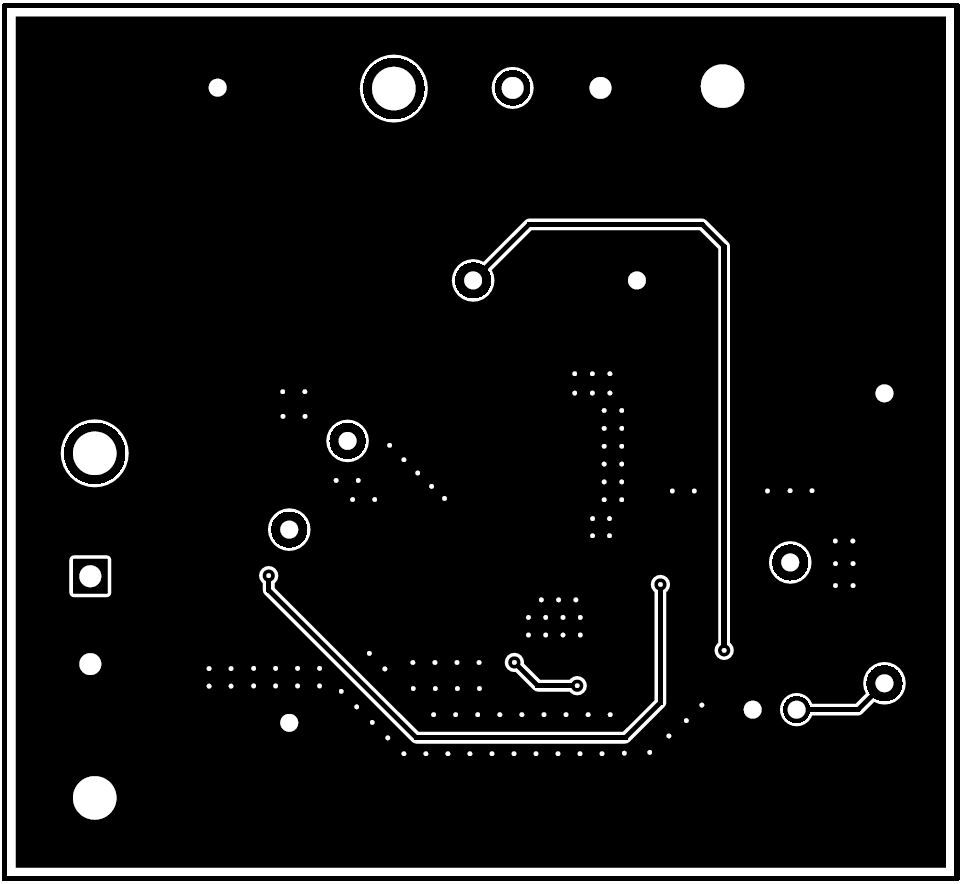

图 5-1、图 5-2 和图 5-3 显示了 TPS562202EVM 的电路板布局。顶层包含 VIN、VOUT 和接地的主要电源布线。顶层还具有 TPS562202 引脚的连接和一大块用接地线填充的区域。大多数信号布线也位于顶部。输入去耦电容器 C2、C3 和 C4 尽可能靠近 IC 放置输入和输出连接器、测试点和所有元件都位于顶部。底层是接地层以及开关节点覆铜、信号接地覆铜和从调节点到电阻分压器网络顶部的反馈布线。顶层和底层都使用 2oz 厚的覆铜。

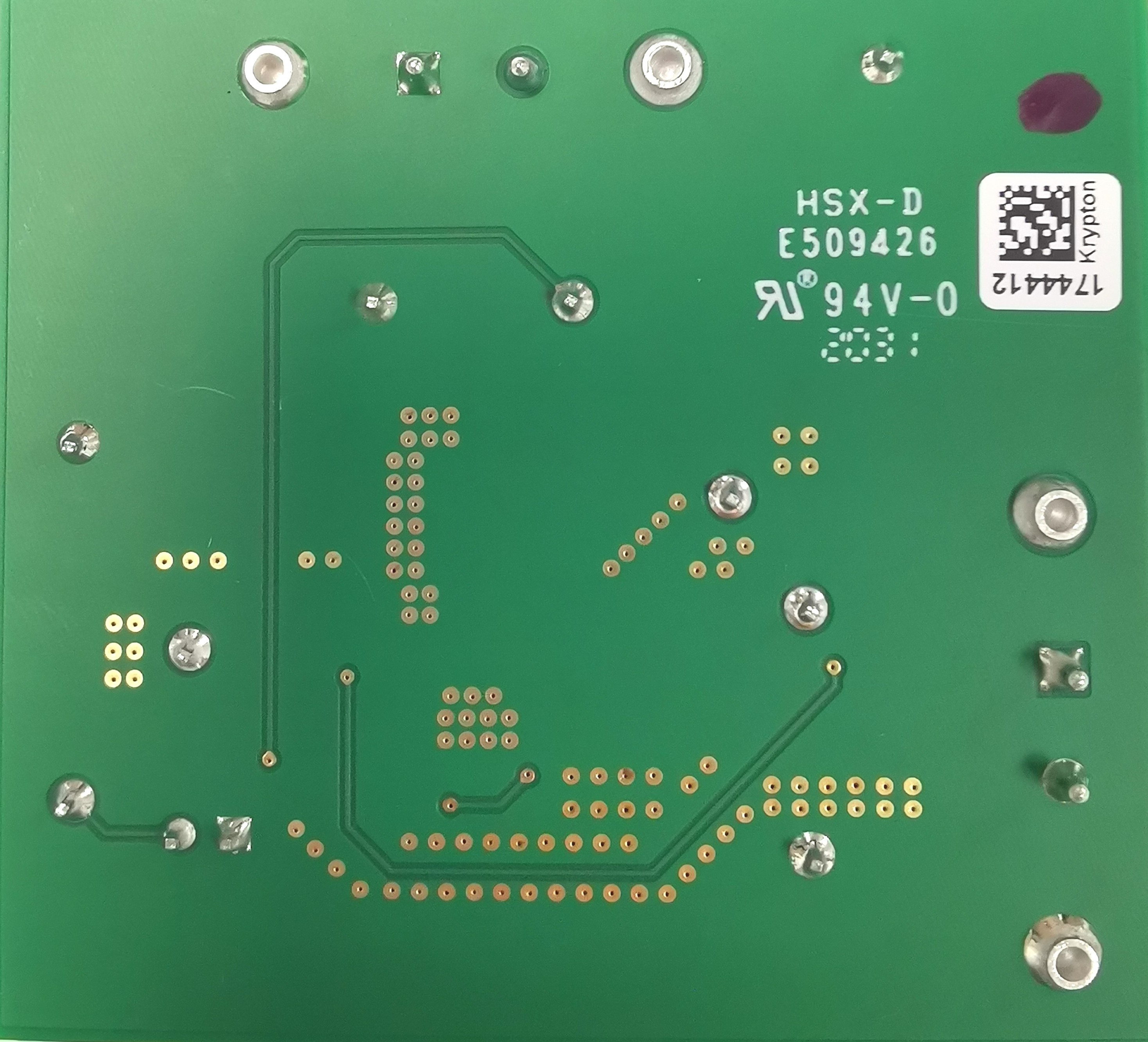

图 5-4 和图 5-5 分别是 TPS562202EVM 电路板顶视图和底视图。

图 5-1 TPS562202EVM 顶层装配图

图 5-1 TPS562202EVM 顶层装配图 图 5-2 TPS562202EVM 顶层

图 5-2 TPS562202EVM 顶层 图 5-3 TPS562202EVM 底层

图 5-3 TPS562202EVM 底层 图 5-4 TPS562202EVM 电路板顶视图

图 5-4 TPS562202EVM 电路板顶视图 图 5-5 TPS562202EVM 电路板底视图

图 5-5 TPS562202EVM 电路板底视图