ZHCSDJ6E February 2015 – June 2018 LMH1218

PRODUCTION DATA.

- 1 特性

- 2 应用

- 3 说明

- 4 修订历史记录

- 5 Pin Configuration and Functions

- 6 Specifications

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3

Feature Description

- 7.3.1 Loss of Signal Detector

- 7.3.2 Continuous Time Linear Equalizer (CTLE)

- 7.3.3 2:1 Multiplexer

- 7.3.4 Clock and Data Recovery

- 7.3.5 Eye Opening Monitor (EOM)

- 7.3.6 Fast EOM

- 7.3.7 LMH1218 Device Configuration

- 7.3.8 Power-On Reset

- 7.4 Device Functional Modes

- 7.5 Programming

- 7.6 Register Maps

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11器件和文档支持

- 12机械、封装和可订购信息

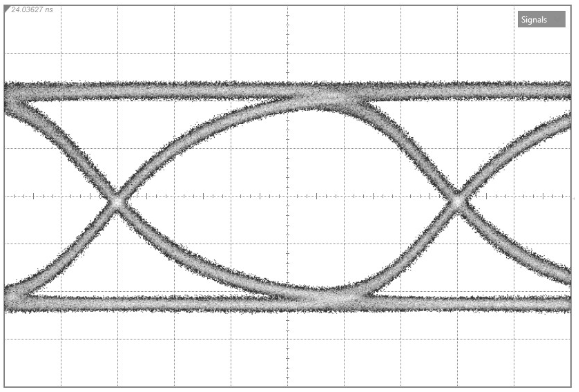

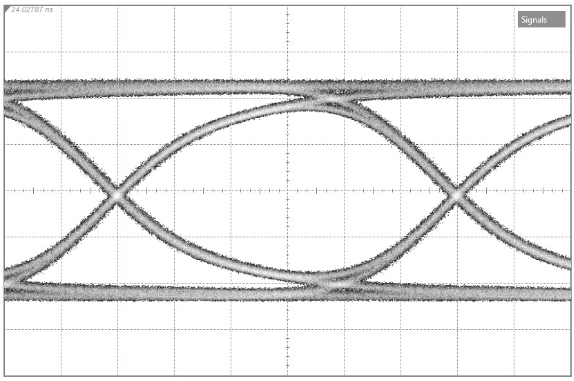

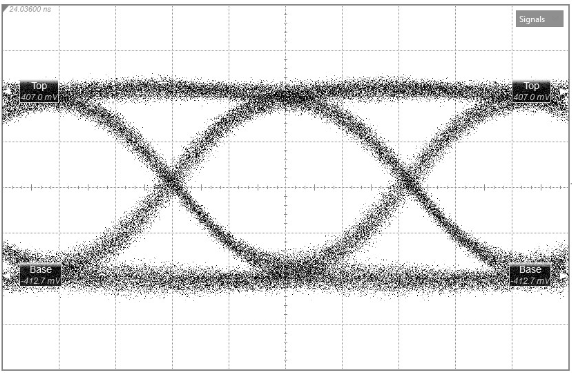

8.2.3 Application Curves

Figure 25 and Figure 27 depict the differential output eye diagrams for OUT1 at 10.3125 Gbps and 11.88 Gbps. Figure 26 depicts the single-end eye diagram for OUT0 at 11.88 Gbps. Measurements were done at default operating conditions.