SNVU753A November 2019 – May 2021

- Trademarks

- 1Introduction

- 2Description

- 3TPS542A52EVM-059 Bottom Circuit

- 4TPS542A52EVM-059 Top Circuit (Small Layout Area Design)

- 5TPS542A52EVM-059 PCB Layout

- 6List of Materials

- 7Revision History

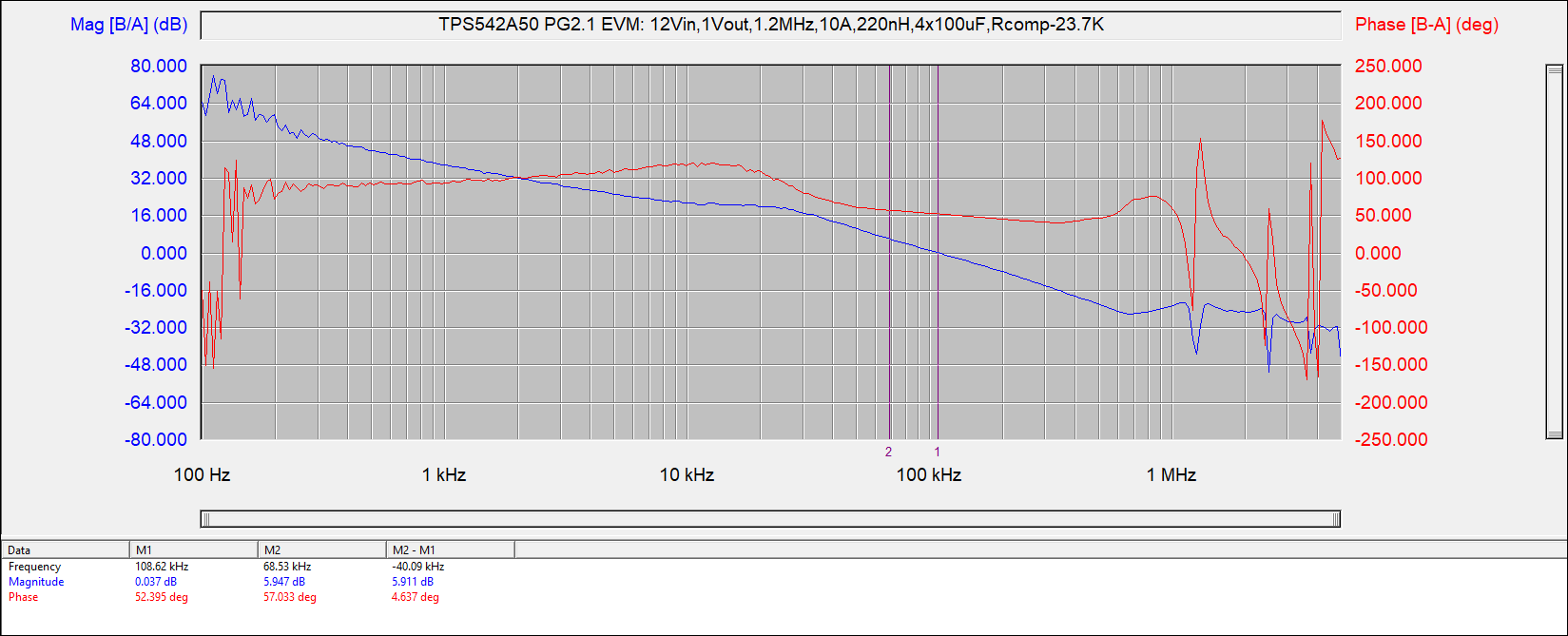

4.3.9 Loop Response

The loop response of the top circuit of the TPS542A52EVM-059 with a 10-A load is shown in Figure 4-7. The bandwidth of the loop is 105 kHz, and the phase margin is 52°.

Figure 4-7 Loop Response - IOUT = 10 A, Loop

Bandwidth = 105 kHz, Phase Margin = 52°

Figure 4-7 Loop Response - IOUT = 10 A, Loop

Bandwidth = 105 kHz, Phase Margin = 52°