SNAU279A July 2022 – September 2022

- Abstract

- Trademarks

- 1Introduction

- 2EVM Quick Start

- 3EVM Configuration

-

4EVM

Schematics

- 4.1 Power Supply Schematic

- 4.2 Alternative Power Supply Schematic

- 4.3 Power Distribution Schematic

- 4.4 LMK5B33414 and Input Reference Inputs IN0 to IN1 Schematic

- 4.5 Clock Outputs OUT0 to OUT3 Schematic

- 4.6 Clock Outputs OUT4 to OUT9 Schematic

- 4.7 Clock Outputs OUT10 to OUT13 and Clock Inputs IN2 and IN3 Schematic

- 4.8 XO Schematic

- 4.9 Logic I/O Interfaces Schematic

- 4.10 USB2ANY Schematic

- 5EVM Bill of Materials

-

6Appendix A - TICS Pro LMK5B33414 Software

- 6.1 Using the Start Page

- 6.2 Using the Status Page

- 6.3 Using the Input Page

- 6.4 Using APLL1, APLL2, and APLL3 Pages

- 6.5 Using the DPLL1, DPLL2, and DPLL3 Pages

- 6.6 Using the Validation Page

- 6.7 Using the GPIO Page

- 6.8 SYNC/SYSREF/1-PPS Page

- 6.9 Using the Outputs Page

- 6.10 EEPROM Page

- 6.11 Design Report Page

- 7Revision History

6.3.1 Cascaded Configurations

Cascaded configurations can be created using the input page, where the relevant VCO buffers and dividers will automatically be enabled by inferring the state of source selection registers.

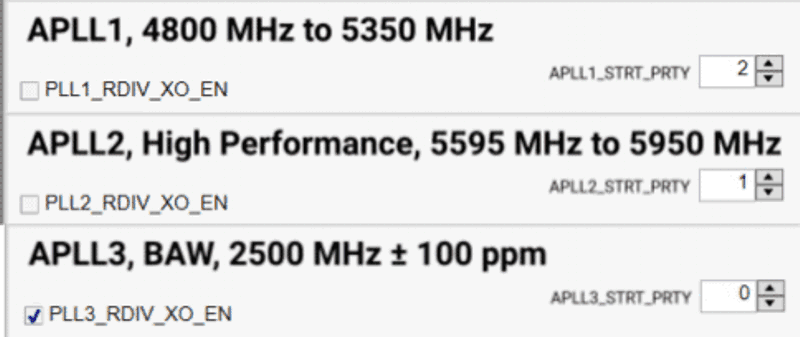

At least one PLL must always be active and set to XO reference source for cascaded configurations to be valid. APLL start-up priority will automatically choose XO-source APLLs to start up before all other PLLs whenever possible. Start-up priority cannot be properly inferred, therefore users must set this priority themselves in the User Controls page if in pin-selection mode. In the example image below, APLL3 is referenced to XO input and APLL1 and APLL2 are referenced from APLL3. Priority is controlled in ascending order, with 0 first and 2 last. APLLs can share priorities; if all APLL priorities are set to 0, all APLLs will start up simultaneously.

Figure 6-11 Cascade APLL Start Priorities.

Figure 6-11 Cascade APLL Start Priorities.