SNAU279A July 2022 – September 2022

- Abstract

- Trademarks

- 1Introduction

- 2EVM Quick Start

- 3EVM Configuration

-

4EVM

Schematics

- 4.1 Power Supply Schematic

- 4.2 Alternative Power Supply Schematic

- 4.3 Power Distribution Schematic

- 4.4 LMK5B33414 and Input Reference Inputs IN0 to IN1 Schematic

- 4.5 Clock Outputs OUT0 to OUT3 Schematic

- 4.6 Clock Outputs OUT4 to OUT9 Schematic

- 4.7 Clock Outputs OUT10 to OUT13 and Clock Inputs IN2 and IN3 Schematic

- 4.8 XO Schematic

- 4.9 Logic I/O Interfaces Schematic

- 4.10 USB2ANY Schematic

- 5EVM Bill of Materials

-

6Appendix A - TICS Pro LMK5B33414 Software

- 6.1 Using the Start Page

- 6.2 Using the Status Page

- 6.3 Using the Input Page

- 6.4 Using APLL1, APLL2, and APLL3 Pages

- 6.5 Using the DPLL1, DPLL2, and DPLL3 Pages

- 6.6 Using the Validation Page

- 6.7 Using the GPIO Page

- 6.8 SYNC/SYSREF/1-PPS Page

- 6.9 Using the Outputs Page

- 6.10 EEPROM Page

- 6.11 Design Report Page

- 7Revision History

6.1.5 Step 5

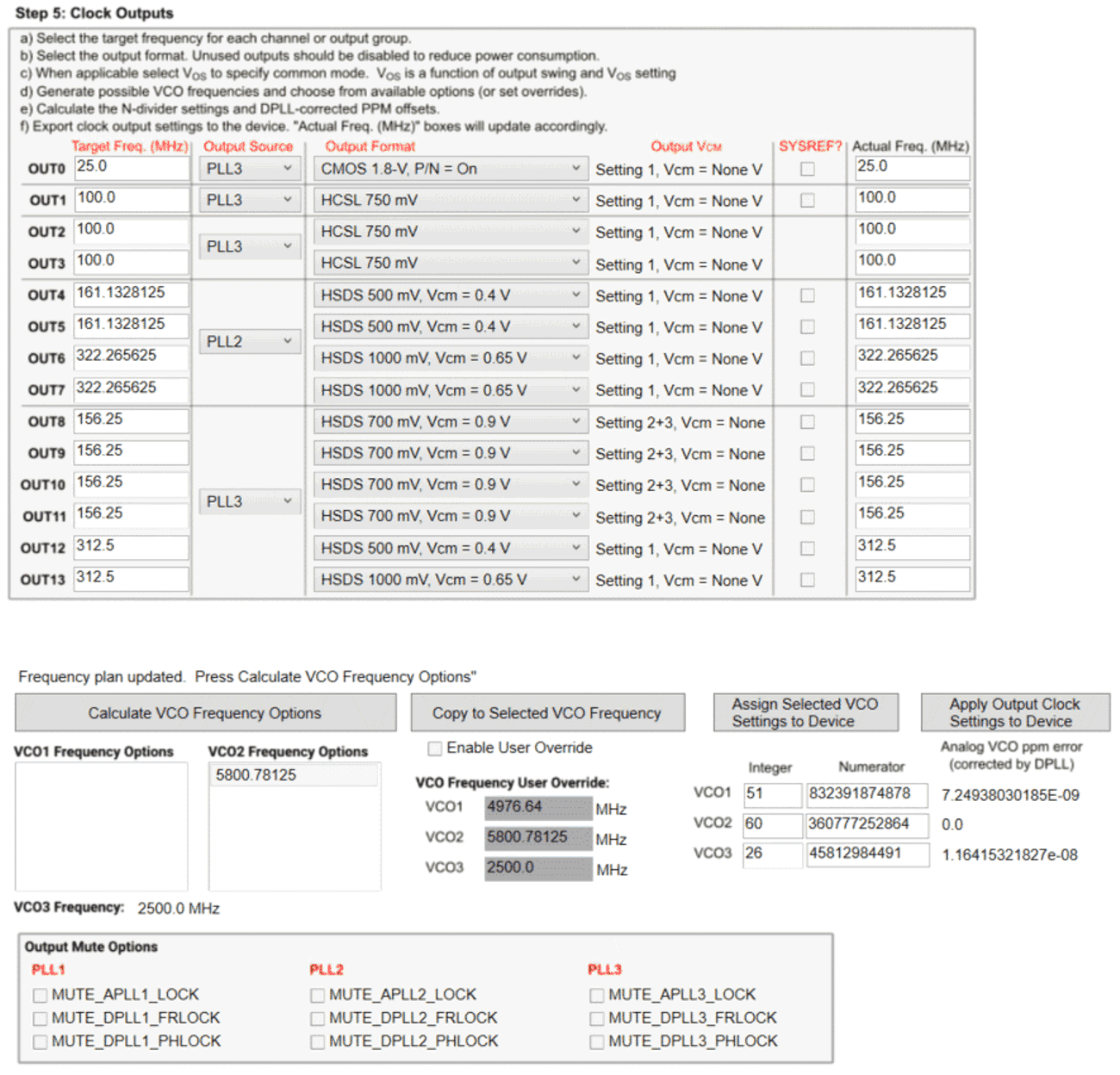

Enter the desired target frequencies for each output, as well as the desired output format, output source, whether the output is SYSREF, and whether the output is being used or not.

Press the Calculate VCO Frequency Options button to generate a list of possible VCO frequency combinations.

Figure 6-5 Step 5: Clock Outputs.

Figure 6-5 Step 5: Clock Outputs. Select a desired combination of VCO frequencies from the list of calculated values. If a specific VCO frequency is not in this list, a manual override can occur by selecting the Enable User Override checkbox and typing in the desired VCO frequencies. The Copy to Selected VCO Frequency box can also be used to copy the VCO frequency in the list selections to the VCO overrides.

Press the Assign Selected VCO Settings to Device button to update the VCO frequencies, then press the Apply Output Clock Settings to Device button. By default, the analog PLL frequencies are shown. The DPLL calculated frequency from step 6, however, will result in exact output frequencies.

After the output frequency plan is calculated, ensure that a valid XO input is fed into the device so the APLLs can lock and generate the required frequencies. The device will not output any clocks until all enabled APLLs are locked.