SBOA442 March 2021 TMP107 , TMP107-Q1

6 Test Results

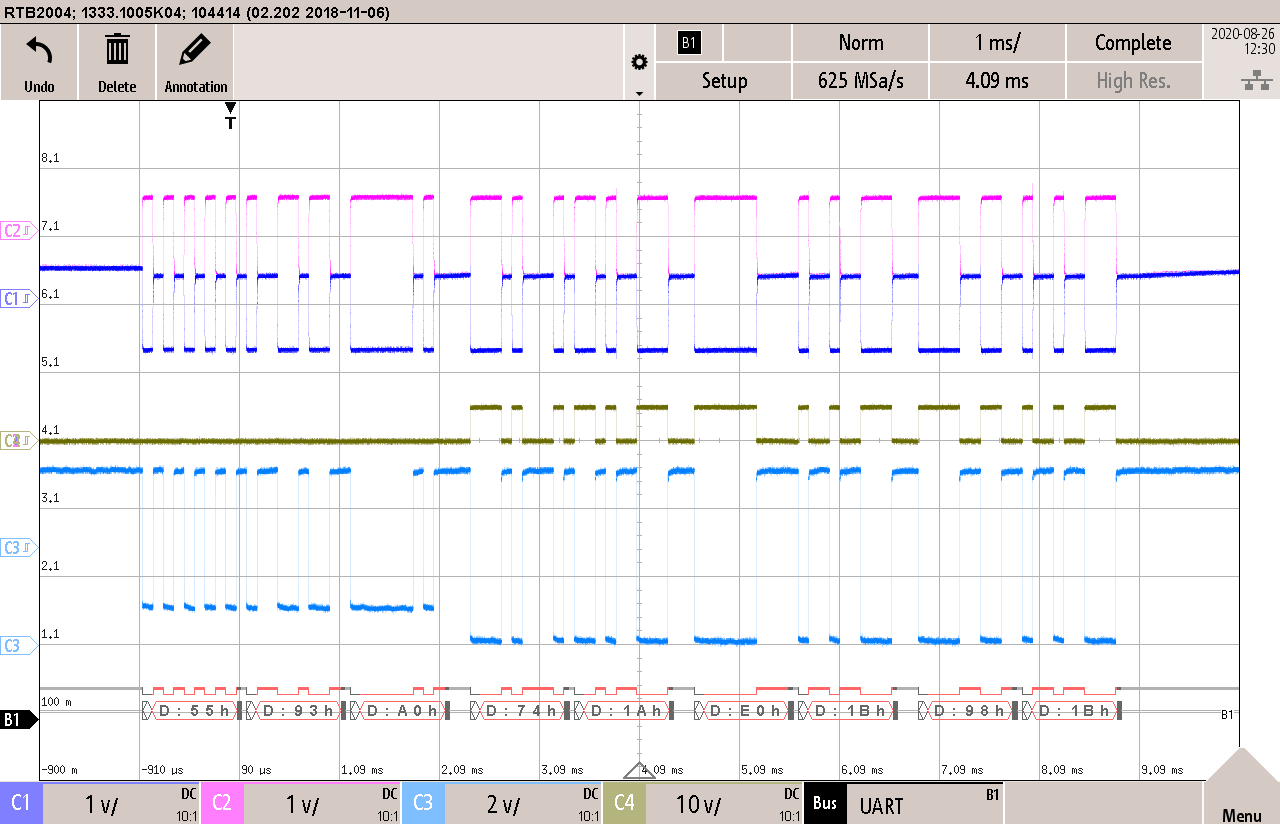

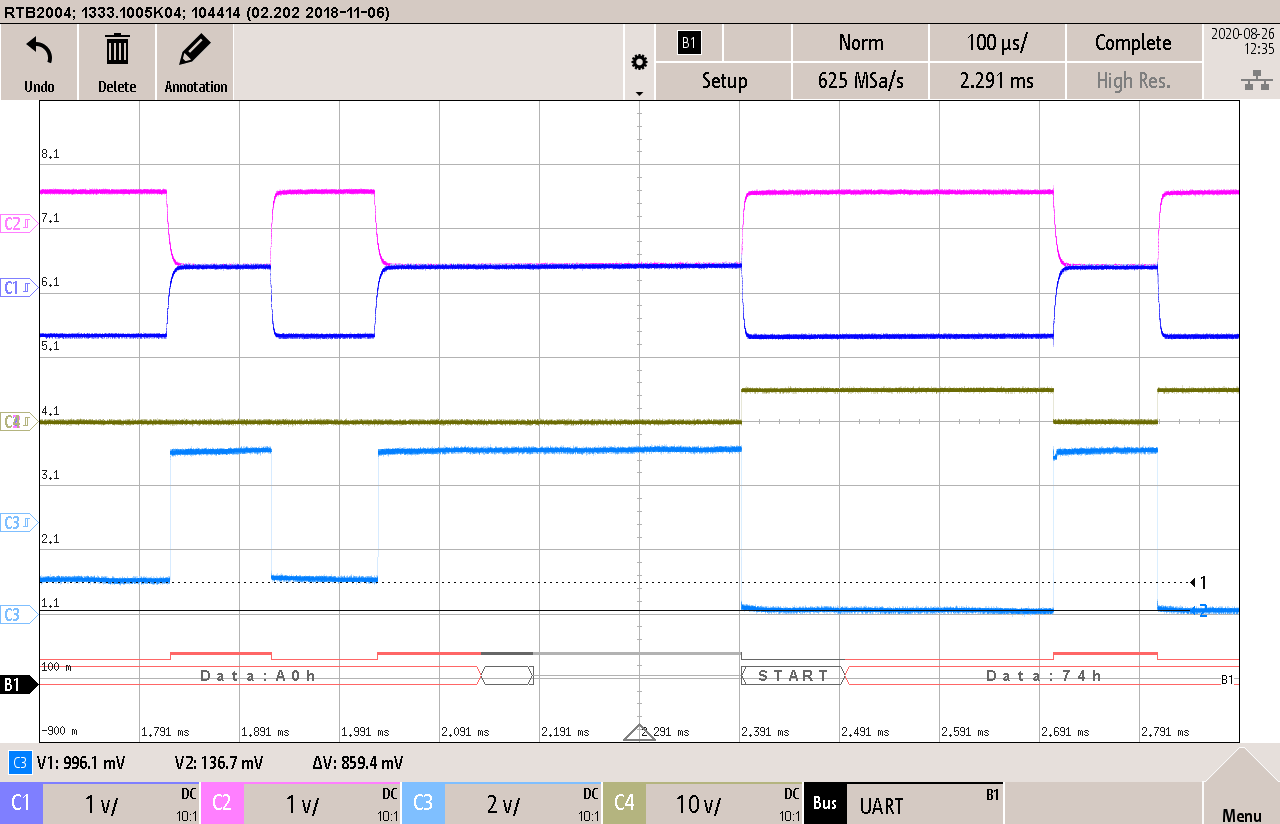

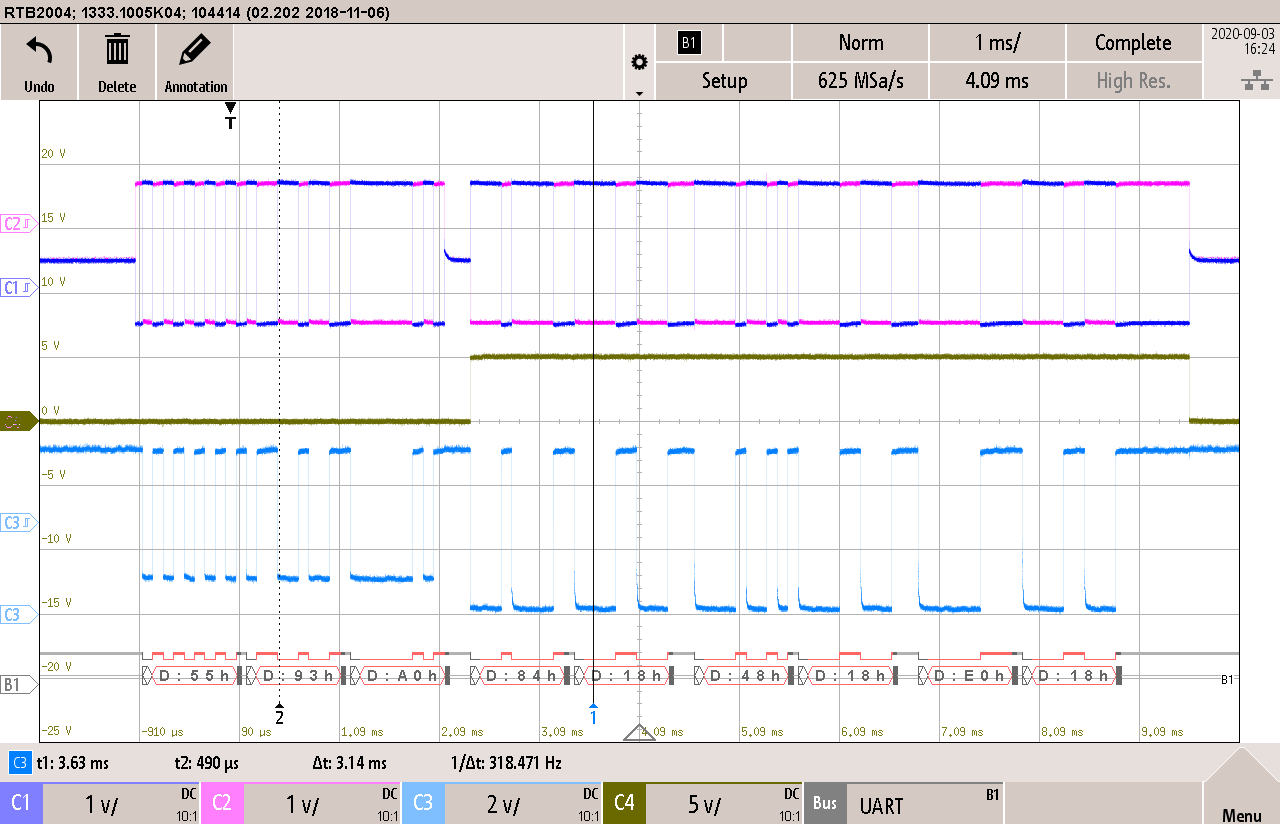

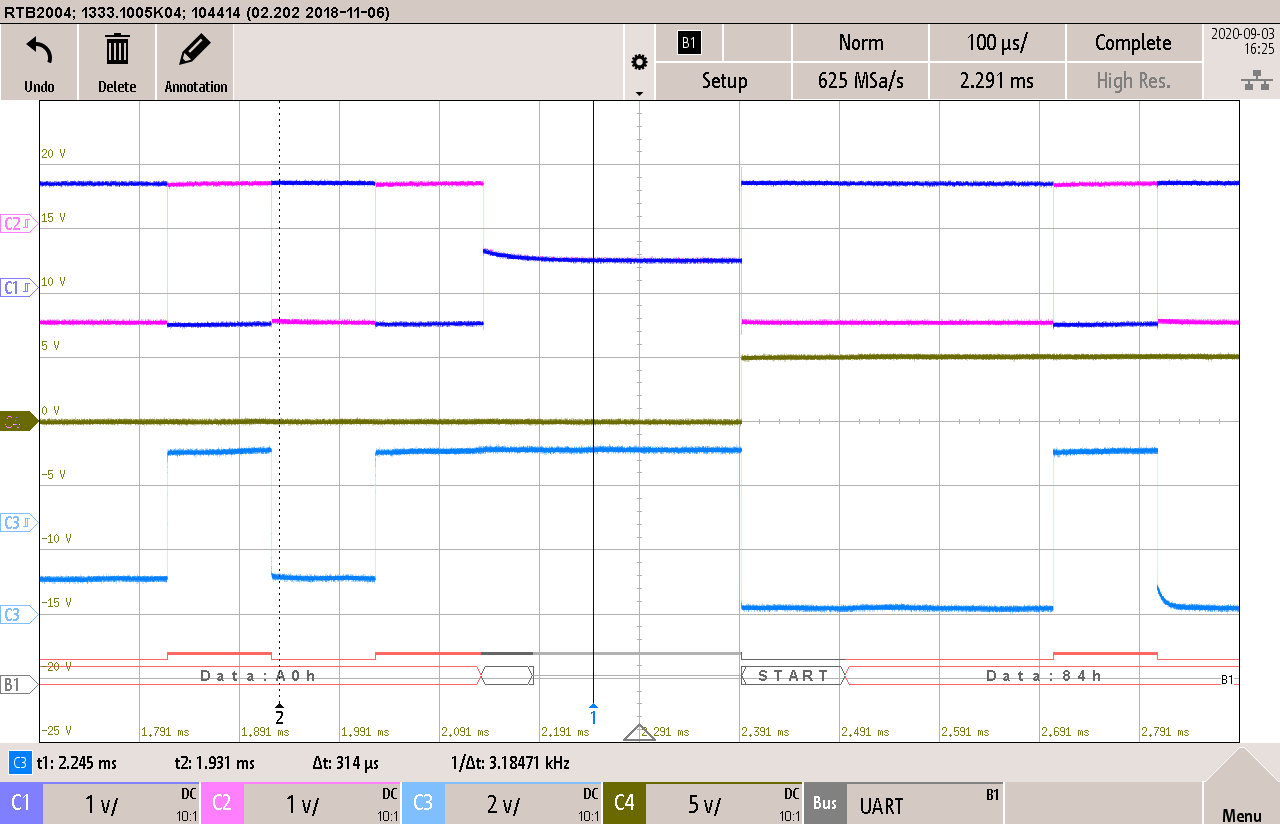

Figure 6-1 and Figure 6-2 show real waveforms for the CAN to SMAART wire interface converter circuit. The host microcontroller reads out temperature from three sensors at 9600 bps.

Channel3: I/O, Channel4: DIR

Channel3: I/O, Channel4: DIR

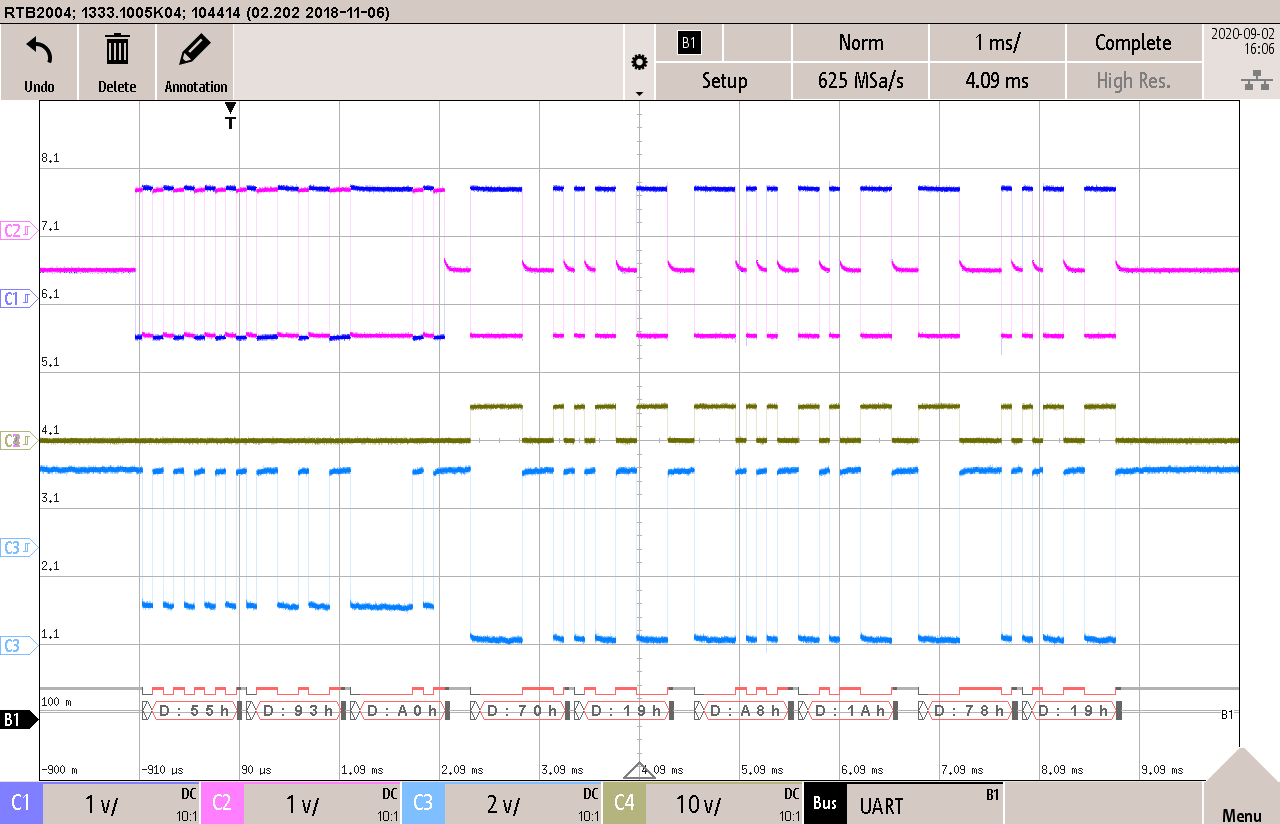

Figure 6-3 shows real waveforms for the RS-485 to SMAART wire interface converter without the timing capacitor C9. Note that during the TMP107-Q1 sensor transmitting the RS-485 bus switches only between the logic-low and idle state. The communication works because the receive data output pin R of the SN65HVC485 transceiver on the receiving side returns logic high for the properly-terminated bus in the idle state.

Figure 6-3 Real Waveforms for the

RS-485 to SMAART wire™

Interface Converter Circuit Without

Figure 6-3 Real Waveforms for the

RS-485 to SMAART wire™

Interface Converter Circuit Withoutthe Timing Capacitor C8

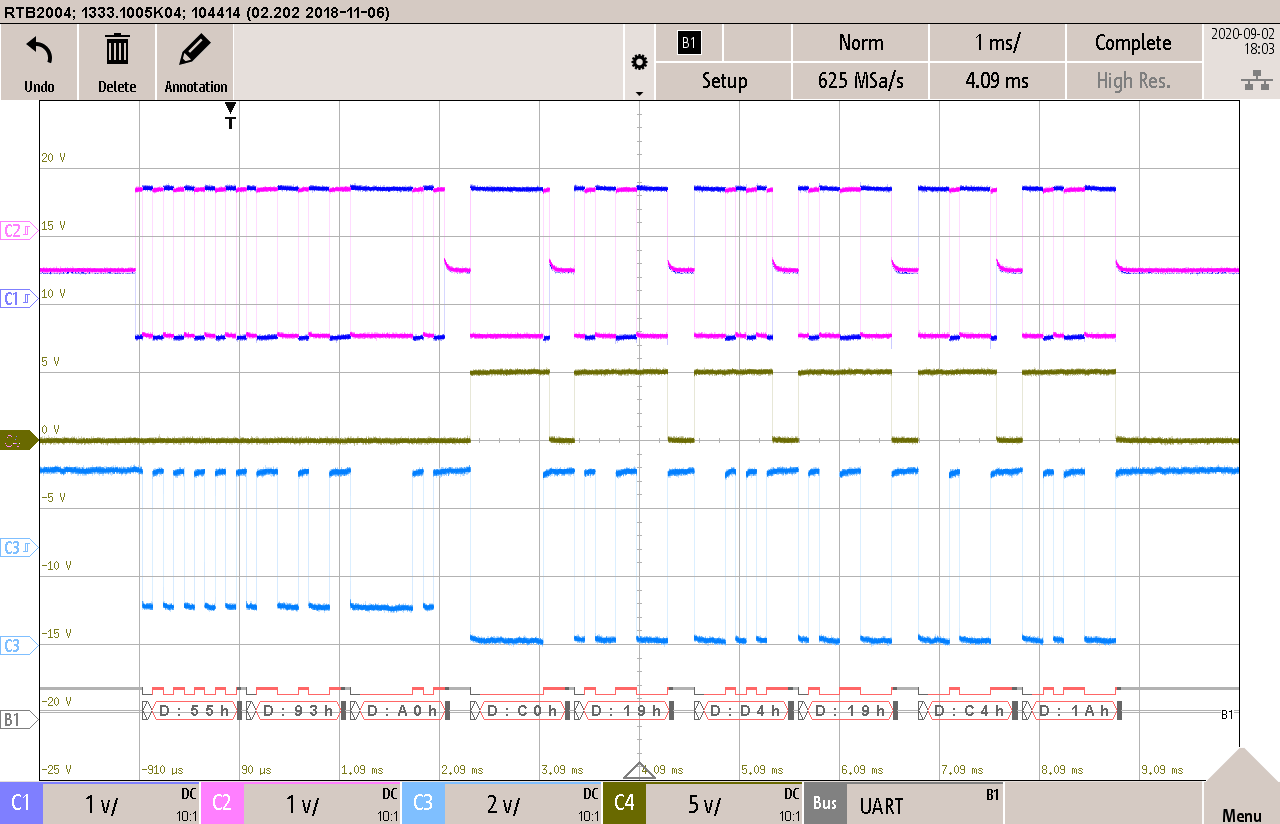

Adding the capacitor C8 (68 nF) extends the pulse and forces the RS-485 bus remaining in the active state for longer time as shown in the Figure 6-4. The control signal DIR returns to zero during transmitting the stop bit over the bus.

Figure 6-4 Real Waveforms for the

RS-485 to SMAART wire™

Interface Converter Circuit With

Figure 6-4 Real Waveforms for the

RS-485 to SMAART wire™

Interface Converter Circuit Withthe Timing Capacitor C8 (68 nF)

Figure 6-5 and Figure 6-6 show further improvement with the timing capacitor C8 and the diode D1. The diode from the timing capacitor to the I/O signal converts the circuit into re-triggable single-shot timer. At least every start bit re-triggers the timing circuitry and extends the period for which the DIR signal keeps the bus in active state.

Figure 6-5 Real Waveforms for the

RS-485 to SMAART wire™

Interface Converter Circuit With

Figure 6-5 Real Waveforms for the

RS-485 to SMAART wire™

Interface Converter Circuit Withthe Timing Capacitor C8 and Diode D1

Figure 6-6 Real Waveforms for the

RS-485 to SMAART wire™

Interface Converter Circuit With

Figure 6-6 Real Waveforms for the

RS-485 to SMAART wire™

Interface Converter Circuit Withthe Timing Capacitor C8 and Diode D1 (Detail)