SLVSAG1C December 2010 – December 2015 TPS54327

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

封装选项

机械数据 (封装 | 引脚)

散热焊盘机械数据 (封装 | 引脚)

订购信息

8 Application and Implementation

NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI’s customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

8.1 Application Information

The TPS54327 device is used as a step converter that converts a voltage of 4.5 V to 18 V to a lower voltage. WEBENCH software is available to aid in the design and analysis of circuits.

8.2 Typical Application

Figure 7. Schematic Diagram

Figure 7. Schematic Diagram

8.2.1 Design Requirements

Use the parameters in Table 1 for this application.

Table 1. TPS54327EVM-686 Performance Specifications Summary

| PARAMETERS | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| Input voltage range (VIN) | 4.5 | 12 | 18 | V | ||

| Output voltage | 1.05 | V | ||||

| Operating frequency | VIN = 12 V, IO = 1 A | 675 | kHz | |||

| Output current range | 0 | 3 | A | |||

8.2.2 Detailed Design Procedure

To begin the design process, you must know a few application parameters:

- Input voltage range

- Output voltage

- Output current

- Output voltage ripple

- Input voltage ripple

8.2.2.1 Output Voltage Resistors Selection

The output voltage is set with a resistor divider from the output node to the VFB pin. TI recommends using 1% tolerance or better divider resistors. Start by using Equation 2 to calculate VOUT.

To improve efficiency at very light loads consider using larger value resistors, too high of resistance will be more susceptible to noise and voltage errors from the VFB input current will be more noticeable.

8.2.2.2 Output Filter Selection

The output filter used with the TPS54327 is an LC circuit. This LC filter has double pole at:

At low frequencies, the overall loop gain is set by the output set-point resistor divider network and the internal gain of the TPS54327. The low-frequency phase is 180 degrees. At the output filter pole frequency, the gain rolls off at a -40 dB per decade rate and the phase drops rapidly. D-CAP2™ introduces a high-frequency zero that reduces the gain roll off to -20 dB per decade and increases the phase to 90 degrees one decade above the zero frequency. The inductor and capacitor selected for the output filter must be selected so that the double pole of Equation 3 is located below the high-frequency zero but close enough that the phase boost provided be the high-frequency zero provides adequate phase margin for a stable circuit. To meet this requirement use the values recommended in Table 2

Table 2. Recommended Component Values

| OUTPUT VOLTAGE (V) | R1 (kΩ) | R2 (kΩ) | C4 (pF) | L1 (µH) | C8 + C9 (µF) |

|---|---|---|---|---|---|

| 1 | 6.81 | 22.1 | 1.5 | 22 to 68 | |

| 1.05 | 8.25 | 22.1 | 1.5 | 22 to 68 | |

| 1.2 | 12.7 | 22.1 | 1.5 | 22 to 68 | |

| 1.8 | 30.1 | 22.1 | 5 - 22 | 2.2 | 22 to 68 |

| 2.5 | 49.9 | 22.1 | 5 - 22 | 2.2 | 22 to 68 |

| 3.3 | 73.2 | 22.1 | 5 - 22 | 2.2 | 22 to 68 |

| 5 | 124 | 22.1 | 5 - 22 | 3.3 | 22 to 68 |

| 6.5 | 165 | 22.1 | 5 - 22 | 3.3 | 22 to 68 |

Because the DC gain is dependent on the output voltage, the required inductor value will increase as the output voltage increases. For higher output voltages above 1.8 V, additional phase boost can be achieved by adding a feed forward capacitor (C4) in parallel with R1

The inductor peak-to-peak ripple current, peak current and RMS current are calculated using Equation 4, Equation 5 and Equation 6. The inductor saturation current rating must be greater than the calculated peak current and the RMS or heating current rating must be greater than the calculated RMS current. Use 700 kHz for fSW.

Use 700 kHz for fSW. Make sure the chosen inductor is rated for the peak current of Equation 5 and the RMS current of Equation 6.

For this design example, the calculated peak current is 3.47 A and the calculated RMS current is 3.01 A. The inductor used is a TDK SPM6530-1R5M100 with a peak current rating of 11.5 A and an RMS current rating of

11 A.

The capacitor value and ESR determines the amount of output voltage ripple. The TPS54327 is intended for use with ceramic or other low ESR capacitors. Recommended values range from 22uF to 68uF. Use Equation 7 to determine the required RMS current rating for the output capacitor.

For this design two TDK C3216X5R0J226M 22-µF output capacitors are used. The typical ESR is 2 mΩ each. The calculated RMS current is 0.271 A and each output capacitor is rated for 4 A.

8.2.2.3 Input Capacitor Selection

The TPS54327 requires an input decoupling capacitor and a bulk capacitor is needed depending on the application. TI recommends a ceramic capacitor over 10 μF for the decoupling capacitor. TI also recommends connecting an additional 0.1-µF capacitor from pin 14 to ground to improve the stability of the overcurrent limit function. The capacitor voltage rating must be greater than the maximum input voltage.

8.2.2.4 Bootstrap Capacitor Selection

A 0.1 µF. ceramic capacitor must be connected between the VBST to SW pin for proper operation. TI recommends using a ceramic capacitor.

8.2.2.5 VREG5 Capacitor Selection

A 1-µF ceramic capacitor must be connected between the VREG5 to GND pin for proper operation. TI recommends using a ceramic capacitor.

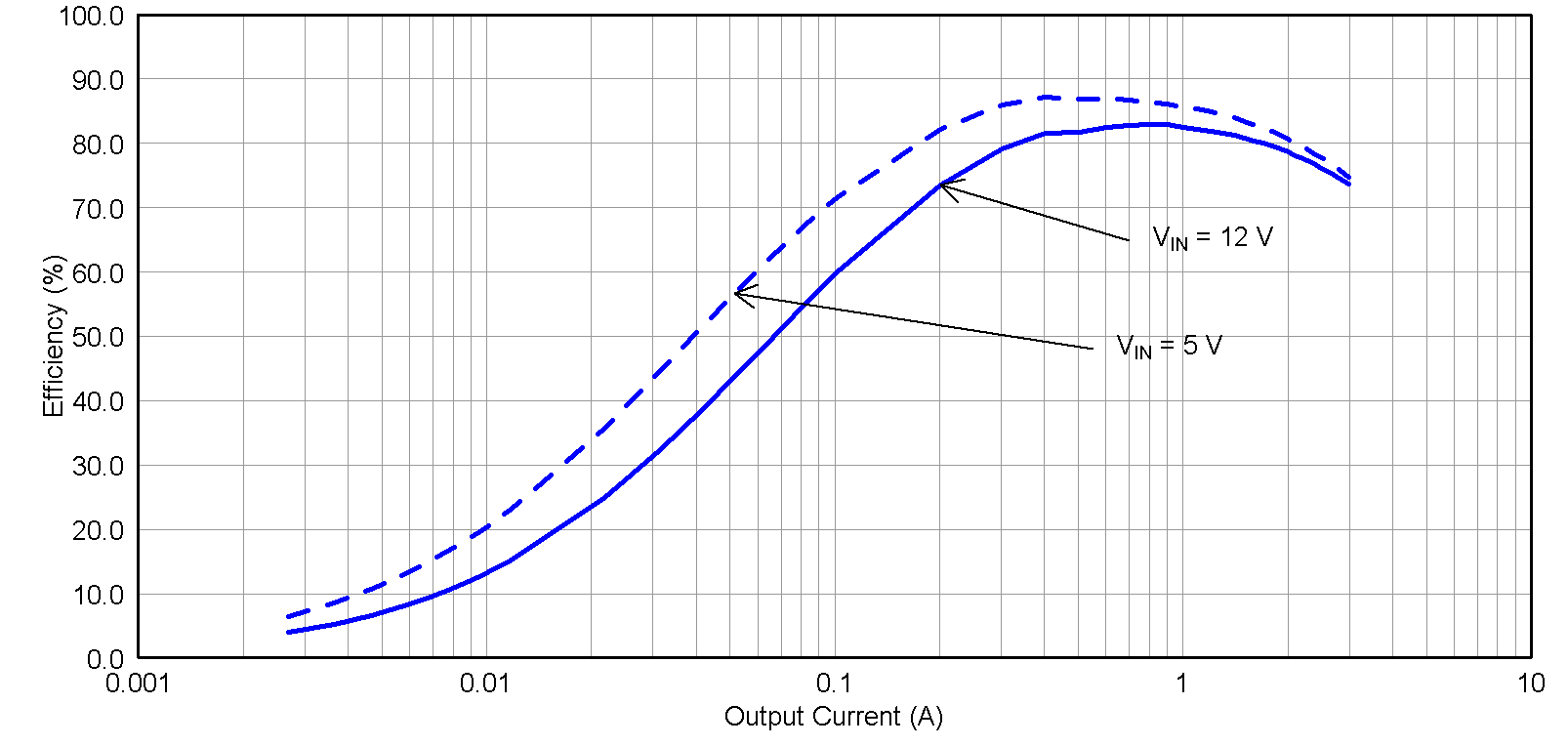

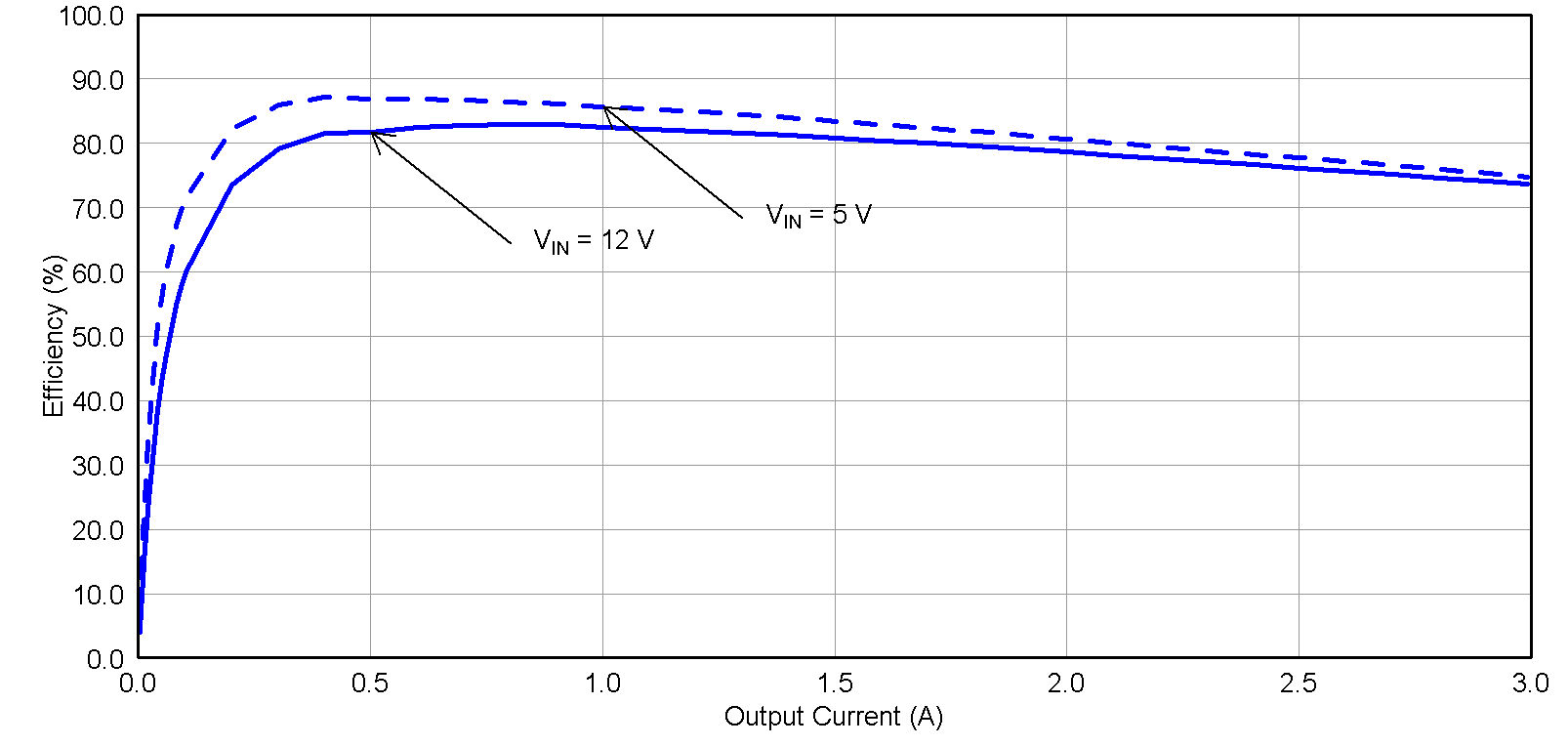

8.2.3 Application Curves

Figure 14. TPS54327EVM-686 Efficiency

Figure 14. TPS54327EVM-686 Efficiency