ZHCSDZ2A February 2013 – July 2015 THS4532

PRODUCTION DATA.

- 1 特性

- 2 应用

- 3 说明

- 4 修订历史记录

- 5 Related Products

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Detailed Description

-

9 Application and Implementation

- 9.1

Application Information

- 9.1.1 Frequency Response and Output Impedance

- 9.1.2 Distortion

- 9.1.3 Slew Rate, Transient Response, Settling Time, Overdrive, Output Voltage, and Turnon and Turnoff Time

- 9.1.4 Common-Mode and Power Supply Rejection

- 9.1.5 VOCM Input

- 9.1.6 Balance Error

- 9.1.7 Single-Supply Operation

- 9.1.8 Low-Power Applications and the Effects of Resistor Values on Bandwidth

- 9.1.9 Driving Capacitive Loads

- 9.1.10 Audio Performance

- 9.1.11 Audio On and Off Pop Performance

- 9.2 Typical Applications

- 9.3 Systems Examples

- 9.1

Application Information

- 10Power Supply Recommendations

- 11Layout

- 12器件和文档支持

- 13机械、封装和可订购信息

7 Specifications

7.1 Absolute Maximum Ratings(1)

| MIN | MAX | UNIT | ||

|---|---|---|---|---|

| Supply voltage, VS– to VS+ | 5.5 | V | ||

| Input/output voltage, VIN±, VOUT±, and VOCM pins | (VS–) – 0.7 | (VS+) + 0.7 | V | |

| Differential input voltage, VID | 1 | V | ||

| Continuous output current, IO | 50 | mA | ||

| Continuous input current, Ii | 0.75 | mA | ||

| Continuous power dissipation | See Thermal Information | |||

| Maximum junction temperature, TJ | 150 | °C | ||

| Operating junction temperature, TJ | –40 | 125 | °C | |

| Storage temperature, Tstg | –65 | 150 | °C | |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

7.2 ESD Ratings

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001(1) | ±2500 | V |

| Charged-device model (CDM), per JEDEC specification JESD22-C101(2) | ±500 | |||

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)| MIN | NOM | MAX | UNIT | ||

|---|---|---|---|---|---|

| VS+ | Single-supply voltage | 2.7 | 5 | 5.4 | V |

| TA | Ambient temperature | –40 | 25 | 125 | °C |

7.4 Thermal Information

| THERMAL METRIC (1) | THS4532 | UNIT | |

|---|---|---|---|

| TSSOP (PW) | |||

| 16 PINS | |||

| RθJA | Junction-to-ambient thermal resistance | 122.4 | °C/W |

| RθJC(top) | Junction-to-case (top) thermal resistance | 61.2 | |

| RθJB | Junction-to-board thermal resistance | 66.7 | |

| ψJT | Junction-to-top characterization parameter | 14.4 | |

| ψJB | Junction-to-board characterization parameter | 66.2 | |

| RθJC(bot) | Junction-to-case (bottom) thermal resistance | N/A | |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

7.5 Electrical Characteristics: VS = 2.7 V

Test conditions at TA = 25°C, VS+ = 2.7 V, VS– = 0 V, VOCM = +VS/2, VOUT = 2 VPP, RF = 2 kΩ, RL = 2 kΩ differential, G = 1 V/V, single-ended input, differential output, and input and output referenced to mid-supply, unless otherwise noted.| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | TEST LEVEL(1) |

|---|---|---|---|---|---|---|

| AC PERFORMANCE | ||||||

| Small-signal bandwidth | VOUT = 100 mVPP, G = 1 | 34 | MHz | C | ||

| VOUT = 100 mVPP, G = 2 | 16 | |||||

| VOUT = 100 mVPP, G = 5 | 6 | |||||

| VOUT = 100 mVPP, G = 10 | 2.7 | |||||

| Gain-bandwidth product | VOUT = 100 mVPP, G = 10 | 27 | MHz | |||

| Large-signal bandwidth | VOUT = 2 VPP, G = 1 | 34 | MHz | |||

| Bandwidth for 0.1-dB flatness | VOUT = 2 VPP, G = 1 | 12 | MHz | |||

| Slew rate, rise/fall, 25% to 75% | VOUT = 2-V step | 190/320 | V/µs | |||

| Rise/fall time, 10% to 90% | 5.2/6.1 | ns | ||||

| Settling time to 1%, rise/fall | 25/20 | ns | ||||

| Settling time to 0.1%, rise/fall | 60/60 | |||||

| Settling time to 0.01%, rise/fall | 150/110 | ns | ||||

| Overshoot/undershoot, rise/fall | 1/1% | |||||

| 2nd-order harmonic distortion | f = 1 kHz, VOUT = 1 VRMS | –122 | dBc | |||

| f = 10 kHz | –127 | |||||

| f = 1 MHz | –59 | |||||

| 3rd-order harmonic distortion | f = 1 kHz, VOUT = 1 VRMS | –130 | dBc | |||

| f = 10 kHz | –135 | |||||

| f = 1 MHz | –70 | |||||

| 2nd-order intermodulation distortion | f = 1 MHz, 200-kHz tone spacing, VOUT envelope = 2 VPP |

–83 | dBc | |||

| 3rd-order intermodulation distortion | –81 | |||||

| Input voltage noise | f = 1 kHz | 10 | nV/√Hz | |||

| Voltage noise 1/f corner frequency | 45 | Hz | ||||

| Input current noise | f = 100 kHz | 0.25 | pA/√Hz | |||

| Current noise 1/f corner frequency | 6.5 | kHz | ||||

| Overdrive recovery time | Overdrive = 0.5 V | 65 | ns | |||

| Output balance error | VOUT = 100 mV, f = 1 MHz | –65 | dB | |||

| Closed-loop output impedance | f = 1 MHz (differential) | 2.5 | Ω | |||

| Channel-to-channel crosstalk | f = 10 kHz, measured differentially | -133 | dB | |||

| DC PERFORMANCE | ||||||

| Open-loop voltage gain (AOL) | 100 | 113 | dB | A | ||

| Input-referred offset voltage | TA = 25°C | ±80 | ±400 | µV | A | |

| TA = 0°C to 70°C | ±715 | B | ||||

| TA = –40°C to 85°C | ±855 | |||||

| TA = –40°C to 125°C | ±1300 | |||||

| Input offset voltage drift(2) | TA = 0°C to 70°C | ±2 | ±7 | µV/°C | B | |

| TA = –40°C to 85°C | ±2 | ±7 | ||||

| TA = –40°C to 125°C | ±3 | ±9 | ||||

| Input bias current | TA = 25°C | 200 | 250 | nA | A | |

| TA = 0°C to 70°C | 275 | B | ||||

| TA = –40°C to 85°C | 286 | |||||

| TA = –40°C to 125°C | 305 | |||||

| Input bias current drift(2) | TA = 0°C to 70°C | 0.45 | 0.55 | nA/°C | B | |

| TA = –40°C to 85°C | 0.45 | 0.55 | ||||

| TA = –40°C to 125°C | 0.45 | 0.55 | ||||

| Input offset current | TA = 25°C | ±5 | ±50 | nA | A | |

| TA = 0°C to 70°C | ±55 | B | ||||

| TA = –40°C to 85°C | ±57 | |||||

| TA = –40°C to 125°C | ±60 | |||||

| Input offset current drift(2) | TA = 0°C to 70°C | ±0.03 | ±0.1 | nA/°C | B | |

| TA = –40°C to 85°C | ±0.03 | ±0.1 | ||||

| TA = –40°C to 125°C | ±0.03 | ±0.1 | ||||

| INPUT | ||||||

| Common-mode input low | TA = 25°C, CMRR > 87 dB | VS– – 0.2 | VS– | V | A | |

| TA = –40°C to 125°C, CMRR > 87 dB | VS– – 0.2 | VS– | B | |||

| Common-mode input high | TA = 25°C, CMRR > 87 dB | VS+ – 1.2 | VS+ – 1.1 | V | A | |

| TA = –40°C to 125°C, CMRR > 87 dB | VS+ – 1.2 | VS+ – 1.1 | B | |||

| Common-mode rejection ratio | 90 | 116 | dB | A | ||

| Input impedance common-mode | 200 || 1.2 | kΩ || pF | C | |||

| Input impedance differential mode | 200 || 1 | C | ||||

| OUTPUT | ||||||

| Single-ended output voltage: low | TA = 25°C | VS– + 0.06 | VS– + 0.2 | V | A | |

| TA = –40°C to 125°C | VS– + 0.06 | VS– + 0.2 | B | |||

| Single-ended output voltage: high | TA = 25°C | VS+ – 0.2 | VS+ – 0.11 | V | A | |

| TA = –40°C to 125°C | VS+ – 0.2 | VS+ – 0.11 | B | |||

| Output saturation voltage: high/low | 110/60 | mV | C | |||

| Linear output current drive | TA = 25°C | ±15 | ±22 | mA | A | |

| TA = –40°C to 125°C | ±15 | B | ||||

| POWER SUPPLY | ||||||

| Specified operating voltage | 2.5 | 5.5 | V | B | ||

| Quiescent operating current/ch | TA = 25°C, PD = VS+ | 230 | 330 | µA | A | |

| TA = –40°C to 125°C, PD = VS+ | 270 | 370 | B | |||

| Power-supply rejection (PSRR) | 87 | 108 | dB | A | ||

| POWER DOWN | ||||||

| Enable voltage threshold | Specified on above 2.1 V | 2.1 | V | A | ||

| Disable voltage threshold | Specified off below 0.7 V | 0.7 | V | A | ||

| Disable pin bias current | PD = VS– + 0.5 V | 50 | 500 | nA | A | |

| Power-down quiescent current | PD = VS– + 0.5 V | 0.5 | 2 | µA | A | |

| Turn-on time delay | Time from PD = high to VOUT = 90% of final value, RL= 200 Ω | 650 | ns | C | ||

| Turn-off time delay | Time from PD = low to VOUT = 10% of original value, RL= 200 Ω | 20 | ns | C | ||

| OUTPUT COMMON-MODE VOLTAGE CONTROL (VOCM) | ||||||

| Small-signal bandwidth | VOCM input = 100 mVPP | 23 | MHz | C | ||

| Slew rate | VOCM input = 1 VSTEP | 14 | V/µs | C | ||

| Gain | 0.99 | 0.996 | 1.01 | V/V | A | |

| Common-mode offset voltage | Offset = output common-mode voltage – VOCM input voltage | ±1 | ±5 | mV | A | |

| VOCM input bias current | VOCM = (VS+ – VS–)/2 | ±20 | ±100 | nA | A | |

| VOCM input voltage range | 0.8 | 0.75 to 1.9 | 1.75 | V | A | |

| VOCM input impedance | 100 || 1.6 | kΩ || pF | C | |||

| Default voltage offset from (VS+ – VS–)/2 |

Offset = output common-mode voltage – (VS+ – VS–)/2 | ±3 | ±10 | mV | A | |

(1) Test levels (all values set by characterization and simulation): (A) 100% tested at +25°C; over temperature limits by characterization and simulation. (B) Not tested in production; limits set by characterization and simulation. (C) Typical value only for information.

7.6 Electrical Characteristics: VS = 5 V

Test conditions at TA = +25°C, VS+ = 5 V, VS– = 0 V, VOCM = open, VOUT = 2 VPP, RF = 2 kΩ, RL = 2 kΩ differential, G = 1 V/V, single-ended input, differential output, and input and output referenced to mid-supply, unless otherwise noted.| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | TEST LEVEL(1) |

|---|---|---|---|---|---|---|

| AC PERFORMANCE | ||||||

| Small-signal bandwidth | VOUT = 100 mVPP, G = 1 | 36 | MHz | C | ||

| VOUT = 100 mVPP, G = 2 | 17 | |||||

| VOUT = 100 mVPP, G = 5 | 6 | |||||

| VOUT = 100 mVPP, G = 10 | 2.7 | |||||

| Gain-bandwidth product | VOUT = 100 mVPP, G = 10 | 27 | MHz | |||

| Large-signal bandwidth | VOUT = 2 VPP, G = 1 | 36 | MHz | |||

| Bandwidth for 0.1-dB flatness | VOUT = 2 VPP, G = 1 | 15 | MHz | |||

| Slew rate, rise/fall, 25% to 75% | VOUT = 2 VStep | 220/390 | V/µs | |||

| Rise/fall time, 10% to 90% | 4.6/5.6 | ns | ||||

| Settling time to 1%, rise/fall | 25/20 | ns | ||||

| Settling time to 0.1%, rise/fall | 60/60 | ns | ||||

| Settling time to 0.01%, rise/fall | 150/110 | ns | ||||

| Overshoot/undershoot, rise/fall | 1/1% | |||||

| 2nd-order harmonic distortion | f = 1 kHz, VOUT = 1 VRMS | –122 | dBc | |||

| f = 10 kHz | –128 | |||||

| f = 1 MHz | –60 | |||||

| 3rd-order harmonic distortion | f = 1 kHz, VOUT = 1 VRMS | –130 | dBc | |||

| f = 10 kHz | –137 | |||||

| f = 1 MHz | –71 | |||||

| 2nd-order intermodulation distortion | f = 1 MHz, 200-kHz tone spacing, VOUT envelope = 2 VPP |

–85 | dBc | |||

| 3rd-order intermodulation distortion | –83 | dBc | ||||

| Input voltage noise | f = 1 kHz | 10 | nV/√Hz | |||

| Voltage noise 1/f corner frequency | 45 | Hz | ||||

| Input current noise | f = 100 kHz | 0.25 | pA/√Hz | |||

| Current noise 1/f corner frequency | 6.5 | kHz | ||||

| Overdrive recovery time | Overdrive = 0.5 V | 65 | ns | |||

| Output balance error | VOUT = 100 mV, f = 1 MHz | –67 | dB | |||

| Closed-loop output impedance | f = 1 MHz (differential) | 2.5 | Ω | |||

| Channel-to-channel crosstalk | f = 10 kHz, measured differentially | -133 | dB | |||

| DC PERFORMANCE | ||||||

| Open-loop voltage gain (AOL) | 100 | 114 | dB | A | ||

| Input-referred offset voltage | TA = 25°C | ±80 | ±400 | µV | A | |

| TA = 0°C to 70°C | ±715 | B | ||||

| TA = –40°C to 85°C | ±855 | |||||

| TA = –40°C to 125°C | ±1300 | |||||

| Input offset voltage drift(2) | TA = 0°C to 70°C | ±2 | ±7 | µV/°C | B | |

| TA = –40°C to 85°C | ±2 | ±7 | ||||

| TA = –40°C to 125°C | ±3 | ±9 | ||||

| Input bias current | TA = 25°C | 200 | 250 | nA | A | |

| TA = 0°C to 70°C | 279 | B | ||||

| TA = –40°C to 85°C | 292 | |||||

| TA = –40°C to 125°C | 315 | |||||

| Input bias current drift(2) | TA = 0°C to 70°C | 0.5 | 0.65 | nA/°C | B | |

| TA = –40°C to 85°C | 0.5 | 0.65 | ||||

| TA = –40°C to 125°C | 0.5 | 0.65 | ||||

| Input offset current | TA = 25°C | ±5 | ±50 | nA | A | |

| TA = 0°C to 70°C | ±55 | B | ||||

| TA = –40°C to 85°C | ±57 | |||||

| TA = –40°C to 125°C | ±60 | |||||

| Input offset current drift(2) | TA = 0°C to 70°C | ±0.03 | ±0.1 | nA/°C | B | |

| TA = –40°C to 85°C | ±0.03 | ±0.1 | ||||

| TA = –40°C to 125°C | ±0.03 | ±0.1 | ||||

| INPUT | ||||||

| Common-mode input: low | TA = 25°C, CMRR > 87 dB | VS– – 0.2 | VS– | V | A | |

| TA = –40°C to 125°C, CMRR > 87 dB | VS– – 0.2 | VS– | B | |||

| Common-mode input: high | TA = 25°C, CMRR > 87 dB | VS+ – 1.2 | VS+ –1.1 | V | A | |

| TA = –40°C to 125°C, CMRR > 87 dB | VS+ – 1.2 | VS+ –1.1 | B | |||

| Common-mode rejection ratio | 90 | 116 | dB | A | ||

| Input impedance common-mode | 200 || 1.2 | kΩ || pF | C | |||

| Input impedance differential mode | 200 || 1 | C | ||||

| OUTPUT | ||||||

| Linear output voltage: low | TA = 25°C | VS– + 0.1 | VS– + 0.2 | V | A | |

| TA = –40°C to 125°C | VS– + 0.1 | VS– + 0.2 | V | B | ||

| Linear output voltage: high | TA = 25°C | VS+ – 0.25 | VS+ – 0.12 | V | A | |

| TA = –40°C to 125°C | VS+ – 0.25 | VS+ – 0.12 | V | B | ||

| Output saturation voltage: high/low | 120/100 | mV | C | |||

| Linear output current drive | TA = 25°C | ±15 | ±25 | mA | A | |

| TA = –40°C to 125°C | ±15 | B | ||||

| POWER SUPPLY | ||||||

| Specified operating voltage | 2.5 | 5.5 | V | B | ||

| Quiescent operating current/ch | TA = 25°C, PD = VS+ | 250 | 350 | µA | A | |

| TA = –40°C to 125°C, PD = VS+ | 290 | 390 | B | |||

| Power-supply rejection (PSRR) | 87 | 108 | dB | A | ||

| POWER DOWN | ||||||

| Enable voltage threshold | Specified on above 2.1 V | 2.1 | V | A | ||

| Disable voltage threshold | Specified off below 0.7 V | 0.7 | V | A | ||

| Disable pin bias current | PD = VS– + 0.5 V | 50 | 500 | nA | A | |

| Power-down quiescent current | PD = VS– + 0.5 V | 0.5 | 2 | µA | A | |

| Turn-on time delay | Time from PD = high to VOUT = 90% of final value, RL= 200 Ω | 600 | ns | C | ||

| Turn-off time delay | Time from PD = low to VOUT = 10% of original value, RL= 200 Ω | 15 | ns | C | ||

| OUTPUT COMMON-MODE VOLTAGE CONTROL (VOCM) | ||||||

| Small-signal bandwidth | VOCM input = 100 mVPP | 24 | MHz | C | ||

| Slew rate | VOCM input = 1 VSTEP | 15 | V/µs | C | ||

| Gain | 0.99 | 0.996 | 1.01 | V/V | A | |

| Common-mode offset voltage | Offset = output common-mode voltage – VOCM input voltage | ±1 | ±5 | mV | A | |

| VOCM input bias current | VOCM = (VS+ – VS–)/2 | ±20 | ±120 | nA | A | |

| VOCM input voltage range | 0.95 | 0.75 to 4.15 | 4.0 | V | A | |

| VOCM input impedance | 65 || 0.86 | kΩ || pF | C | |||

| Default voltage offset from (VS+ – VS–)/2 |

Offset = output common-mode voltage – (VS+ – VS–)/2 | ±3 | ±10 | mV | A | |

(1) Test levels (all values set by characterization and simulation): (A) 100% tested at +25°C; over temperature limits by characterization and simulation. (B) Not tested in production; limits set by characterization and simulation. (C) Typical value only for information.

(2) Input offset voltage drift, input bias current drift, and input offset current drift are average values calculated by taking data at the end points, computing the difference, and dividing by the temperature range.

7.7 Typical Characteristics

Table 3. Table of Graphs

| DESCRIPTION | VS = 2.7 V | VS = 5 V |

|---|---|---|

| Small-signal frequency response | Figure 1 | Figure 35 |

| Large-signal frequency response | Figure 2 | Figure 36 |

| Large- and small- signal pulse response | Figure 3 | Figure 37 |

| Single-ended slew rate vs VOUT step | Figure 4 | Figure 38 |

| Differential slew rate vs VOUT step | Figure 5 | Figure 39 |

| Overdrive recovery | Figure 6 | Figure 40 |

| 10-kHz FFT on audio analyzer | Figure 7 | Figure 41 |

| Harmonic distortion vs Frequency | Figure 8 | Figure 42 |

| Harmonic distortion vs Output voltage at 1 MHz | Figure 9 | Figure 43 |

| Harmonic distortion vs Gain at 1 MHz | Figure 10 | Figure 44 |

| Harmonic distortion vs Load at 1 MHz | Figure 11 | Figure 45 |

| Harmonic distortion vs VOCM at 1 MHz | Figure 12 | Figure 46 |

| Two-tone, 2nd and 3rd order intermodulation distortion vs Frequency | Figure 13 | Figure 47 |

| Single-ended output voltage swing vs Load resistance | Figure 14 | Figure 48 |

| Single-ended output saturation voltage vs Load current | Figure 15 | Figure 49 |

| Main amplifier differential output impedance vs Frequency | Figure 16 | Figure 50 |

| Frequency response vs CLOAD | Figure 17 | Figure 51 |

| RO vs CLOAD | Figure 18 | Figure 52 |

| Rejection ratio vs Frequency | Figure 19 | Figure 53 |

| Crosstalk vs Frequency | Figure 20 | Figure 54 |

| Turn-on time | Figure 21 | Figure 55 |

| Turn-off time | Figure 22 | Figure 56 |

| Input-referred voltage noise and current noise spectral density | Figure 23 | Figure 57 |

| Main amplifier differential open-loop gain and phase vs Frequency | Figure 24 | Figure 58 |

| Output balance error vs Frequency | Figure 25 | Figure 59 |

| VOCM small signal frequency response | Figure 26 | Figure 60 |

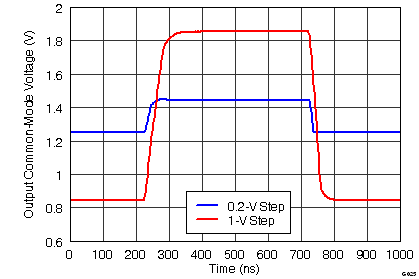

| VOCM large and small signal pulse response | Figure 27 | Figure 61 |

| VOCM input impedance vs frequency | Figure 28 | Figure 62 |

| Count vs input offset current | Figure 29 | Figure 63 |

| Count vs input offset current temperature drift | Figure 30 | Figure 64 |

| Input offset current vs temperature | Figure 31 | Figure 65 |

| Count vs input offset voltage | Figure 32 | Figure 66 |

| Count vs input offset voltage temperature drift | Figure 33 | Figure 67 |

| Input offset voltage vs temperature | Figure 34 | Figure 68 |

7.7.1 Typical Characteristics: VS = 2.7 V

VS+ = 2.7 V, VS– = 0 V, CM = open, VOUT = 2 Vpp, RF = 2 kΩ, RL = 2 kΩ Differential, G = 1V/V, Single-Ended Input, Differential Output, Input and Output Referenced to mid-supply unless otherwise noted.

| VS = 2.7 V | G = 1 V/V | RF = 2 kΩ |

| RL = 2 kΩ | VOUT = 100 mVPP |

| VS = 2.7 V | G = 1 V/V | RF = 2 kΩ |

| RL = 2 kΩ |

| VS = 2.7 V | G = 2 V/V | RF = 2 kΩ |

| RL = 200 Ω |

| VS = 2.7 V | G = 1 V/V | RF = 2 kΩ |

| RL = 100 Ω | VOUT = 4 VPP |

| VS = 2.7 V | G = 1 V/V | RF = 2 kΩ |

| RL = 2 kΩ | f = 1 MHz |

| VS = 2.7 V | G = 1 V/V | RF = 2 kΩ |

| VOUT = 2 VPP | f = 1 MHz |

| VS = 2.7 V | G = 1 V/V | RF = 2 kΩ |

| RL = 2 kΩ | VOUT = 2 VPP | Envelope |

Distortion vs Frequency

| VS = 2.7 V | G = 2 V/V | RF = 2 kΩ |

| VS = 2.7 V | G = 1 V/V | RF = 2 kΩ |

| RL = 2 kΩ | VOUT = 100 mVPP |

| VS = 2.7 V | G = 1 V/V | RF = 2 kΩ |

| RL = 2 kΩ |

| VS = 2.7 V | G = 1 V/V | RF = 2 kΩ |

| RL = 200 Ω | VIN = 1 V |

| VS = 2.7 V | G = 1 V/V | RF = 2 kΩ |

| RL = 2 kΩ | V |

| VS = 2.7 V | TA = 25°C | |

| VS = 2.7 V | Channel 1 | |

| VS = 2.7 V | Both Channels |

| VS = 2.7 V | G = 1 V/V | RF = 2 kΩ |

| RL = 2 kΩ | VOUT = 20 VPP |

| VS = 2.7 V | G = 2 V/V | RF = 2 kΩ |

| RL = 200 Ω |

| VS = 2.7 V | G = 2 V/V | RF = 2 kΩ |

| RL = 2 kΩ |

| VS = 2.7 V | G = 1 V/V | RF = 2 kΩ |

| RL = 2 kΩ | VOUT =2 VPP |

| VS = 2.7 V | RF = 2 kΩ | RL = 2 kΩ |

| VOUT = 2 VPP | f = 1 MHz |

| VS = 2.7 V | G = 1 V/V | RF = 2 kΩ |

| RL = 2 kΩ | VOUT = 2 VPP | f = 1 MHz |

| VS = 2.7 V | G = 2 V/V | RF = 2 kΩ |

| VS = 2.7 V | G = 1 V/V | RF = 2 kΩ |

| VOUT = 100 mVPP |

| VS = 2.7 V | G = 1 V/V | RF = 2 kΩ |

| RL = 2 kΩ |

| VS = 2.7 V | G = 1 V/V | RF = 2 kΩ |

| RL = 2 kΩ | VOUT = 2 VPP |

| VS = 2.7 V | G = 1 V/V | RF = 2 kΩ |

| RL = 200 Ω |

| VS = 2.7 V | G = 1 V/V | RF = 2 kΩ |

| VOUT = 100 mVPP |

| VS = 2.7 V | ||

| VS = 2.7 V | Both Channels | |

| VOUT = 100 mVPP |

| VS = 2.7 V | TA = 25°C |

| VS = 2.7 V | Channel 1 | |

spacer

spacer

spacer

spacer

spacer

spacer

spacer

spacer

spacer

spacer

7.7.2 Typical Characteristics: VS = 5 V

VS+ = 5 V, VS– = 0 V, VOCM = open, VOUT = 2 Vpp, RF = 2 kΩ, RL = 2 kΩ Differential, G = 1V/V, Single-Ended Input, Differential Output, Input and Output Referenced to mid-supply, TA = 25°C unless otherwise noted.

| VS = 5 V | G = 1 V/V | RF = 2 kΩ |

| RL = 2 kΩ | VOUT = 100 mVPP |

| VS = 5 V | G = 1 V/V | RF = 2 kΩ |

| RL = 2 kΩ |

| VS = 5 V | G = 2 V/V | RF = 2 kΩ |

| RL = 200 Ω | VOUT = 100 mVPP |

| VS = 5 V | G = 1 V/V | RF = 2 kΩ |

| RL = 100 kΩ | VOUT = 8 VPP |

| VS = 5 V | G = 1 V/V | RF = 2 kΩ |

| RL = 2 kΩ | f = 1 MHz |

| VS = 5 V | G = 1 V/V | RF = 2 kΩ |

| VOUT 2 VPP | f = 1 MHz |

| VS = 5 V | G = 1 V/V | RF = 2 kΩ |

| RL = 2 kΩ | VOUT = 2 VPP | Envelope |

Distortion vs Frequency

| VS = 5 V | G = 2 V/V | RF = 2 kΩ |

| VS = 5 V | G = 1 V/V | RF = 2 kΩ |

| RL = 2 kΩ | VOUT = 100 mVPP |

| VS = 5 V | G = 1 V/V | RF = 2 kΩ |

| RL = 2 kΩ |

| VS = 5 V | G = 1 V/V | RF = 2 kΩ |

| RL = 200 Ω | VIN = 1 V |

| VS = 5 V | G = 1 V/V | RF = 2 kΩ |

| RL = 2 kΩ |

| VS = 5 V | TA = 25°C |

| VS = 5 V | Channel 1 | |

| VS = 5 V | Both Channels |

| VS = 5 V | G = 1 V/V | RF = 2 kΩ |

| RL = 2 kΩ | VOUT = 2 VPP |

| VS = 5 V | G = 2 V/V | RF = 2 kΩ |

| RL = 200 Ω |

| VS = 5 V | G = 2 V/V | RF = 2 kΩ |

| RL = 200 Ω | VOUT = 100 mVPP |

| VS = 5 V | G = 1 V/V | RF = 2 kΩ |

| RL = 2 kΩ | VOUT = 2VPP |

| VS = 5 V | RF = 2 kΩ | RL = 2 kΩ |

| VOUT = 2 VPP | f = 1 MHz |

| VS = 5 V | G = 1 V/V | RF = 2 kΩ |

| RL = 2 kΩ | VOUT = 2 VPP | f = 1 MHz |

| VS = 5 V | G = 2 V/V | RF = 2 kΩ |

| VS = 5 V | G = 1 V/V | RF = 2 kΩ |

| VOUT = 100 mVPP |

| VS = 5 V | G = 1 V/V | RF = 2 kΩ |

| RL = 2 kΩ |

| VS = 5 V | G = 1 V/V | RF = 2 kΩ |

| RL = 2 kΩ | VOUT = 2 VPP |

| VS = 5 V | G = 1 V/V | RF = 2 kΩ |

| RL = 200 Ω |

| VS = 5 V | G = 1 V/V | RF = 2 kΩ |

| VOUT = 200 mVPP |

| VS = 5 V | ||

| VS = 5 V | Both Channels |

| VS = 5 V | TA = 25°C |

| VS = 5 V | Channel 1 | |