ZHCSP13A september 2021 – june 2023 LMK1D1204P

PRODUCTION DATA

10.2.3 Application Curves

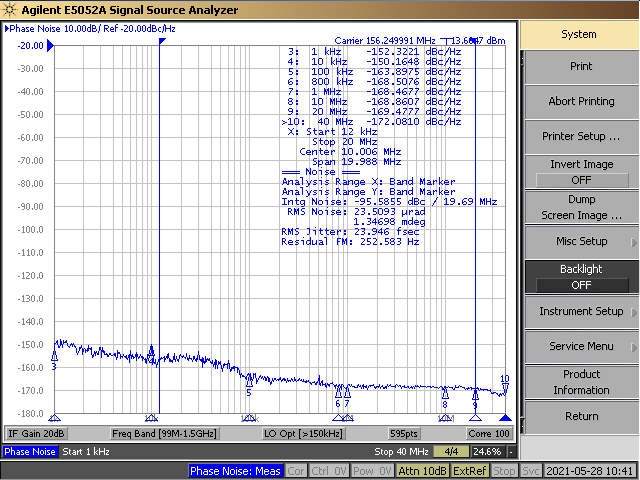

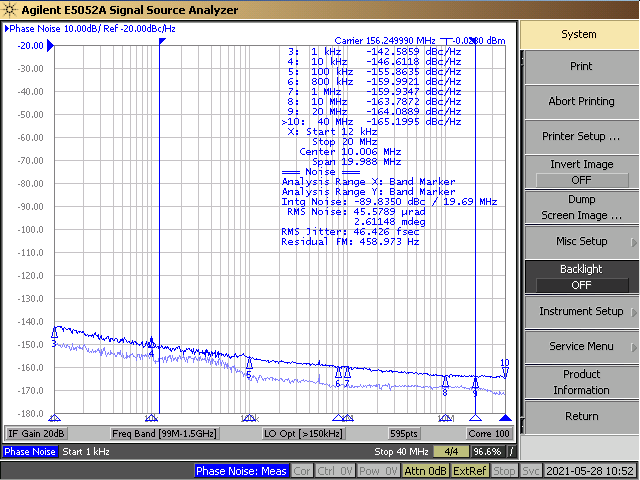

This section shows the low additive noise for the LMK1D1204P. The low noise 156.25-MHz source with 24-fs RMS jitter shown in Figure 10-2 drives the LMK1D1204P, resulting in 46.4-fs RMS when integrated from 12 kHz to 20 MHz (see Figure 10-3). The resultant additive jitter is 39.7-fs RMS for this configuration.

| Note: Reference signal is a low-noise Rhode and Schwarz SMA100B |

Figure 10-3 LMK1D1204P Output Phase Noise, 156.25 MHz, 46.4-fs RMS (12 kHz to 20 MHz)

Figure 10-3 LMK1D1204P Output Phase Noise, 156.25 MHz, 46.4-fs RMS (12 kHz to 20 MHz)