ZHCSDE0A February 2015 – October 2015 CC2650

PRODUCTION DATA.

- 1器件概述

- 2修订历史记录

- 3 Device Comparison

- 4Terminal Configuration and Functions

-

5Specifications

- 5.1 Absolute Maximum Ratings

- 5.2 ESD Ratings

- 5.3 Recommended Operating Conditions

- 5.4 Power Consumption Summary

- 5.5 General Characteristics

- 5.6 1-Mbps GFSK (Bluetooth Low Energy) - RX

- 5.7 1-Mbps GFSK (Bluetooth Low Energy) - TX

- 5.8 IEEE 802.15.4 (Offset Q-PSK DSSS, 250 kbps) - RX

- 5.9 IEEE 802.15.4 (Offset Q-PSK DSSS, 250 kbps) - TX

- 5.10 24-MHz Crystal Oscillator (XOSC_HF)

- 5.11 32.768-kHz Crystal Oscillator (XOSC_LF)

- 5.12 48-MHz RC Oscillator (RCOSC_HF)

- 5.13 32-kHz RC Oscillator (RCOSC_LF)

- 5.14 ADC Characteristics

- 5.15 Temperature Sensor

- 5.16 Battery Monitor

- 5.17 Continuous Time Comparator

- 5.18 Low-Power Clocked Comparator

- 5.19 Programmable Current Source

- 5.20 DC Characteristics

- 5.21 Thermal Characteristics

- 5.22 Timing Requirements

- 5.23 Switching Characteristics

- 5.24 Typical Characteristics

- 6Detailed Description

- 7Application, Implementation, and Layout

- 8器件和文档支持

- 9机械、封装和可订购信息

封装选项

请参考 PDF 数据表获取器件具体的封装图。

机械数据 (封装 | 引脚)

- RSM|32

- RHB|32

- RGZ|48

散热焊盘机械数据 (封装 | 引脚)

订购信息

6 Detailed Description

6.1 Overview

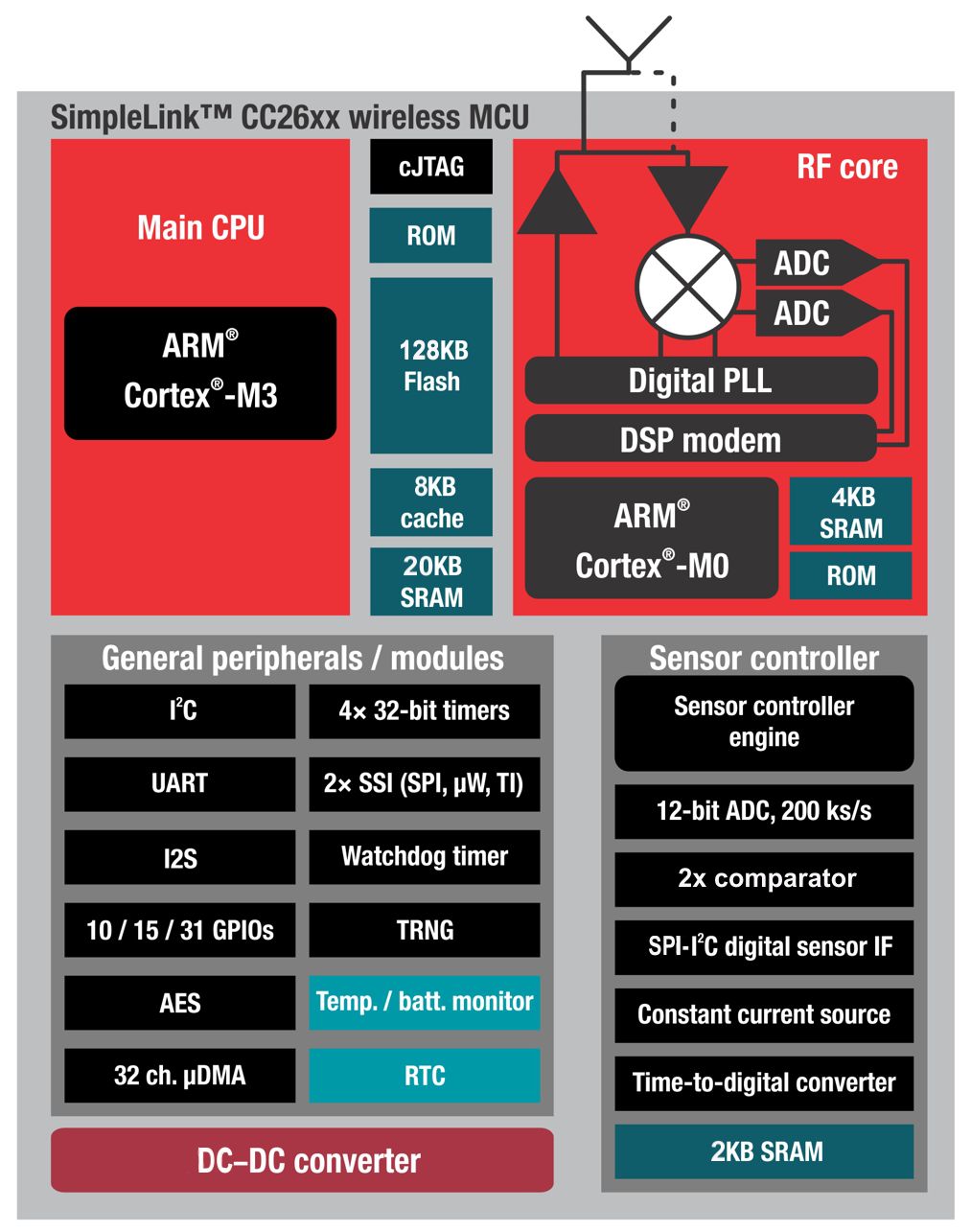

The core modules of the CC26xx product family are shown in the Section 6.2.

6.2 Functional Block Diagram

6.3 Main CPU

The SimpleLink CC2650 Wireless MCU contains an ARM Cortex-M3 (CM3) 32-bit CPU, which runs the application and the higher layers of the protocol stack.

The CM3 processor provides a high-performance, low-cost platform that meets the system requirements of minimal memory implementation, and low-power consumption, while delivering outstanding computational performance and exceptional system response to interrupts.

CM3 features include the following:

- 32-bit ARM Cortex-M3 architecture optimized for small-footprint embedded applications

- Outstanding processing performance combined with fast interrupt handling

- ARM Thumb®-2 mixed 16- and 32-bit instruction set delivers the high performance expected of a 32-bit ARM core in a compact memory size usually associated with 8- and 16-bit devices, typically in the range of a few kilobytes of memory for microcontroller-class applications:

- Single-cycle multiply instruction and hardware divide

- Atomic bit manipulation (bit-banding), delivering maximum memory use and streamlined peripheral control

- Unaligned data access, enabling data to be efficiently packed into memory

- Fast code execution permits slower processor clock or increases sleep mode time

- Harvard architecture characterized by separate buses for instruction and data

- Efficient processor core, system, and memories

- Hardware division and fast digital-signal-processing oriented multiply accumulate

- Saturating arithmetic for signal processing

- Deterministic, high-performance interrupt handling for time-critical applications

- Enhanced system debug with extensive breakpoint and trace capabilities

- Serial wire trace reduces the number of pins required for debugging and tracing

- Migration from the ARM7™ processor family for better performance and power efficiency

- Optimized for single-cycle flash memory use

- Ultralow-power consumption with integrated sleep modes

- 1.25 DMIPS per MHz

6.4 RF Core

The RF Core contains an ARM Cortex-M0 processor that interfaces the analog RF and base-band circuitries, handles data to and from the system side, and assembles the information bits in a given packet structure. The RF core offers a high level, command-based API to the main CPU.

The RF core is capable of autonomously handling the time-critical aspects of the radio protocols (802.15.4 RF4CE and ZigBee, Bluetooth Low Energy) thus offloading the main CPU and leaving more resources for the user application.

The RF core has a dedicated 4-KB SRAM block and runs initially from separate ROM memory. The ARM Cortex-M0 processor is not programmable by customers.

6.5 Sensor Controller

The Sensor Controller contains circuitry that can be selectively enabled in standby mode. The peripherals in this domain may be controlled by the Sensor Controller Engine which is a proprietary power-optimized CPU. This CPU can read and monitor sensors or perform other tasks autonomously, thereby significantly reducing power consumption and offloading the main CM3 CPU.

The Sensor Controller is set up using a PC-based configuration tool, called Sensor Controller Studio, and potential use cases may be (but are not limited to):

- Analog sensors using integrated ADC

- Digital sensors using GPIOs, bit-banged I2C, and SPI

- UART communication for sensor reading or debugging

- Capacitive sensing

- Waveform generation

- Pulse counting

- Keyboard scan

- Quadrature decoder for polling rotation sensors

- Oscillator calibration

NOTE

Texas Instruments provides application examples for some of these use cases, but not for all of them.

The peripherals in the Sensor Controller include the following:

- The low-power clocked comparator can be used to wake the device from any state in which the comparator is active. A configurable internal reference can be used in conjunction with the comparator. The output of the comparator can also be used to trigger an interrupt or the ADC.

- Capacitive sensing functionality is implemented through the use of a constant current source, a time-to-digital converter, and a comparator. The continuous time comparator in this block can also be used as a higher-accuracy alternative to the low-power clocked comparator. The Sensor Controller will take care of baseline tracking, hysteresis, filtering and other related functions.

- The ADC is a 12-bit, 200-ksamples/s ADC with eight inputs and a built-in voltage reference. The ADC can be triggered by many different sources, including timers, I/O pins, software, the analog comparator, and the RTC.

- The Sensor Controller also includes a SPI–I2C digital interface.

- The analog modules can be connected to up to eight different GPIOs.

The peripherals in the Sensor Controller can also be controlled from the main application processor.

Table 6-1 GPIOs Connected to the Sensor Controller(1)

| ANALOG CAPABLE | 7 × 7 RGZ DIO NUMBER |

5 × 5 RHB DIO NUMBER |

4 × 4 RSM DIO NUMBER |

|---|---|---|---|

| Y | 30 | 14 | |

| Y | 29 | 13 | |

| Y | 28 | 12 | |

| Y | 27 | 11 | 9 |

| Y | 26 | 9 | 8 |

| Y | 25 | 10 | 7 |

| Y | 24 | 8 | 6 |

| Y | 23 | 7 | 5 |

| N | 7 | 4 | 2 |

| N | 6 | 3 | 1 |

| N | 5 | 2 | 0 |

| N | 4 | 1 | |

| N | 3 | 0 | |

| N | 2 | ||

| N | 1 | ||

| N | 0 |

6.6 Memory

The flash memory provides nonvolatile storage for code and data. The flash memory is in-system programmable.

The SRAM (static RAM) can be used for both storage of data and execution of code and is split into two 4-KB blocks and two 6-KB blocks. Retention of the RAM contents in standby mode can be enabled or disabled individually for each block to minimize power consumption. In addition, if flash cache is disabled, the 8-KB cache can be used as a general-purpose RAM.

The ROM provides preprogrammed embedded TI RTOS kernel, Driverlib and lower layer protocol stack software (802.15.4 MAC and Bluetooth Low Energy Controller). It also contains a bootloader that can be used to reprogram the device using SPI or UART.

6.7 Debug

The on-chip debug support is done through a dedicated cJTAG (IEEE 1149.7) or JTAG (IEEE 1149.1) interface.

6.8 Power Management

To minimize power consumption, the CC2650 device supports a number of power modes and power management features (see Table 6-2).

Table 6-2 Power Modes

| MODE | SOFTWARE CONFIGURABLE POWER MODES | RESET PIN HELD | |||

|---|---|---|---|---|---|

| ACTIVE | IDLE | STANDBY | SHUTDOWN | ||

| CPU | Active | Off | Off | Off | Off |

| Flash | On | Available | Off | Off | Off |

| SRAM | On | On | On | Off | Off |

| Radio | Available | Available | Off | Off | Off |

| Supply System | On | On | Duty Cycled | Off | Off |

| Current | 1.45 mA + 31 µA/MHz | 550 µA | 1 µA | 0.15 µA | 0.1 µA |

| Wake-up Time to CPU Active(1) | – | 14 µs | 151 µs | 1015 µs | 1015 µs |

| Register Retention | Full | Full | Partial | No | No |

| SRAM Retention | Full | Full | Full | No | No |

| High-Speed Clock | XOSC_HF or RCOSC_HF |

XOSC_HF or RCOSC_HF |

Off | Off | Off |

| Low-Speed Clock | XOSC_LF or RCOSC_LF |

XOSC_LF or RCOSC_LF |

XOSC_LF or RCOSC_LF | Off | Off |

| Peripherals | Available | Available | Off | Off | Off |

| Sensor Controller | Available | Available | Available | Off | Off |

| Wake up on RTC | Available | Available | Available | Off | Off |

| Wake up on Pin Edge | Available | Available | Available | Available | Off |

| Wake up on Reset Pin | Available | Available | Available | Available | Available |

| Brown Out Detector (BOD) | Active | Active | Duty Cycled(2) | Off | N/A |

| Power On Reset (POR) | Active | Active | Active | Active | N/A |

In active mode, the application CM3 CPU is actively executing code. Active mode provides normal operation of the processor and all of the peripherals that are currently enabled. The system clock can be any available clock source (see Table 6-2).

In idle mode, all active peripherals can be clocked, but the Application CPU core and memory are not clocked and no code is executed. Any interrupt event will bring the processor back into active mode.

In standby mode, only the always-on domain (AON) is active. An external wake event, RTC event, or sensor-controller event is required to bring the device back to active mode. MCU peripherals with retention do not need to be reconfigured when waking up again, and the CPU continues execution from where it went into standby mode. All GPIOs are latched in standby mode.

In shutdown mode, the device is turned off entirely, including the AON domain and the Sensor Controller. The I/Os are latched with the value they had before entering shutdown mode. A change of state on any I/O pin defined as a wake from Shutdown pin wakes up the device and functions as a reset trigger. The CPU can differentiate between a reset in this way, a reset-by-reset pin, or a power-on-reset by reading the reset status register. The only state retained in this mode is the latched I/O state and the Flash memory contents.

The Sensor Controller is an autonomous processor that can control the peripherals in the Sensor Controller independently of the main CPU, which means that the main CPU does not have to wake up, for example, to execute an ADC sample or poll a digital sensor over SPI. The main CPU saves both current and wake-up time that would otherwise be wasted. The Sensor Controller Studio enables the user to configure the sensor controller and choose which peripherals are controlled and which conditions wake up the main CPU.

6.9 Clock Systems

The CC2650 supports two external and two internal clock sources.

A 24-MHz crystal is required as the frequency reference for the radio. This signal is doubled internally to create a 48-MHz clock.

The 32-kHz crystal is optional. Bluetooth low energy requires a slow-speed clock with better than

±500 ppm accuracy if the device is to enter any sleep mode while maintaining a connection. The internal

32-kHz RC oscillator can in some use cases be compensated to meet the requirements. The low-speed crystal oscillator is designed for use with a 32-kHz watch-type crystal.

The internal high-speed oscillator (48-MHz) can be used as a clock source for the CPU subsystem.

The internal low-speed oscillator (32.768-kHz) can be used as a reference if the low-power crystal oscillator is not used.

The 32-kHz clock source can be used as external clocking reference through GPIO.

6.10 General Peripherals and Modules

The I/O controller controls the digital I/O pins and contains multiplexer circuitry to allow a set of peripherals to be assigned to I/O pins in a flexible manner. All digital I/Os are interrupt and wake-up capable, have a programmable pullup and pulldown function and can generate an interrupt on a negative or positive edge (configurable). When configured as an output, pins can function as either push-pull or open-drain. Five GPIOs have high drive capabilities (marked in bold in Section 4).

The SSIs are synchronous serial interfaces that are compatible with SPI, MICROWIRE, and Texas Instruments synchronous serial interfaces. The SSIs support both SPI master and slave up to 4 MHz.

The UART implements a universal asynchronous receiver/transmitter function. It supports flexible baud-rate generation up to a maximum of 3 Mbps and is compatible with the Bluetooth HCI specifications.

Timer 0 is a general-purpose timer module (GPTM), which provides two 16-bit timers. The GPTM can be configured to operate as a single 32-bit timer, dual 16-bit timers or as a PWM module.

Timer 1, Timer 2, and Timer 3 are also GPTMs. Each of these timers is functionally equivalent to Timer 0.

In addition to these four timers, the RF core has its own timer to handle timing for RF protocols; the RF timer can be synchronized to the RTC.

The I2C interface is used to communicate with devices compatible with the I2C standard. The I2C interface is capable of 100-kHz and 400-kHz operation, and can serve as both I2C master and I2C slave.

The TRNG module provides a true, nondeterministic noise source for the purpose of generating keys, initialization vectors (IVs), and other random number requirements. The TRNG is built on 24 ring oscillators that create unpredictable output to feed a complex nonlinear combinatorial circuit.

The watchdog timer is used to regain control if the system fails due to a software error after an external device fails to respond as expected. The watchdog timer can generate an interrupt or a reset when a predefined time-out value is reached.

The device includes a direct memory access (µDMA) controller. The µDMA controller provides a way to offload data transfer tasks from the CM3 CPU, allowing for more efficient use of the processor and the available bus bandwidth. The µDMA controller can perform transfer between memory and peripherals. The µDMA controller has dedicated channels for each supported on-chip module and can be programmed to automatically perform transfers between peripherals and memory as the peripheral is ready to transfer more data. Some features of the µDMA controller include the following (this is not an exhaustive list):

- Highly flexible and configurable channel operation of up to 32 channels

- Transfer modes:

- Memory-to-memory

- Memory-to-peripheral

- Peripheral-to-memory

- Peripheral-to-peripheral

- Data sizes of 8, 16, and 32 bits

The AON domain contains circuitry that is always enabled, except for in Shutdown (where the digital supply is off). This circuitry includes the following:

- The RTC can be used to wake the device from any state where it is active. The RTC contains three compare and one capture registers. With software support, the RTC can be used for clock and calendar operation. The RTC is clocked from the 32-kHz RC oscillator or crystal. The RTC can also be compensated to tick at the correct frequency even when the internal 32-kHz RC oscillator is used instead of a crystal.

- The battery monitor and temperature sensor are accessible by software and give a battery status indication as well as a coarse temperature measure.

6.11 System Architecture

Depending on the product configuration, CC26xx can function either as a Wireless Network Processor (WNP—an IC running the wireless protocol stack, with the application running on a separate MCU), or as a System-on-Chip (SoC), with the application and protocol stack running on the ARM CM3 core inside the device.

In the first case, the external host MCU communicates with the device using SPI or UART. In the second case, the application must be written according to the application framework supplied with the wireless protocol stack.