ZHCSBF4B July 2013 – September 2015 ADS42JB46

PRODUCTION DATA.

- 1 特性

- 2 应用

- 3 说明

- 4 修订历史记录

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

-

7 Specifications

- 7.1 Absolute Maximum Ratings

- 7.2 ESD Ratings

- 7.3 Recommended Operating Conditions

- 7.4 Thermal Information

- 7.5 Electrical Characteristics: ADS42JB46

- 7.6 Electrical Characteristics: General

- 7.7 Timing Characteristics

- 7.8 Digital Characteristics

- 7.9 Reset Timing

- 7.10 Serial Interface Timing

- 7.11 Typical Characteristics: ADS42JB46

- 7.12 Typical Characteristics: Contour

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3 Feature Description

- 8.4 Device Functional Modes

- 8.5 Programming

- 8.6

Register Maps

- 8.6.1 Summary of Serial Interface Registers

- 8.6.2

Description of Serial Interface Registers

- 8.6.2.1 Register Address 06

- 8.6.2.2 Register Address 07

- 8.6.2.3 Register Address 08

- 8.6.2.4 Register Address 0B

- 8.6.2.5 Register Address 0C

- 8.6.2.6 Register Address 0D

- 8.6.2.7 Register Address 0E

- 8.6.2.8 Register Address 0F

- 8.6.2.9 Register Address 10

- 8.6.2.10 Register Address 11

- 8.6.2.11 Register Address 12

- 8.6.2.12 Register Address 13

- 8.6.2.13 Register Address 1F

- 8.6.2.14 Register Address 26

- 8.6.2.15 Register Address 27

- 8.6.2.16 Register Address 2B

- 8.6.2.17 Register Address 2C

- 8.6.2.18 Register Address 2D

- 8.6.2.19 Register Address 30

- 8.6.2.20 Register Address 36

- 8.6.2.21 Register Address 37

- 8.6.2.22 Register Address 38

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12器件和文档支持

- 13机械、封装和可订购信息

9 Application and Implementation

NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI’s customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

9.1 Application Information

A device clock and sysref signal must be provided to the ADC and it is recommended that these are source synchronous (generated from a common source with match trace lengths) if synchronizing multiple ADCs. An example of a device that can be used to generate source synchronous device clock and sysref is the LMK04828. The device clock frequency must be the same frequency as the desired sampling rate. The sysref period is required to be an integer multiple of the period of the multi-frame clock. Consequently, the frequency of sysref must be restricted to (Device Clock Frequency) / (2×n×K),n = 1,2,3… K is set by the value in spi register 0x2D and it ranges from 1 to 32. A large enough K is recommended (greater than 16) to absorb the lane skews and avoid data transmission errors across the JESD204B interface. The sync~ signal is used by the FPGA or ASIC to acknowledge the correct reception of comma characters from the ADC during the JESD204B link initialization process. During normal operation this signal should be logic 1 if there are no errors in the data transmission from the ADC to the FPGA or ASIC.

9.2 Typical Application

In a typical application, such as a dual channel digitizer, the ADS42JB46 is connected to an FPGA or ASIC as shown in Figure 75.

Figure 75. ADS42JBxx in a Dual-Channel Digitizer

Figure 75. ADS42JBxx in a Dual-Channel Digitizer

9.2.1 Design Requirements

For this design example, use the parameters listed in Table 15 as the input parameters.

Table 15. Design Parameters

| PARAMETER | EXAMPLE VALUE |

|---|---|

| Fsampling | 160 MSPS |

| IF | 10 MHz,170 MHz |

| SNR | >72 dBc |

| SFDR | >80 dBc |

| HD2 | >90 dBc |

9.2.2 Detailed Design Procedure

9.2.2.1 Analog Input

The analog input pins have analog buffers (running from the AVDD3V supply) that internally drive the differential sampling circuit. As a result of the analog buffer, the input pins present high input impedance to the external driving source (10-kΩ dc resistance and 4-pF input capacitance). The buffer helps isolate the external driving source from the switching currents of the sampling circuit. This buffering makes driving the buffered inputs easier than when compared to an ADC without the buffer.

The input common-mode is set internally using a 5-kΩ resistor from each input pin to VCM so the input signal can be ac-coupled to the pins. Each input pin (INP, INM) must swing symmetrically between (VCM + 0.5 V) and (VCM – 0.5 V), resulting in a 2-V PP differential input swing. When programmed for a 2.5-V PP full-scale, each input pin must swing symmetrically between (VCM + 0.625 V) and (VCM – 0.625 V).

The input sampling circuit has a high 3-dB bandwidth that extends up to 900 MHz (measured with a 50-Ω source driving a 50-Ω termination between INP and INM). The dynamic offset of the first-stage sub-ADC limits the maximum analog input frequency to approximately 250 MHz (with a 2.5-VPP full-scale amplitude) and to approximately 400 MHz (with a 2-VPP full-scale amplitude). This 3-dB bandwidth is different than the analog bandwidth of 900 MHz, which is only an indicator of signal amplitude versus frequency.

9.2.2.1.1 Drive Circuit Requirements

For optimum performance, the analog inputs must be driven differentially. This technique improves the common-mode noise immunity and even-order harmonic rejection. A small resistor (5 Ω to 10 Ω) in series with each input pin is recommended to damp out ringing caused by package parasitics.

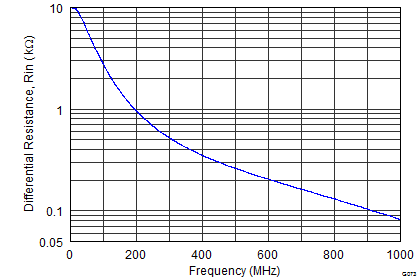

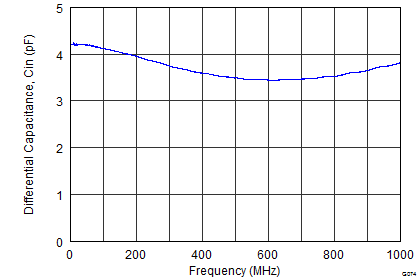

Figure 76, Figure 77, and Figure 78 show the differential impedance (ZIN = RIN || CIN) at the ADC input pins. The presence of the analog input buffer results in an almost constant input capacitance up to 1 GHz.

Figure 77. ADC Analog Input Resistance (RIN) Across Frequency

Figure 77. ADC Analog Input Resistance (RIN) Across Frequency

Figure 78. ADC Analog Input Capacitance (CIN) Across Frequency

Figure 78. ADC Analog Input Capacitance (CIN) Across Frequency

9.2.2.1.2 Driving Circuit

An example driving circuit configuration is shown in Figure 79. To optimize even-harmonic performance at high input frequencies (greater than the first Nyquist), the use of back-to-back transformers is recommended, as shown in Figure 79. Note that the drive circuit is terminated by 50 Ω near the ADC side. The ac-coupling capacitors allow the analog inputs to self-bias around the required common-mode voltage. An additional R-C-R (39 Ω – 6.8 pF – 39 Ω) circuit placed near the device pins helps further improve HD3.

Figure 79. Drive Circuit for Input Frequencies up to 250 MHz

Figure 79. Drive Circuit for Input Frequencies up to 250 MHz

The mismatch in the transformer parasitic capacitance (between the windings) results in degraded even-order harmonic performance. Connecting two identical RF transformers back-to-back helps minimize this mismatch and good performance is obtained for high-frequency input signals. An additional termination resistor pair may be required between the two transformers, as shown in Figure 79. The center point of this termination is connected to ground to improve the balance between the P (positive) and M (negative) sides. The values of the terminations between the transformers and on the secondary side must be chosen to obtain an effective 50 Ω (for a 50-Ω source impedance). For high input frequencies (> 250 MHz), the R-C-R circuit can be removed, as indicated in Figure 80.

Figure 80. Drive Circuit for Input Frequencies > 250 MHz

Figure 80. Drive Circuit for Input Frequencies > 250 MHz

9.2.2.2 Clock Input

The device clock inputs can be driven differentially (sine, LVPECL, or LVDS) or single-ended (LVCMOS), with little or no difference in performance between them. The common-mode voltage of the clock inputs is set to 1.4 V using internal 5-kΩ resistors. The self-bias clock inputs of the device can be driven by the transformer-coupled, sine-wave clock source or by the ac-coupled, LVPECL and LVDS clock sources, as shown in Figure 81, Figure 82, and Figure 83. Figure 84 details the internal clock buffer.

NOTE:

RT = termination resistor, if necessary. Figure 82. LVDS Clock Driving Circuit

Figure 82. LVDS Clock Driving Circuit

Figure 83. LVPECL Clock Driving Circuit

Figure 83. LVPECL Clock Driving Circuit

NOTE:

CEQ is 1 pF to 3 pF and is the equivalent input capacitance of the clock buffer.A single-ended CMOS clock can be ac-coupled to the CLKP input, with CLKM connected to ground with a 0.1-μF capacitor, as shown in Figure 85. However, for best performance, the clock inputs must be driven differentially, thereby reducing susceptibility to common-mode noise. For high input frequency sampling, TI recommends using a clock source with very low jitter. Band-pass filtering of the clock source can help reduce the effects of jitter. There is no change in performance with a non-50% duty cycle clock input.

Figure 85. Single-Ended Clock Driving Circuit

Figure 85. Single-Ended Clock Driving Circuit

9.2.2.3 SNR and Clock Jitter

The signal-to-noise ratio (SNR) of the ADC is limited by three different factors, as shown in Equation 3. Quantization noise is typically not noticeable in pipeline converters and is 96 dBFS for a 16-bit ADC. Thermal noise limits SNR at low input frequencies and clock jitter sets SNR for higher input frequencies.

SNR limitation is a result of sample clock jitter and can be calculated by Equation 4:

The total clock jitter (TJitter) has three components: the internal aperture jitter (85 fS for the device) is set by the noise of the clock input buffer, the external clock jitter, and the jitter from the analog input signal. TJitter can be calculated by Equation 5:

External clock jitter can be minimized by using high-quality clock sources and jitter cleaners as well as band-pass filters at the clock input while a faster clock slew rate improves ADC aperture jitter. The device has a 74.1-dBFS thermal noise and an 85-fS internal aperture jitter. The SNR value depends on the amount of external jitter for different input frequencies, as shown in Figure 86.

Figure 86. SNR versus Input Frequency and External Clock Jitter

Figure 86. SNR versus Input Frequency and External Clock Jitter

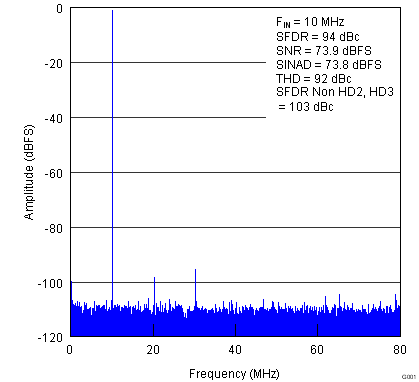

9.2.3 Application Curves

Figure 87. FFT for 10-MHz Input Signal

Figure 87. FFT for 10-MHz Input Signal

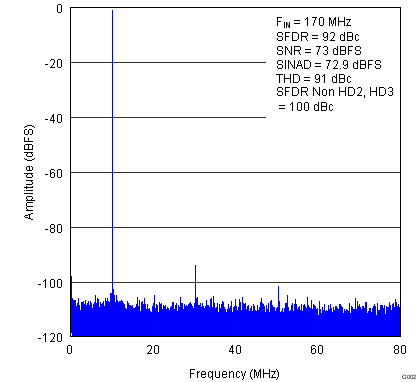

Figure 88. FFT for 170-MHz Input Signal

Figure 88. FFT for 170-MHz Input Signal