ZHCU481E october 2022 – july 2023

2.3.6.3 逻辑视图

以下几个图展示了与节 2.3.6.2相同的信息,不过是通过逻辑框图显示的。特别是:

- 图 2-14 和图 2-15 展示了使用逻辑门的 CLB 块的内容。

- 图 2-16 使用该逻辑来显示主状态机如何控制其他块。

- 图 2-17 跟踪几个从其输入开始并经过一些相关逻辑的简单 CLB 输出信号。

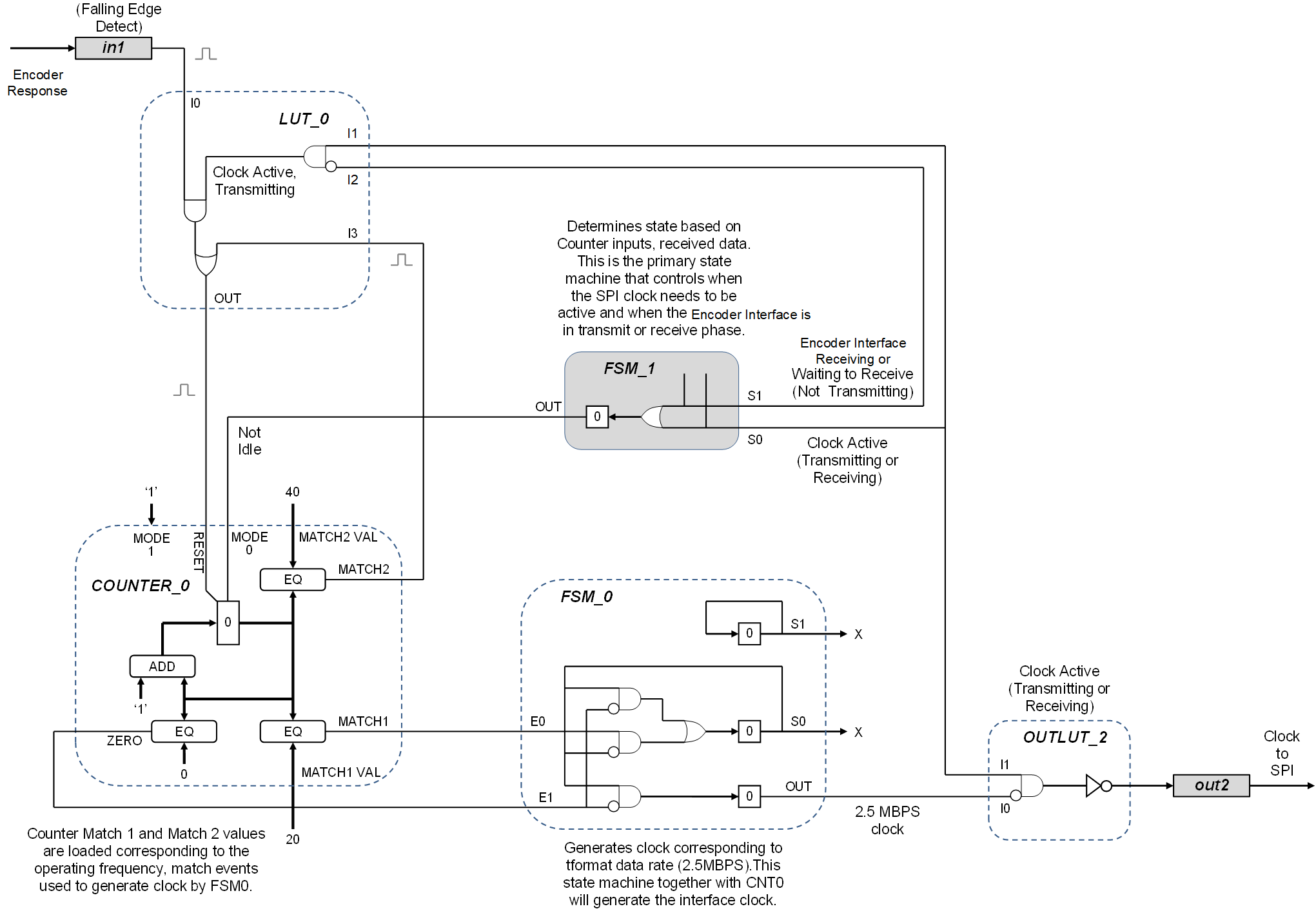

- 图 2-18 跟踪时钟到 SPI 输出,从 Input1 开始,经过 LUT_0、FSM_0、Counter_0,一直到 Ouput_LUT_0(受 FSM_1 的 3 个输出控制)。

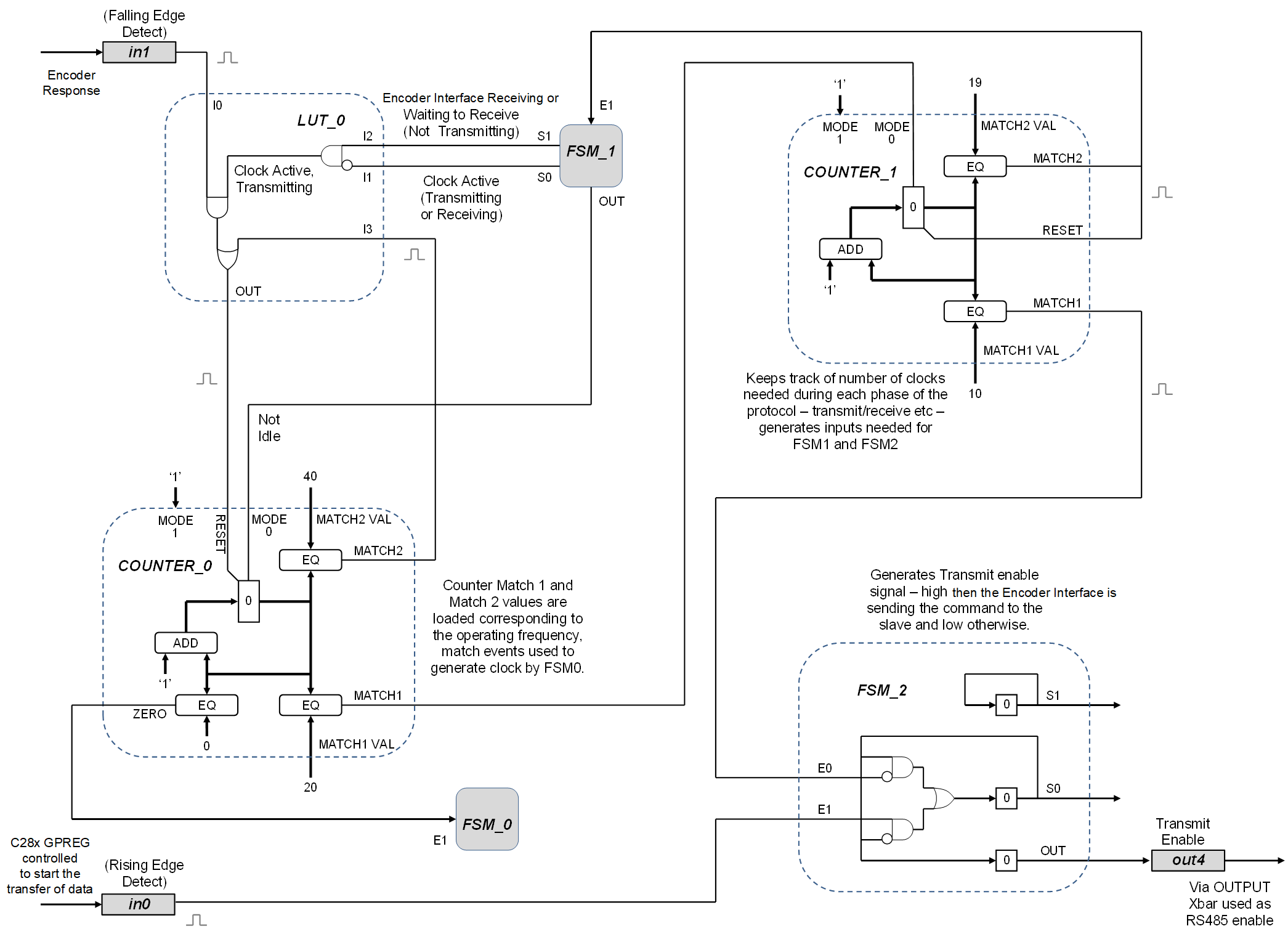

- 图 2-19 跟踪发送使能输出,从 Input0 和 Input1 开始,经过 LUT_0、Counter_0、Counter1 和 FSM_2(受 FSM_1 的 3 个输出控制)。

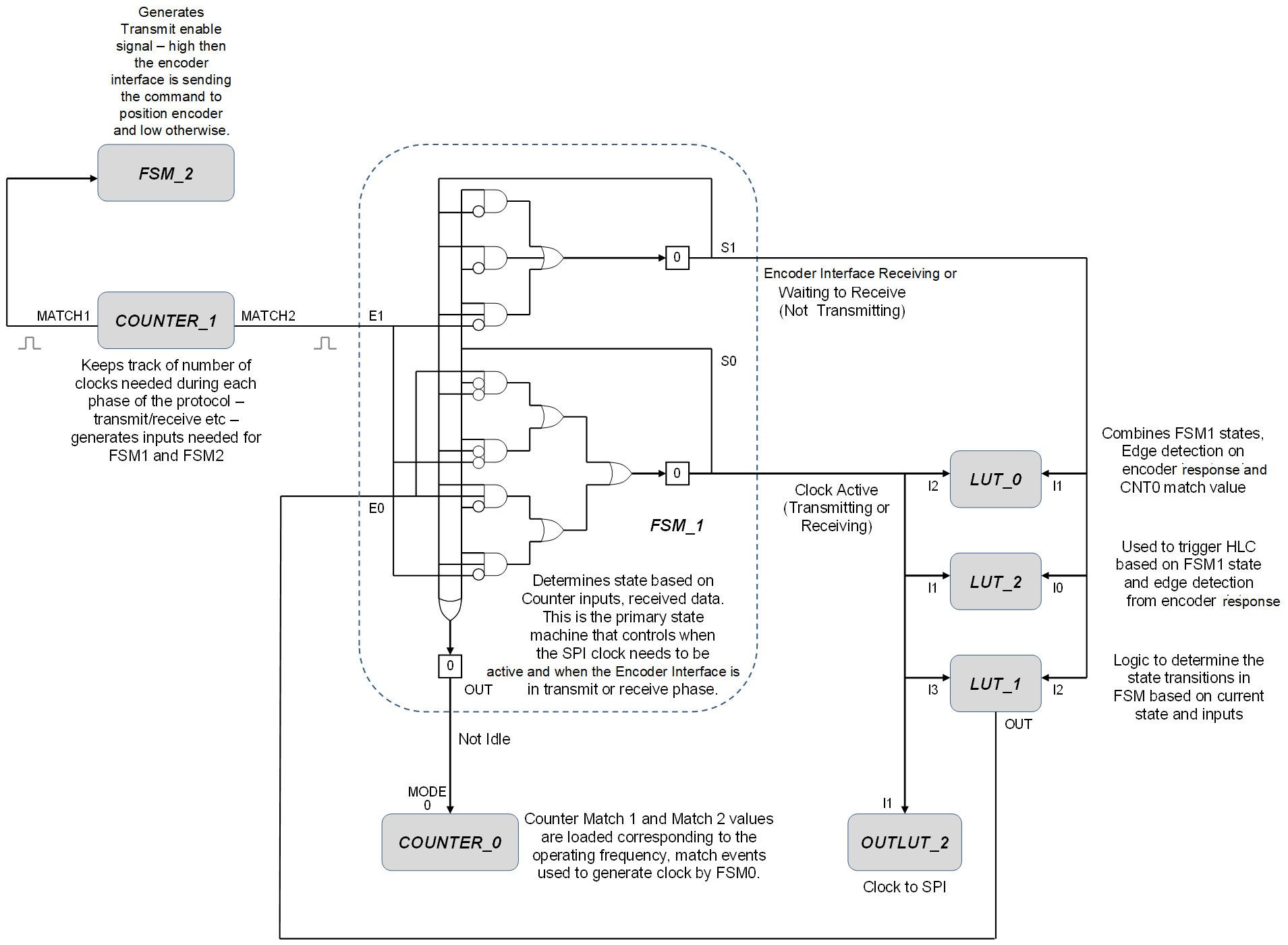

图 2-14 LUT、OUTLUT 和计数器

图 2-14 LUT、OUTLUT 和计数器 图 2-15 有限状态机

图 2-15 有限状态机 图 2-16 主状态机

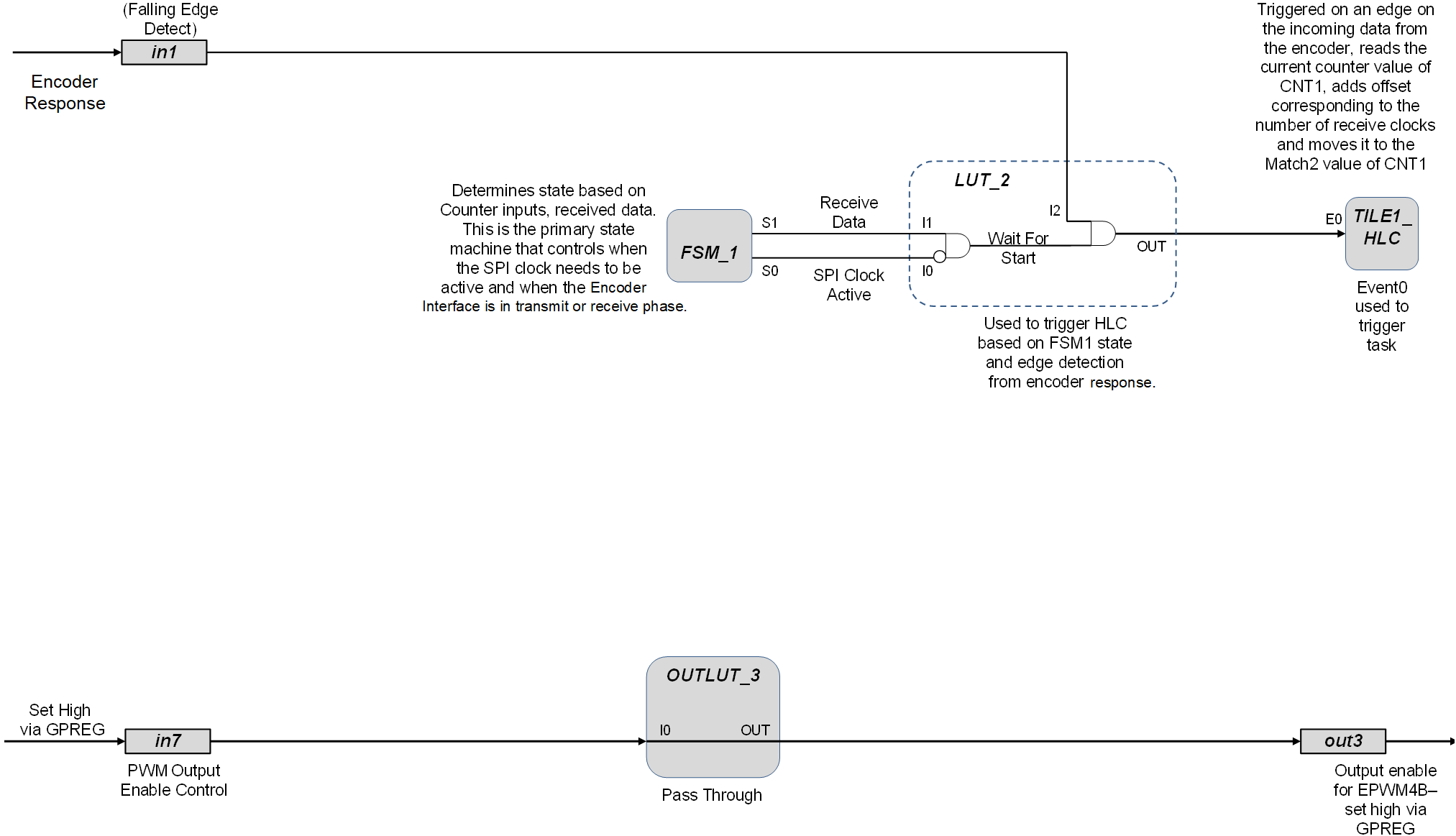

图 2-16 主状态机 图 2-17 CLB 输出 – HLC Event0 和 EPWM 输出使能

图 2-17 CLB 输出 – HLC Event0 和 EPWM 输出使能注: 只有 F2837xD 设计会覆盖 ePWM 输出。

图 2-18 CLB 输出 – 时钟到 SPI

图 2-18 CLB 输出 – 时钟到 SPI 图 2-19 CLB 输出 – RS485 使能

图 2-19 CLB 输出 – RS485 使能