ZHCACT4 june 2023 AM2431 , AM2432 , AM2434 , AM2631 , AM2631-Q1 , AM2632 , AM2632-Q1 , AM2634 , AM2634-Q1 , AM263P4 , AM3351 , AM3352 , AM3354 , AM3356 , AM3357 , AM3358 , AM3358-EP , AM3359 , AM4372 , AM4376 , AM4377 , AM4378 , AM4379 , AM5706 , AM5708 , AM5716 , AM5718 , AM5718-HIREL , AM5726 , AM5728 , AM5729 , AM5746 , AM5748 , AM5749 , AM6411 , AM6412 , AM6421 , AM6422 , AM6441 , AM6442 , AM6526 , AM6528 , AM6546 , AM6548

2.5 LVDS 和 M-LVDS 接口

低电压差分信令 (LVDS) 器件通常符合美国国家标准学会 (ANSI) 标准 TIA/EIA-644。多点低电压差分信令 (M-LVDS) 符合 ANSI TIA/EIA-899。表 2-1 重点介绍了 LVDS 和 M-LVDS 之间的驱动器和接收器的一些重要规格。

| 参数 | TIA/EIA-644-A (LVDS REV A) | TIA/EIA-899 (M-LVDS) | 单位 |

|---|---|---|---|

| 驱动器特性 | |||

| 失调电压:Vos(最大值) | 1375 | 2100 | mV |

| 失调电压:Vos(最小值) | 1125 | 300 | mV |

|

差分输出电压:Vod(最大值) |

454 (100Ω) | 650 (50Ω) | mV |

| 差分输出电压:Vod(最小值) | 247 (100Ω) | 480 (50Ω) | mV |

| 失调电压变化:Vospp | 150 | 150 | mV |

| 短路电流:Ios | 12/24 | 43 | mA |

| 差分电压变化:ΔVod | 50 | 50 | mV |

| 失调电压变化:ΔVos | 50 | 50 | mV |

| 转换时间:tr/tf(最小值) | 260 | 1000 | ps |

| 接收器特性 | |||

| 接地电位差:Vgpd | ±1 | ±1 | V |

| 输入漏电流:输入电流 | 20 | 20 | μA |

| 差分输入漏电流:Iid | 6 | 4 | μA |

| 输入电压范围:Vin | 0 至 2.4 | -1.4 至 3.8 | V |

| 输入阈值:Vith | 100 | 50 | mV |

驱动器内通信设计需要高速、低功耗和电磁兼容性。因此,LVDS 器件为从点对点到多点数据传输的驱动器内通信设计提供了广泛的解决方案。数据传输速率可达 1500Mbps,电缆长度为 100 米,功耗仅为 1.2mW。差分信号还有助于提高抗噪声能力。德州仪器 (TI) 用于 LVDS 的 DS90x 系列和用于 M-LVDS 的 SN65MLVDSx 系列为设计人员提供了各种单通道和多通道器件。此外,TI 的 ISO7821LLx 系列在驱动器内设计中需要时,特别是在冷热侧控制应用中,通过 LVDS 接口提供了增强的隔离。图 2-10 显示了具有 LVDS 接口和 PRU 的驱动器内通信方框图。

图 2-10 具有 LVDS 接口和 PRU 的驱动器内通信方框图

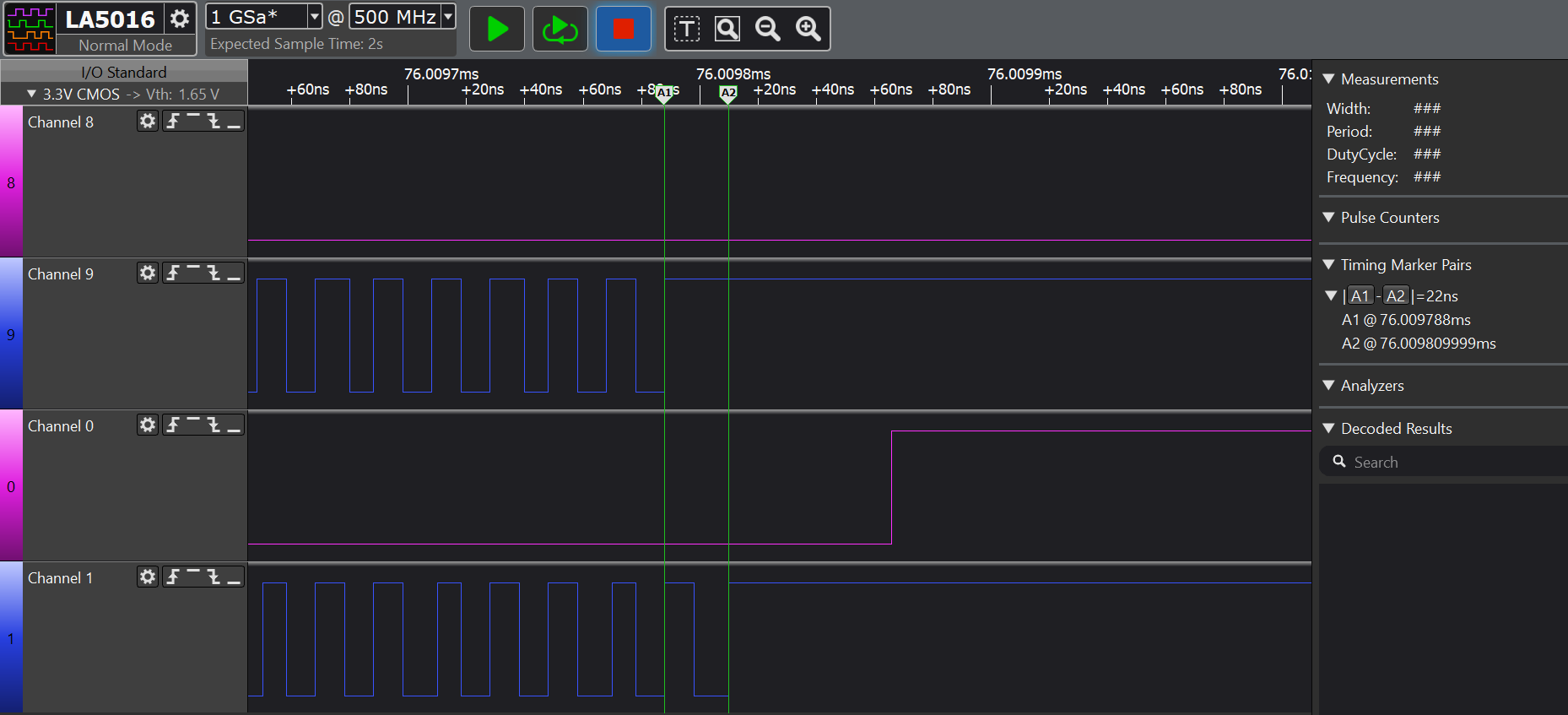

图 2-10 具有 LVDS 接口和 PRU 的驱动器内通信方框图为了验证 LVDS 收发器和隔离器的延迟,PRU_GPO 使用 DS90LV049+ISO7821LL 为 LVDS 接口发送 100MHz 时钟信号,使用 SM65MLVDS203+ISO7840 为 M-LVDS 接口发送 100MHz 时钟信号。图 2-11 和图 2-12 显示 LVDS 接口的延迟为 18ns,M-LVDS 接口的延迟为 22ns。

图 2-11 DS90LV049 接口和 ISO7821LL LVDS 接口的 18ns 延迟

图 2-11 DS90LV049 接口和 ISO7821LL LVDS 接口的 18ns 延迟 图 2-12 SN65MLLVDS203 接口和 ISO7840 M-LVDS 接口的 22ns 延迟

图 2-12 SN65MLLVDS203 接口和 ISO7840 M-LVDS 接口的 22ns 延迟