ZHCABX7A May 2020 – November 2022 TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28033 , TMS320F28033-Q1 , TMS320F28035 , TMS320F28035-EP , TMS320F28035-Q1 , TMS320F28053 , TMS320F28055 , TMS320F2806-Q1 , TMS320F28065 , TMS320F28069 , TMS320F28069-Q1 , TMS320F28069F , TMS320F28069F-Q1 , TMS320F28069M , TMS320F28069M-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384D-Q1 , TMS320F28384S , TMS320F28384S-Q1 , TMS320F28386D , TMS320F28386D-Q1 , TMS320F28386S , TMS320F28386S-Q1 , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

5 将快速控制环路卸载到 CLA

各种实时控制应用涉及在单个器件上实现多个控制环路。然而,从处理器带宽的角度来讲,将多个控制系统集成在单个控制器上,而同时保持低系统成本,仍然具有挑战性。CLA 是与 C28x 主内核完全并行的处理器,可为 C28x 系列带来并发的控制环路执行。CLA 有其自身的程序和数据总线,并且独立于 MCU 上的主内核之外执行。如Topic Link Label2和Topic Link Label3所述,CLA 的独特之处包括提供最小延迟并轻松访问主要控制外设,使 CLA 能够完全从 C28x 卸载快速控制算法任务。将控制任务卸载到 CLA 还有其他好处,例如执行中的抖动降低和控制环路的确定性操作。之所以可以实现这一点,是因为 CLA 以任务为导向,而非由中断服务驱动的状态机,并且 CLA 上的任务不能被中断,从而保证了控制环路的确定性。在管线型 CPU 中,如果 CPU 在 ISR 被接收时正在执行分支类型语句,ISR 可被延迟“n”个数量周期。但是,这对于 CLA CPU 来说不是问题,因为它本质上是任务驱动的,会在空闲状态下等待,直到周期性任务触发才开始执行。因此,将快速控制任务卸载到 CLA 并在 C28x 上运行其余任务有助于提高总体系统性能,同时减少执行中的抖动。

“cla_ex6_cpu_offloading”示例说明了当涉及多个需要多个 CPU (C28x) 带宽的控制任务和后台任务时,如何以较好的方式将控制环路从 C28x 卸载到 CLA。图 5-1 显示在该示例中仿真了两个控制环路。较快的环路(环路 1)以 200KHz 的频率运行,而较慢的环路(环路 2)以 20KHz 的频率运行。这两个环路都使用 PI 控制器来控制单个 PWM 输出的占空比,但贡献权重不同:较快的环路占 80%,较慢的环路占 20%。两个环路的输入由 ADCA 和 ADCB 进行采样,每个环路都有多个 SOC 可用于滤除输入中的任何噪声。主环路中还有一个连续运行的后台任务,可根据用户配置的开关“system_OFF”禁用或启用整个系统,包括 PWM 输出和控制环路。请注意,CCS 调试器时钟不能用于对 CLA 例程进行分析,因此该示例中采用了基于 GPIO 的分析技术来分析这两个任务的表现。已使用 GPIO2 和 GPIO 3 来实现此目的。

图 5-2 显示了在没有使用 CLA 的情况下,两个控制任务全部都在 C28x 上运行时的流程图。在这种情况下,总 CPU (C28x) 利用率超过可调度的利用率限制 (UB),因此在这种情况下系统是可调度的。通过观察图 5-3 中显示的分析波形也可以进一步证实这一点。请注意,在 GPIO3 上没有观察到切换,这清楚地表明优先级较低的环路 2 任务没有机会完成,后台任务也不会完成。

图 5-1 双控制环路示例展示

图 5-1 双控制环路示例展示 图 5-2 两个任务都在 C28x 上运行的流程图

图 5-2 两个任务都在 C28x 上运行的流程图 图 5-3 C28x 上运行的两个任务的分析波形

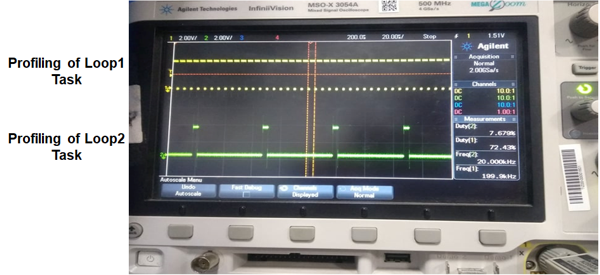

图 5-3 C28x 上运行的两个任务的分析波形由于系统不可通过 C28x 进行调度,因此可以将其中一项控制任务卸载到 CLA 以满足系统要求。由于 CLA 提供非常低的中断延迟,因此最好将快速控制任务卸载到 CLA,这样也会释放 C28x 上的最大带宽,从而可将带宽用于执行后台任务和其他系统任务。图 5-4 所示为当较高频率环路 1 任务卸载到 CLA 时这两个任务的流程图。通过将 CLA 用于并发环路执行,用于控制任务的 C28x 利用率下降到大约 7.7%,从而可以正确执行其他后台任务。将任务卸载到 CLA 可使系统在这种情况下完全可调度,从图 5-5 中显示的分析波形也可以明显看出这一点。该示例允许用户通过将工程构建选项中的预定义符号“run_loop1_cla”更新为 1,快速方便地将环路 1 任务从 C28x 卸载到 CLA。

图 5-4 将环路 1 任务卸载到 CLA 的流程图

图 5-4 将环路 1 任务卸载到 CLA 的流程图 图 5-5 将环路 1 任务卸载到 CLA 的分析波形

图 5-5 将环路 1 任务卸载到 CLA 的分析波形