ZHCABL1A December 2020 – January 2022 TAS2563

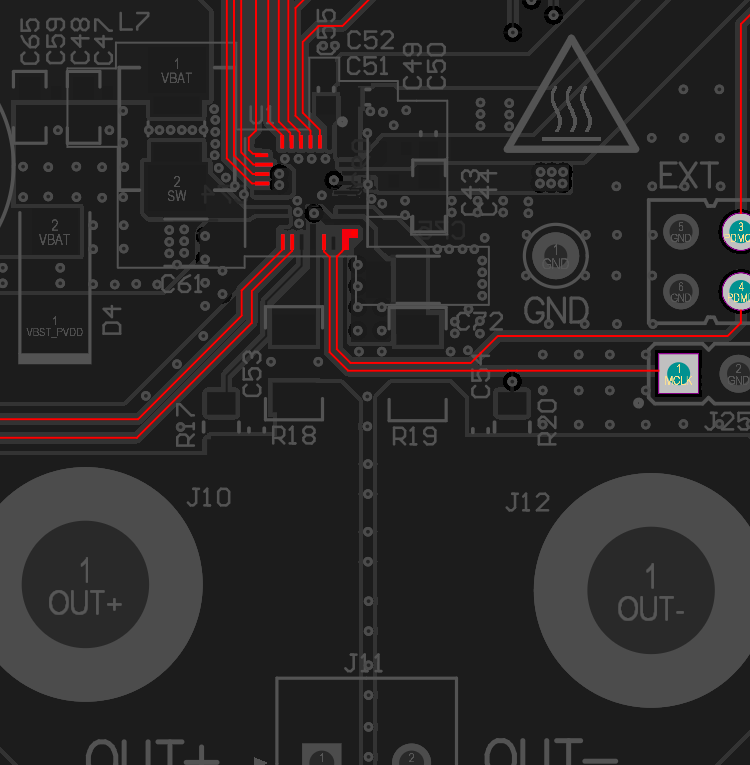

1.10 数字部分

TAS2563 器件涉及数字和模拟活动。布线不同信号时必须小心谨慎,否则可能导致噪声问题,尤其是从数字线路到模拟部分的布线。

在超快速模式中,I2C 线路的数字线路频率可达 1MHz,I2S 线路的数字线路频率可达 50MHz。这类高频成分会影响模拟信号的性能。在测量方面,数字噪声电平可能影响示波器捕获或 THD+N 测量结果。

图 1-12 数字连接

图 1-12 数字连接ZHCABL1A December 2020 – January 2022 TAS2563

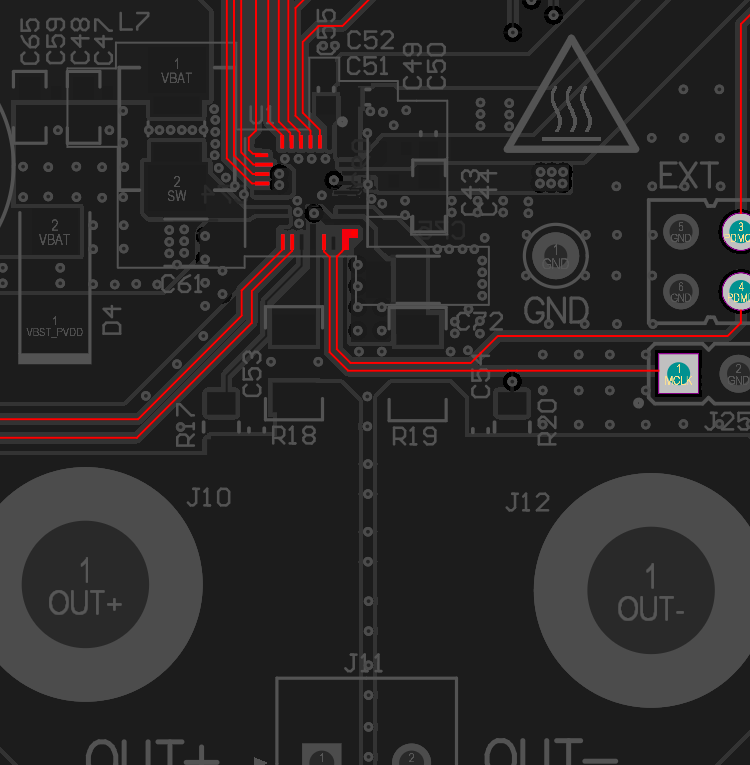

TAS2563 器件涉及数字和模拟活动。布线不同信号时必须小心谨慎,否则可能导致噪声问题,尤其是从数字线路到模拟部分的布线。

在超快速模式中,I2C 线路的数字线路频率可达 1MHz,I2S 线路的数字线路频率可达 50MHz。这类高频成分会影响模拟信号的性能。在测量方面,数字噪声电平可能影响示波器捕获或 THD+N 测量结果。

图 1-12 数字连接

图 1-12 数字连接