ZHCABJ6B April 2022 – January 2024 PCM3120-Q1 , PCM5120-Q1 , PCM6120-Q1 , TLV320ADC3120 , TLV320ADC3140 , TLV320ADC5120 , TLV320ADC5140 , TLV320ADC6120 , TLV320ADC6140

2 TLV320ADCx140/TLV320ADCx120/PCMx120-Q1/PCMx140-Q1 中固有的抗混叠功能

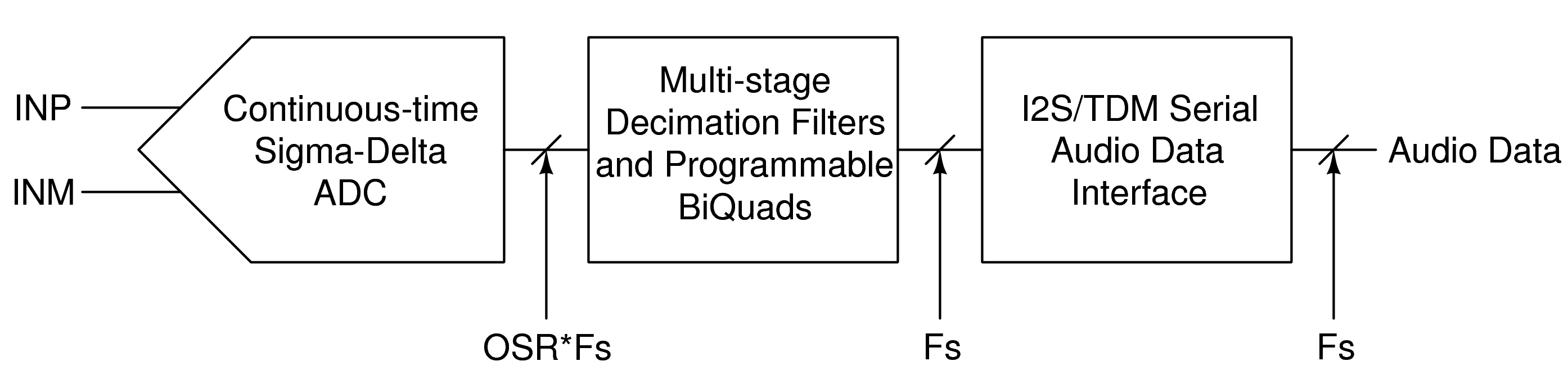

TLV320ADCx140/TLV320ADCx120/PCMx120-Q1/PCMx140-Q1 器件使用 Δ-Σ 模数转换器来对输入信号进行数字化处理。该 ADC 结合使用过采样和噪声整形功能来实现高性能。图 2-1 展示了音频信号链的简化方框图。

图 2-1 音频信号链方框图

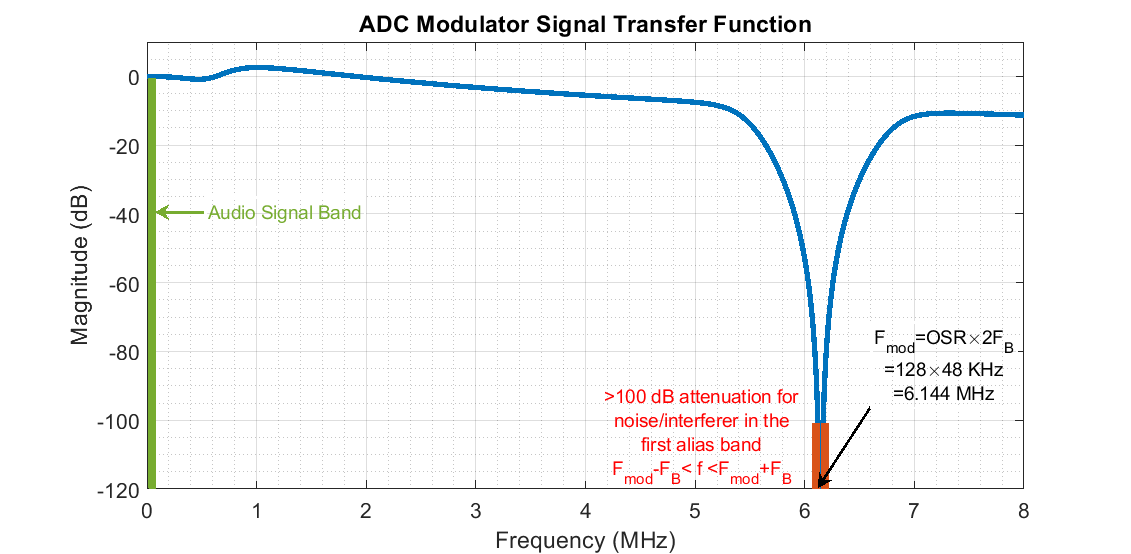

图 2-1 音频信号链方框图为了提高转换性能,TLV320ADCx140/TLV320ADCx120/PCMx120-Q1/PCMx140-Q1 不仅会对信号进行过采样来简化抗混叠滤波器设计,而且还以调制器频率 (FMOD) 的倍数在信号传递函数中添加陷波。调制器采样率与输出采样率之比被称为过采样率 (OSR)。可能混叠到带内并破坏目标信号的频带约为 N×FMOD ±20kHz(N = 1、2、3,以此类推)。调制器传递函数中的陷波会严重衰减 (> 100dB) 这些频带。图 2-2 展示了调制器的信号传递函数。对于 48kHz 的所有倍数和约数,调制器的采样频率均设为 6.144MHz。44.1kHz 系列采样率使用 5.644MHz 的调制器采样频率。信号链后方的集成式数字滤波器会在每个抽取级处切断带外噪声,从而提供超过 70dB 的阻带衰减。整体架构无需构建复杂高阶外部模拟抗混叠滤波器所需的板载运算放大器和无源器件,因此有助于降低系统成本和缩小整体解决方案尺寸。

图 2-2 ADC 调制器的信号传递函数

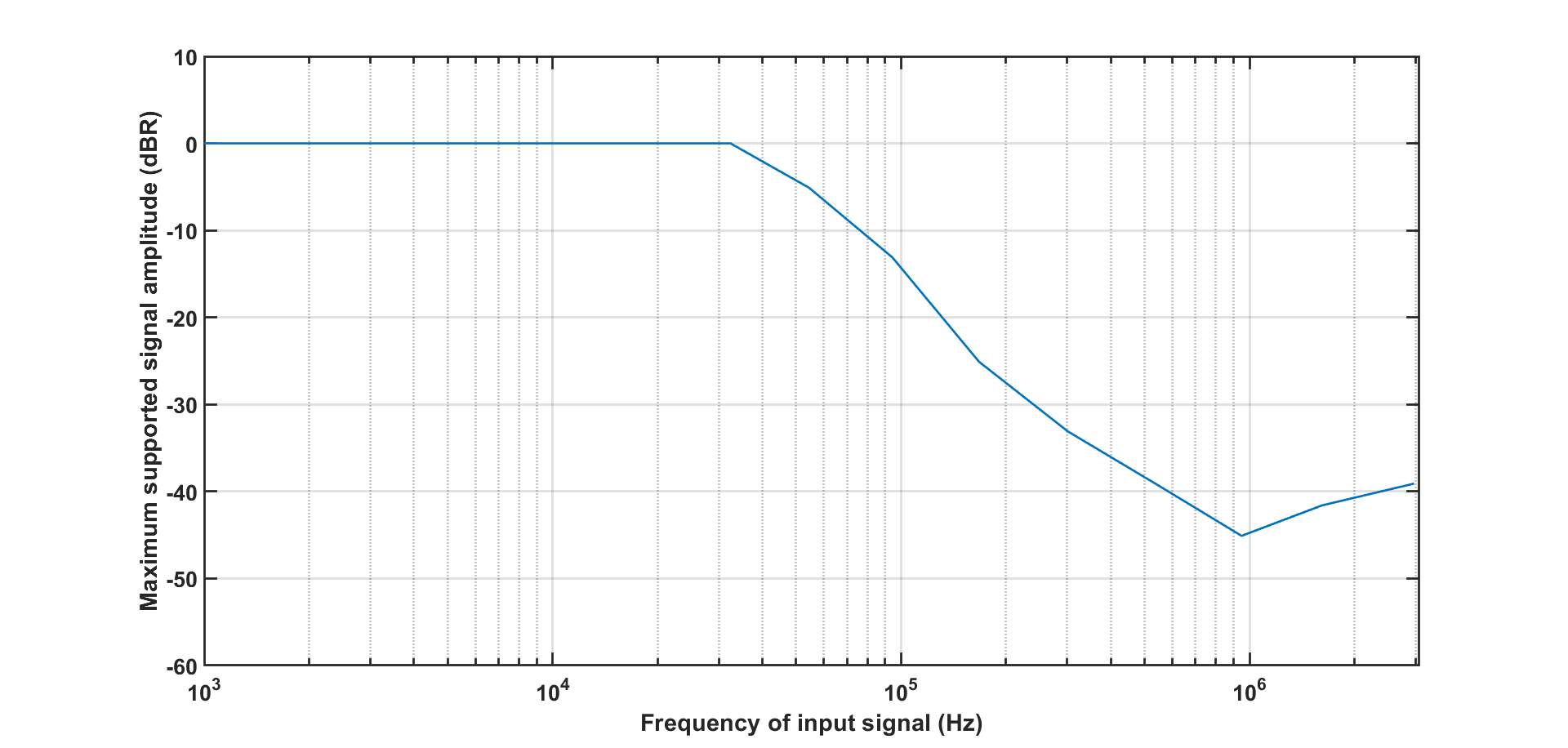

图 2-2 ADC 调制器的信号传递函数TLV320ADCx140/TLV320ADCx120/PCMx120-Q1/PCMx140-Q1 器件的信号链能够耐受输入端的噪声/干扰信号(通常无需抗混叠滤波器)。不过,该信号链无法承受超过特定限值的噪声/干扰信号。存在满量程信号时,输入端支持的最大集成噪声(整个带宽)为 0.0075V(2Vrms 时为 -48dBr)。如果不存在信号,则支持的集成噪声值为 0.01V(2Vrms 时为 -46 dBr)。请注意,这里假设此输入噪声具有等效于二阶高通传递函数的整形频谱。对于特定频率的音调(干扰/信号),图 2-3 展示了各种频率条件下都能够支持音调的振幅,而不会导致调制器饱和。

图 2-3 支持的最大信号振幅

图 2-3 支持的最大信号振幅如果存在高带外干扰信号/噪声,建议使用截止频率为 20kHz 的一阶或二阶抗混叠滤波器来抑制带外噪声/干扰信号,并防止信号链出现饱和。