ZHCAA80B December 2019 – April 2021 AFE7920 , AFE7921 , AFE7988 , AFE7989

11.1 差分信号间距

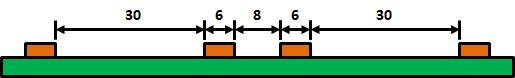

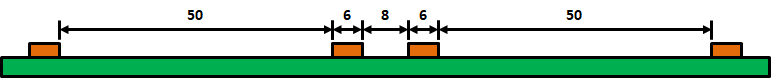

为了最大限度地减少高速接口实现时的串扰,信号对之间的间距必须至少是布线宽度的五倍。此间距称为 5W 规则。对于典型 PCB 布局,5W 规则可能过于严格,并可能不符合成本和 PCB 面积要求。因此,在某些情况下,可以接受 3W 规则(或间距是布线宽度的 3 倍)。对于计算出的布线宽度为 6mil 的 PCB 设计,高速差分对之间至少需要 30mil 的间距。此外,在布线的整段长度上要与任何其他信号保持最低 30mil 的禁止距离。如果高速差分对与时钟或周期信号相邻,要将此禁止距离增大到最低 50mil,确保适当隔离。图 11-1图 11-2有关高速差分对信号间距的示例,请参阅 和。

图 11-1 差分对与相邻的其他信号的间距

图 11-1 差分对与相邻的其他信号的间距 图 11-2 差分对与相邻的时钟或周期信号的间距

图 11-2 差分对与相邻的时钟或周期信号的间距在包含多个高速接口的器件中,要避免这些接口之间的串扰,这一点很重要。为了避免串扰,请确保在封装迂回布线之后和连接器端接之前,每个差分对未布置在另一个差分对的 30mil 范围内。